# UCC28910, UCC28911 High-Voltage Flyback Switcher with Primary-Side Regulation and Output Current Control

#### **Features**

Instruments

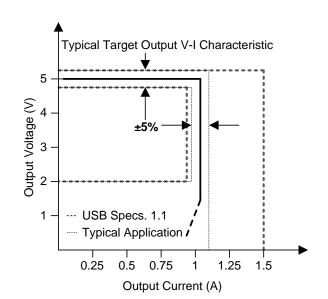

- Constant-Voltage (CV) and Constant-Current (CC) Output Regulation Without Optical-Coupler

- ±5% Output Voltage Regulation Accuracy

- ±5% Output Current Regulation With AC Line and Primary Inductance Tolerance Compensation

- 700-V Start-Up and Smart Power Management Enables <30-mW Standby Power

- 115-kHz Maximum Switching Frequency Design for High-Power Density

- Valley Switching and Frequency Dithering to Ease **EMI** Compliance

- Thermal Shut Down

- Low Line and Output Over-Voltage Protection

# **Applications**

- Home and Building Automation

- **Power Metering Bias**

- Bias Power for Smoke Alarm, Fire Alarm and Thermostat

- Wall Adapters, Chargers for Mobile Phones

- Smart plug, IoT, MCU and WiFi Power

- Aux power for TV, Server, White Goods

- **LED Lighting**

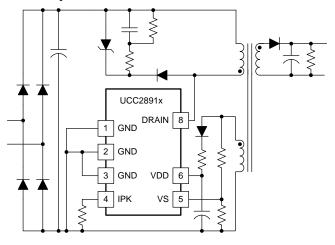

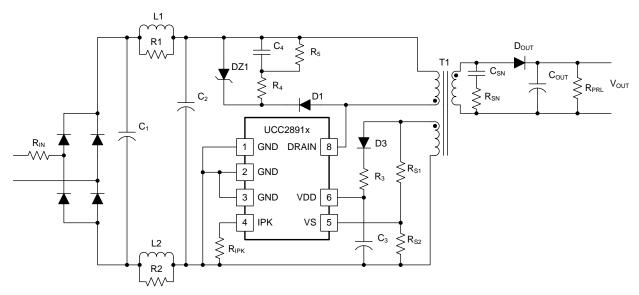

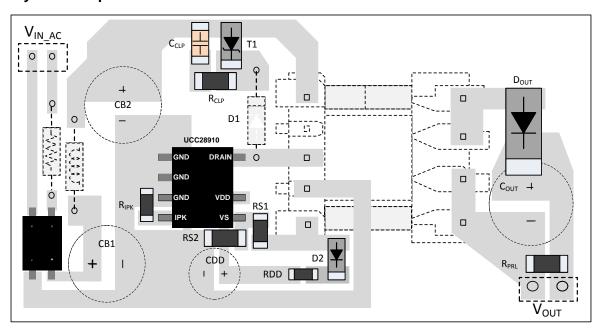

# Simplified Schematic

# 3 Description

The UCC28910 and UCC28911 are high-voltage flyback switchers that provide output voltage and current regulation without the use of an optical coupler. Both devices incorporate a 700-V power FET and a controller that process operating information from the flyback auxiliary winding and power FET to provide a precise output voltage and current control. The integrated high-voltage current source for startup that is switched off during device operation, and the controller current consumption is dynamically adjusted with load. Both enable the very low stand-by power consumption.

Control algorithms in the UCC28910 and UCC28911, combining switching frequency and peak primary current modulation, allow operating efficiencies to meet or exceed applicable standards. Discontinuous conduction mode (DCM) with valley switching is used to reduce switching losses. Built-in protection features help to keep secondary and primary component stress levels in check across the operating range. The frequency jitter helps to reduce EMI filter cost.

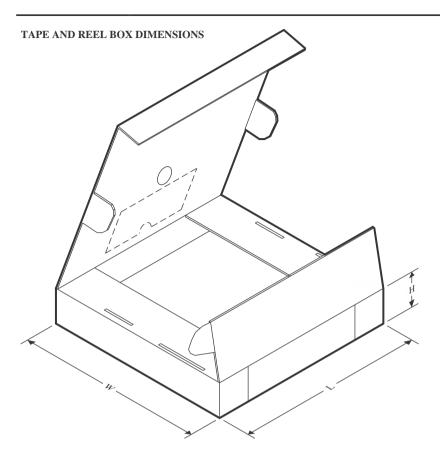

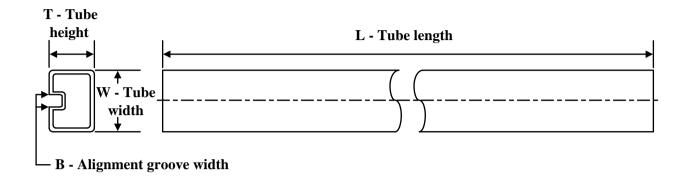

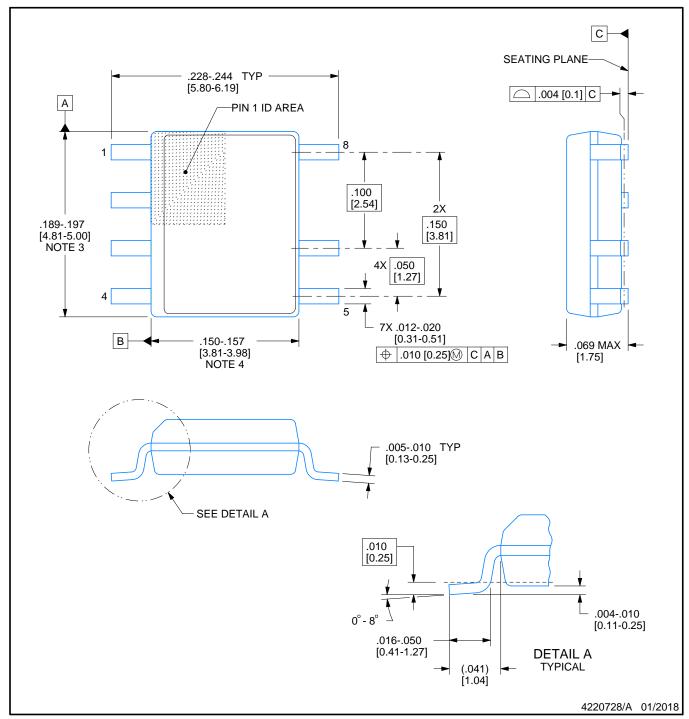

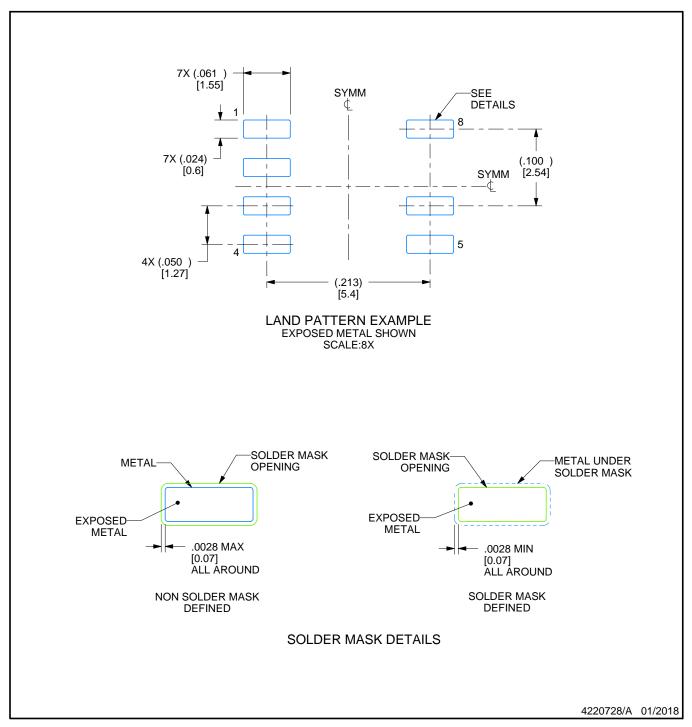

#### **Device Information**

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| UCC28910    | SOIC-7 (7) | 5.00 mm x 6.20 mm |

| UCC28911    | SOIC-7 (7) | 5.00 mm x 6.20 mm |

| T: | aŀ | ٦la | 9 ( | ٦ſ | F ( | $\Box$ | n | n | t | ar | ١ts |

|----|----|-----|-----|----|-----|--------|---|---|---|----|-----|

|    | αк | ,,, |     | _  |     | _      | _ |   | Ľ | _  |     |

| 1 | Features 1                           |    | 9.1 Overview                         | 14 |

|---|--------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                       |    | 9.2 Functional Block Diagram         | 15 |

| 3 | Description 1                        |    | 9.3 Feature Description              | 16 |

| 4 | Simplified Schematic                 |    | 9.4 Device Functional Modes          | 27 |

| 5 | Revision History2                    | 10 | Applications and Implementation      | 28 |

| 6 | Device Comparison Table              |    | 10.1 Application Information         | 28 |

| - | -                                    |    | 10.2 Typical Application             | 28 |

| 7 | Pin Configuration and Functions      | 11 | Power Supply Recommendations         | 44 |

| 8 | 7.1 Detailed Pin Description         | 12 | Layout                               |    |

| 0 | Specifications                       |    | 12.1 Layout Guidelines               | 44 |

|   | 8.1 Absolute Maximum Ratings         |    | 12.2 Layout Example                  |    |

|   | 8.2 Storage Conditions               | 13 | Device and Documentation Support     |    |

|   | 8.3 ESD Ratings                      |    | 13.1 Documentation Support           |    |

|   | 8.4 Recommended Operating Conditions |    | 13.2 Trademarks                      |    |

|   | 8.5 Thermal Information              |    | 13.3 Electrostatic Discharge Caution |    |

|   | 8.6 Electrical Characteristics       |    | 13.4 Glossary                        |    |

|   | 8.7 Switching Characteristics        |    | 13.5 Related Links                   |    |

|   | 8.8 Typical Characteristics          | 14 | Mechanical, Packaging, and Orderable |    |

| 9 | Detailed Description 14              | 14 | Information                          | 47 |

|   |                                      |    |                                      |    |

# 5 Revision History

| CI | hanges from Revision C (March 2015) to Revision D           | Page |

|----|-------------------------------------------------------------|------|

| •  | Deleted minimum Wait supply current specification           | 8    |

| •  | Deleted minimum Quiescent wait supply current specification |      |

| •  | Added EMI Dithering section                                 | 20   |

| •  | Corrected typographical error in Equation 7                 | 33   |

|    |                                                             |      |

| C | hanges from Revision August 2014 (B) to Revision C                             | Page |

|---|--------------------------------------------------------------------------------|------|

| • | Added UCC28911 device                                                          | 1    |

| • | Changed Simplified Schematic diagram                                           | 1    |

| • | Added UCC28911 specifications throughout.                                      | 7    |

| • | Changed Typical Characteristics                                                | 11   |

| • | Changed Figure 28                                                              | 23   |

| • | Changed Figure 29.                                                             | 23   |

| • | Changed Applications and Implementation section to include the UCC28911 device | 28   |

| Changes from Revision A (July 2013) to Revision B |                                      |  |  |

|---------------------------------------------------|--------------------------------------|--|--|

| •                                                 | Changed Simplified Schematic diagram |  |  |

# Changes from Original (July 2013) to Revision A Page

# 6 Device Comparison Table

| DEVICE NUMBER <sup>(1)</sup> | 175 V <sub>AC</sub> to 265 V <sub>AC</sub> |                           | 90 V <sub>AC</sub> to  | UNITS                     |       |

|------------------------------|--------------------------------------------|---------------------------|------------------------|---------------------------|-------|

| DEVICE NUMBER                | Adapter <sup>(2)</sup>                     | Open Frame <sup>(3)</sup> | Adapter <sup>(2)</sup> | Open Frame <sup>(3)</sup> | UNITS |

| UCC28910                     | 6.5                                        | 9.5                       | 6                      | 7.5                       | W     |

| UCC28911                     | 8                                          | 12                        | 7.5                    | 10                        | W     |

- (1) Obtained considering 125°C as maximum junction temperature. For lower operating maximum junction temperature maximum output power should be lower.

- Typical continuous power in enclosed adapter at 50°C ambient, with adequate copper area ( > 560 mm²) connected on GND pin to have 90°C/W as junction to ambient thermal resistance.

- (3) Maximum continuous power with open frame design at 50°C ambient, with adequate copper area connected on GND pin and /or adequate air flow to have 50°C/W as junction to ambient thermal resistance.

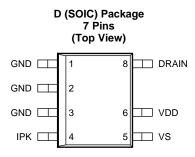

# 7 Pin Configuration and Functions

#### Pin Functions

| PIN   |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                               |

|-------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | 1/0\               | DESCRIPTION                                                                                                                                                                                                                                                               |

| DRAIN | 8   | Р                  | DRAIN, the drain of the internal power FET, but also the input for the high-voltage current source used to start up the device.                                                                                                                                           |

|       | 1 2 |                    | The ground pins (GND) are both the reference pins for the controller and the low-side return for the drive                                                                                                                                                                |

| GND   |     | G                  | output. Special care should be taken to return all AC decoupling as close as possible to this pin and                                                                                                                                                                     |

|       | 3   |                    | avoid any common trace length with analog signal return paths.                                                                                                                                                                                                            |

| IPK   | 4   | 0                  | IPK is used to set the maximum peak current flowing in the power FET that is proportional to the maximum output current.                                                                                                                                                  |

| N/A   | 7   | N/A                | This pin is not present to provide enough distance between high voltage pin (DRAIN) and VDD pins.                                                                                                                                                                         |

| VDD   | 6   | Р                  | VDD is the supply pin to the controller. A carefully placed bypass capacitor to GND is required on this pin.                                                                                                                                                              |

| VS    | 5   | I                  | Voltage Sense (VS) is used to provide voltage and timing feedback to the controller. Normally this pin is connected to a voltage divider between an auxiliary winding and ground. The value of the upper resistor of this divider is used to program low line thresholds. |

(1) P = Supply, G = Ground, I = Input, O = output

# 7.1 Detailed Pin Description

# 7.1.1 VDD (Device Voltage Supply)

The VDD pin is connected to a bypass capacitor to ground and typically to a rectifier diode connected to the auxiliary winding. The VDD turn on UVLO threshold is 9.5 V (VDD<sub>ON</sub> typical) and turn off UVLO threshold is 6.5 V (VDD<sub>OFF</sub> typical). The pin is provided with an internal clamp that prevents the voltage from exceeding the absolute maximum rating of the pin. The internal clamp cannot absorb currents higher than 10 mA (see  $I_{VDD(clp)}$  in Absolute Maximum Ratings). To avoid damaging the device, when the clamp flowing current exceeds 6 mA ( $I_{DDCLP\_OC}$  typical) the device stops switching. The VDD pin operating range is then from 7 V (VDD<sub>OFF</sub> maximum) up to 26 V (VDD<sub>CLAMP</sub> minimum). The USB charging specification requires that the output current operates in constant current mode from 5 V to a minimum of 2 V; this is easily achieved with a nominal VDD of approximately 17 V. Set  $N_{AS}$  (auxiliary-to-secondary windings turn ratio) to 17 V / ( $V_{OUT} + V_{F}$ ) where  $V_{F}$  is the voltage drop on the output diode at low current. The additional VDD headroom up to the clamp allows for VDD to rise due to the leakage energy delivered to the VDD in high-load conditions.

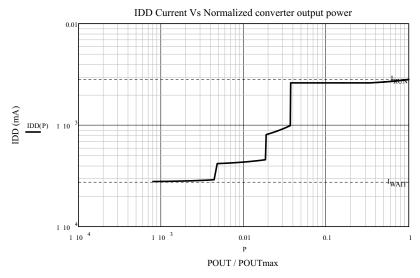

The current consumption of the device depends upon the operating condition. The graph below shows the current consumption as a function of normalized converter output power.

Figure 1. VDD Current Consumption

#### **7.1.2 GND (Ground)**

The device is provided with three pins, shorted together, that are used as external ground reference to the controller for analog signal reference. The three pins also function to pull out the heat caused by the power dissipation of the internal power FET. Place the VDD bypass capacitor close to GND and VDD with short traces to minimize noise on the VS and IPK signal pins.

# **Detailed Pin Description (continued)**

#### 7.1.3 VS (Voltage Sense)

The VS pin is connected to a resistor divider from the auxiliary winding to ground. The VS input provides three functions.

- 1. It provides output voltage information to the voltage control Loop. The output voltage feedback information is sampled at the end of the transformer secondary current demagnetization time to provide an accurate representation of the output voltage.

- 2. It also provides timing information to achieve valley switching and the duty cycle of the secondary transformer current is determined by the waveform on the VS pin.

- 3. It samples the bulk capacitor input voltage providing under-voltage shutdown.

The data provided in 1. and 2. are sensed during the MOSFET off-time; 3. is performed during the MOSFET on-time when the auxiliary-winding voltage is negative.

Connected between VS pin and the auxiliary winding there is the resistance  $R_{S1}$ . During MOSFET on-time the auxiliary voltage is negative and proportional to the converter input voltage. The voltage on VS pin is clamped to GND and through the resistance  $R_{S1}$ . During the on-time, the current sourced from the VS pin, proportional to converter input voltage and inversely proportional to resistance  $R_{S1}$ , is sensed by the device. For the undervoltage function, the enable threshold on VS current is 210  $\mu$ A and the disable threshold is 75  $\mu$ A.

The resistor values for  $R_{S1}$  and  $R_{S2}$  can be determined by the equations below.

$$R_{S1} = \frac{V_{RMS\_EN} \times \sqrt{2}}{N_{PA} \times I_{VSI\_RUN}}$$

#### where

- N<sub>PA</sub> is the transformer primary to auxiliary turns ratio,

- V<sub>RMS EN</sub> is the AC RMS voltage to enable turn on of the controller,

$$R_{S2} = \frac{V_{VSR} \times R_{S1} \times N_{PA}}{(V_{OUT} + V_F) \times N_{PS} - (V_{VSR} \times N_{PA})}$$

#### where

- V<sub>OUT</sub> is the converter output voltage in V,

- V<sub>F</sub> is the output rectifier forward drop at low current in V,

- N<sub>PS</sub> is the transformer primary to secondary turns ratio R<sub>S1</sub> is the VS divider high side resistance in Ohms,

- V<sub>VSR</sub> is the regulating level of VS pin.

(1)

# **Detailed Pin Description (continued)**

#### 7.1.4 IPK (Set the Maximum DRAIN Current Peak)

A resistance ( $R_{IPK}$ ) connected between IPK pin and GND sets the maximum value of the power FET peak current,  $I_{D\_PK(max)}$ . A current,  $I_{SENSE}$ , proportional to the power FET current, comes out from the IPK pin during power FET on time. The voltage across  $R_{IPK}$  is fed to the PWM comparator and establish to switch off the power FET according to the following equation:

$$I_{D\_PK(max)} = \frac{V_{CSTE(max)}}{R_{IPK}}$$

where

• V<sub>CSTE(max)</sub> is the equivalent current sense threshold (see Electrical Characteristics table). (3)

If the IPK pin is shorted to GND (RIPK = 0), the peak current is automatically set to  $I_{D\_PEAK(max)}$ , 600 mA for UCC28910, or 700 mA for UCC28911.

A test is performed at device start up to check whether the IPK pin is shorted to GND or the  $R_{IPK}$  is present. If  $R_{IPK}$  is less than  $R_{IPK\_SHORT}$  (maximum), the device interprets it as a short ( $R_{IPK} = 0$ ) and the DRAIN peak current is set to  $I_{D\_PEAK(max)}$ . Otherwise, if  $R_{IPK}$  is greater than  $R_{IPK(min)}$  (minimum), the device sets the peak current DRAIN according to the previous equation. A value of  $R_{IPK}$  that is in between the before said values is not allowed since the value of the peak current may be selected using either of the two sense resistances: the internal sense resistance and  $R_{IPK}$ .

#### **7.1.5 DRAIN**

The DRAIN pin is connected to the DRAIN of the internal power FET. This pin also provides current to the high voltage current source at start up.

# 8 Specifications

# 8.1 Absolute Maximum Ratings

(unless otherwise noted) (1)(2)

|                       |                                                              | MIN                                  | MAX                                  | UNIT |

|-----------------------|--------------------------------------------------------------|--------------------------------------|--------------------------------------|------|

| V <sub>DRAIN</sub>    | DRAIN voltage                                                | Internally<br>limited <sup>(3)</sup> | 700                                  | V    |

| I <sub>DRAIN</sub>    | Negative drain current                                       | -100                                 |                                      | mA   |

| $V_{DD}$              | Supply voltage                                               |                                      | Internally<br>limited <sup>(3)</sup> | V    |

| I <sub>VDD(clp)</sub> | Maximum VDD clamp current                                    |                                      | 10                                   | mA   |

| V <sub>VS</sub>       | Voltage range                                                | Internally<br>limited <sup>(3)</sup> | 7                                    | V    |

| V <sub>IPK</sub>      | Voltage range                                                | -0.5                                 | 5.0                                  | V    |

| I <sub>VS</sub>       | Peak VS pin current (current out of the pin)                 | -1.2                                 |                                      | mA   |

|                       | Pulsed drain current <sup>(4)</sup> , UCC28910               |                                      | 950                                  | mA   |

| IDRAIN                | Pulsed drain current <sup>(4)</sup> , UCC28911               |                                      | 1200                                 | mA   |

| T <sub>LEAD</sub>     | Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                                      | 260                                  | °C   |

| T <sub>J</sub>        | Operating junction temperature range                         | -55                                  | 150                                  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 8.2 Storage Conditions

|                  |                     | MIN | MAX | UNIT |

|------------------|---------------------|-----|-----|------|

| T <sub>stg</sub> | Storage temperature | -65 | 150 | °C   |

#### 8.3 ESD Ratings

|                    |                                                        |                                                                                | VALUE | UNIT |

|--------------------|--------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000                                                                          |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 8.4 Recommended Operating Conditions (1)(2)

|                          |                                          |          | MIN                | NOM | MAX            | UNIT |

|--------------------------|------------------------------------------|----------|--------------------|-----|----------------|------|

| $V_{VDD}$                | Voltage on VDD terminal during operation |          | VDD <sub>OFF</sub> |     | $V_{VDD(clp)}$ | V    |

| I <sub>VS</sub>          | Current out of the terminal              |          |                    |     | 1              | mA   |

| I <sub>D(peak_max)</sub> | Mariana daria and annua                  | UCC28910 |                    | 600 |                | mA   |

|                          | Maximum drain peak current               | UCC28911 |                    | 700 |                | mA   |

| TJ                       | Operating junction temperature           |          | -40                |     | 125            | °C   |

<sup>(1)</sup> Unless otherwise noted, all voltages are with respect to GND.

<sup>(2)</sup> All voltages are with respect to GND. Currents are positive into, negative out of the specified pin. These ratings apply over the operating ambient temperature ranges unless otherwise noted.

<sup>(3)</sup> Do not drive with low impedance voltage source.

<sup>(4)</sup> Maximum pulse width =  $100 \mu s$ .

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> In case of thermal shut down, if TA > 100°C, the device does not restart because of the T<sub>J(hys)</sub> Electrical Characteristics.

#### 8.5 Thermal Information

|                   |                                              | UCC28910   | UCC28911   |       |

|-------------------|----------------------------------------------|------------|------------|-------|

|                   | THERMAL METRIC <sup>(1)</sup>                | D          | D          | UNITS |

|                   |                                              | 7 Pin SOIC | 7 Pin SOIC |       |

| $\theta_{JA}$     | Junction-to-ambient thermal resistance       | 102.2      | 102.2      |       |

| $\theta_{JCtop}$  | Junction-to-case (top) thermal resistance    | 39.1       | 39.1       |       |

| $\theta_{\sf JB}$ | Junction-to-board thermal resistance         | 54.7       | 54.7       | °C/W  |

| ΨЈТ               | Junction-to-top characterization parameter   | 5.4        | 5.4        |       |

| ΨЈВ               | Junction-to-board characterization parameter | 54.7       | 54.7       |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 8.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted),  $V_{VDD} = 15 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $125 ^{\circ}\text{C}$ ,  $T_A = T_J$

|                       | PARAMETER                               | TEST CONDI                                                                                         | TIONS    | MIN    | TYP  | MAX   | UNIT |

|-----------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------|----------|--------|------|-------|------|

| SUPPLY INF            | PUT                                     |                                                                                                    |          |        |      | 1     |      |

|                       | 0 1                                     | $V_{VS} = 3.9 \text{ V}, f_{SW} = f_{SW(max)}$                                                     | UCC28910 | 2.3    | 2.9  | 3.4   | mA   |

| I <sub>RUN</sub>      | Supply current, run                     | $V_{VS} = 3.75 \text{ V}, f_{SW} = f_{SW(max)}$                                                    | UCC28911 | 2.3    | 2.9  | 3.4   | mA   |

| I <sub>RUNQ</sub>     | Outroped supply supply                  | $V_{VS} = 3.9 \text{ V}, f_{SW} = 0 \text{ Hz}$                                                    | UCC28910 | 1.90   | 2.35 | 2.80  | mA   |

|                       | Quiescent supply current                | $V_{VS} = 3.75 \text{ V}, f_{SW} = f_{SW(max)}$                                                    | UCC28911 | 1.90   | 2.35 | 2.80  | mA   |

|                       | Moit aunaly aurrent                     | $V_{VS} = 4.1 \text{ V}, f_{SW} = f_{SW(min)},$                                                    | UCC28910 | ·      | 270  | 370   | μΑ   |

| I <sub>WAIT</sub>     | Wait supply current                     | T <sub>J</sub> = 25°C                                                                              | UCC28911 |        | 250  | 330   | μA   |

|                       | Quiescent wait supply                   | $V_{VS} = 4.1 \text{ V}, f_{SW} = 0 \text{ Hz},$                                                   | UCC28910 |        | 200  | 280   | μΑ   |

| I <sub>WAITQ</sub>    | current                                 | T <sub>J</sub> = 25°C                                                                              | UCC28911 | ·      | 190  | 240   | μA   |

| I <sub>START</sub>    | Supply current before start             | $0 \text{ V} \le \text{V}_{\text{VDD}} \le 5.6 \text{ V},$ $\text{V}_{\text{DRAIN}} = 0 \text{ V}$ | UCC28910 |        | 65   | 90    | μΑ   |

|                       |                                         | 0 V ≤ V <sub>VDD</sub> ≤ 5.6 V,<br>V <sub>DRAIN</sub> = 0 V, T <sub>J</sub> = 25°C                 | UCC28911 |        | 65   | 80    | μΑ   |

|                       | Supply current after fault              | f <sub>SW</sub> = 0 Hz                                                                             | UCC28910 | ·      | 190  | 260   | μA   |

| I <sub>FAULT</sub>    |                                         | f <sub>SW</sub> = 0 Hz, T <sub>J</sub> = 25°C                                                      | UCC28911 |        | 190  | 240   | μΑ   |

| UNDER-VOL             | TAGE LOCKOUT                            |                                                                                                    |          | ·      |      |       |      |

| VDD <sub>ON</sub>     | VDD turn-on threshold                   | V <sub>VDD</sub> low to high                                                                       |          | 9.0    | 9.5  | 10.0  | V    |

| VDD <sub>OFF</sub>    | VDD turn-off threshold                  | V <sub>VDD</sub> high to low                                                                       |          | 6.0    | 6.5  | 7.0   | V    |

| VDD <sub>HV(on)</sub> | HV current source start                 | V <sub>VDD</sub> high to low                                                                       |          | 4.8    | 5.2  | 5.6   | V    |

| $\Delta V_{UVLO}$     | UVLO hysteresis                         | VDD <sub>ON</sub> – VDD <sub>OFF</sub>                                                             |          | 2.8    | 3.0  | 3.2   | V    |

| STARTUP C             | URRENT SOURCE                           |                                                                                                    |          | ·      |      |       |      |

| I <sub>CH1</sub>      | Startup current with VDD shorted to GND | V <sub>VDD</sub> < 250 mV, V <sub>DRAIN</sub> = 100 V                                              |          | -300   |      | -100  | μΑ   |

| I <sub>CH2</sub>      | Sourced current for startup at high VDD | V <sub>VDD</sub> = 8 V, V <sub>DRAIN</sub> = 100 V                                                 |          | -9.75  |      | -0.40 | mA   |

| I <sub>CH3</sub>      | Sourced current for startup at low VDD  | V <sub>VDD</sub> = 2 V, V <sub>DRAIN</sub> = 100 V                                                 |          | -13.75 |      | -1.30 | mA   |

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted),  $V_{VDD}$  = 15 V,  $T_A$  = -40°C to 125°C,  $T_A$  =  $T_J$

|                         | PARAMETER                         | TEST CONDI                                                                                | ITIONS |          | MIN   | TYP  | MAX  | UNIT |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|--------|----------|-------|------|------|------|

| VS INPUT                |                                   |                                                                                           |        | <u>'</u> |       |      |      |      |

| V <sub>VSR</sub>        | Regulating level                  | Measured in no load condition,<br>$T_J = 25^{\circ}C$                                     |        |          | 4.01  | 4.05 | 4.09 | V    |

| V <sub>VSNC</sub>       | Negative clamp level              | $I_{VS} = -300 \ \mu A$                                                                   |        |          | -190  | -250 | -325 | mV   |

| I <sub>VS</sub>         | Input bias current                | V <sub>VS</sub> = 4 V                                                                     |        |          | -0.25 | 0.00 | 0.25 | μΑ   |

| PROTECTION              | N                                 |                                                                                           |        |          |       |      |      |      |

|                         | DDAIN aven avenant                | I win about of to CND                                                                     |        | UCC28910 | 725   | 850  | 925  | mA   |

| I <sub>D(ocp)</sub>     | DRAIN over current                | I <sub>PK</sub> pin shorted to GND                                                        |        | UCC28911 | 880   | 980  | 1090 | mA   |

| V <sub>CSTE_OCP</sub>   | Equivalent V <sub>CST(OCP),</sub> | V <sub>VS</sub> = 3.9 V                                                                   |        | UCC28910 | 670   | 770  | 830  | V    |

|                         | $I_{D(ocp)} \times R_{IPK}$       | V <sub>VS</sub> = 3.75 V                                                                  |        | UCC28911 | 800   | 885  | 975  | V    |

| V                       | Equivalent V <sub>CST(OCP2)</sub> | V <sub>VS</sub> = 3.9 V                                                                   |        | UCC28910 | ·     | 1200 |      | V    |

| V <sub>CSTE_OCP2</sub>  | $I_{D(ocp2)} \times R_{IPK}$      | V <sub>VS</sub> = 3.75 V                                                                  |        | UCC28911 |       | 1400 |      | V    |

|                         | Maximum FET on time at            | $V_{VS}$ < 3.9 V, $I_{PK}$ shorted to GND                                                 |        | UCC28910 | 13    | 18   | 24   | μs   |

| tONMAX(max)             | high load                         | $V_{VS}$ = 3.75 V, $I_{PK}$ shorted to GND                                                |        | UCC28911 | 13    | 18   | 24   | μs   |

| t <sub>ONMAX(min)</sub> | Maximum FET on time at low load   | $V_{VS}$ > 4.1 V, $I_{PK}$ shorted to GND                                                 |        | UCC28910 | 4.3   | 6    | 10   | μs   |

|                         |                                   | $V_{VS}$ = 4.35 V, $I_{PK}$ shorted to GND                                                |        | UCC28911 | 4.3   | 6    | 10   | μs   |

| V <sub>OVP</sub>        | Over-voltage threshold            | At VS input, T <sub>J</sub> = 25°C                                                        |        |          | 4.45  | 4.60 | 4.75 | V    |

| I <sub>VSL(run)</sub>   | VS line sense run current         | Current out of VS pin - increa                                                            | sing   |          | 175   | 215  | 260  | μΑ   |

| I <sub>VSL(stop)</sub>  | VS line sense stop current        | Current out of VS pin - decrea                                                            | asing  |          | 60    | 75   | 100  | μΑ   |

| K <sub>VSL</sub>        | Line sense I <sub>VS</sub> ratio  | I <sub>VSL(run)</sub> / I <sub>VSL(stop)</sub>                                            |        |          | 2.55  | 2.70 | 2.90 | A/A  |

| VDD <sub>CLP</sub>      | VDD voltage clamp                 | I <sub>VDDCLP</sub> forced = 2 mA                                                         |        |          | 26    | 28   | 30   | V    |

| I <sub>VDDCLP_OC</sub>  | VDD clamp over current            | V <sub>VDD</sub> > 25 V                                                                   |        |          | 4.65  | 6.00 | 7.65 | mA   |

| T <sub>J(stop)</sub>    | Thermal shutdown temperature      | Internal junction temperature                                                             |        |          |       | 150  |      | °C   |

| T <sub>J(hys)</sub>     | Thermal shutdown hysteresis       | Internal junction temperature                                                             |        |          |       | 50   |      | °C   |

| POWER FET               |                                   |                                                                                           |        | ·        |       |      | ·    |      |

| BV <sub>DSS</sub>       | Break-down voltage                | $T_J = 25$ °C                                                                             |        |          | 700   |      |      | V    |

|                         |                                   | 1 450 m A T 25%C                                                                          |        | UCC28910 |       | 10.5 | 12.0 | Ω    |

| D                       | Power EET on registence           | $I_D = 150 \text{ mA}, T_J = 25^{\circ}\text{C}$                                          |        | UCC28911 |       | 6.25 | 7.2  | Ω    |

| R <sub>DS(on)</sub>     | Power FET on resistance           | I = 150 mA T = 125°C                                                                      |        | UCC28910 |       | 18.4 | 21.5 | Ω    |

|                         |                                   | I <sub>D</sub> = 150 mA, T <sub>J</sub> = 125°C                                           |        | UCC28911 |       | 11.4 | 13.4 | Ω    |

|                         |                                   | $V_{DS} = 400 \text{ V HV}, \text{ VS} = 4.2 \text{ V I}$<br>$T_{J} = 25^{\circ}\text{C}$ | oc     |          |       |      | 10   | μΑ   |

| I <sub>LEAKAGE</sub>    | DRAIN pin leakage current         | V <sub>DS</sub> = 400 V HV, VS = 4.2 V [<br>T <sub>J</sub> = 125°C                        | OC .   |          |       |      | 20   | μΑ   |

|                         |                                   | V <sub>DS</sub> = 700 V HV, VS = 4.2 V [<br>T <sub>J</sub> = 25°C                         | DC     |          |       |      | 10   | μΑ   |

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted),  $V_{VDD}$  = 15 V,  $T_A$  = -40°C to 125°C,  $T_A$  =  $T_J$

|                        | PARAMETER                                                           | TEST CONDITIONS                                    |          | MIN  | TYP   | MAX  | UNIT |

|------------------------|---------------------------------------------------------------------|----------------------------------------------------|----------|------|-------|------|------|

| CURRENTS               |                                                                     |                                                    |          | ·    |       |      |      |

|                        | Maximum DRAIN peak                                                  | IPK pin shorted to GND, T <sub>J</sub> =           | UCC28910 | 582  | 600   | 618  | mA   |

| ID_PEAK(max)           | current                                                             | 25°C                                               | UCC28911 | 680  | 700   | 720  | mA   |

| R <sub>IPK_SHORT</sub> | IPK to GND resistance Max to assume IPK shorted to GND              |                                                    |          |      |       | 200  | Ω    |

| R <sub>IPK(min)</sub>  | IPK to GND minimum resistance                                       |                                                    |          | 900  |       |      | Ω    |

| V <sub>CSTE(max)</sub> | Equivalent current sense threshold, $I_{D\_PK(max)} \times R_{IPK}$ | V <sub>VS</sub> = 3.9 V, T <sub>J</sub> = 25°C     | UCC28910 | 532  | 540   | 548  | V    |

|                        |                                                                     | V <sub>VS</sub> = 3.75 V                           | UCC28911 | 620  | 630   | 640  | V    |

| V                      | Equivalent current sense threshold, $I_{D\_PK(min)} \times R_{IPK}$ | V <sub>VS</sub> = 4.1 V                            | UCC28910 | 160  | 180   | 200  | V    |

| V <sub>CSTE(min)</sub> |                                                                     | V <sub>VS</sub> = 4.35 V                           | UCC28911 | 170  | 216   | 265  | V    |

| K <sub>AM</sub>        | AM control ratio                                                    | V <sub>CSE(max)</sub> / V <sub>CSE(min)</sub>      |          | 2.30 | 3.00  | 3.50 | V/V  |

| V                      | CC regulation gain, t <sub>DEMAG</sub> ×                            | V <sub>VS</sub> < 3.9 V                            | UCC28910 |      | 0.413 |      |      |

| K <sub>CC</sub>        | f <sub>SW</sub>                                                     | V <sub>VS</sub> = 3.75 V                           | UCC28911 |      | 0.413 |      |      |

| \/                     | CC regulation constant,                                             | V 20 V T 250C                                      | UCC28910 | 216  | 223   | 230  | V    |

| $V_{CCR}$              | $V_{CSET(max)} \times K_{CC}$                                       | $V_{VS} < 3.9 \text{ V}, T_J = 25^{\circ}\text{C}$ | UCC28911 | 250  | 260   | 270  | V    |

# 8.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER             |                             | TEST CONDITIONS           |          | MIN  | TYP  | MAX  | UNIT |

|-----------------------|-----------------------------|---------------------------|----------|------|------|------|------|

| TIMING                |                             |                           | ·        |      |      | ·    |      |

|                       | Maximum switching           | V <sub>VS</sub> < 3.9 V   | UCC28910 | 105  | 115  | 125  | kHz  |

| f <sub>SW(max)</sub>  | frequency                   | V <sub>VS</sub> = 3.75 V  | UCC28911 | 105  | 115  | 125  | kHz  |

| f <sub>SW(min)</sub>  | Minimum switching frequency | V <sub>VS</sub> > 4.1 V   | UCC28910 | 360  | 420  | 490  | Hz   |

|                       |                             | V <sub>VS</sub> = 4.35 V  | UCC28911 | 360  | 420  | 500  | Hz   |

| t <sub>ZTO</sub> Zero | 7                           | V <sub>VS</sub> < 3.9 V   | UCC28910 | 1.80 | 2.10 | 2.65 | μs   |

|                       | Zero crossing timeout delay | V <sub>VS</sub> = 4.35 V  | UCC28911 | 1.80 | 2.10 | 2.75 | μs   |

| t <sub>ON(min)</sub>  | Minimum on time             | 1 0.05 V                  | UCC28910 |      | 390  |      | ns   |

|                       |                             | $I_{PK} = 0.85 \text{ V}$ | UCC28911 |      | 420  |      | ns   |

# 8.8 Typical Characteristics

Unless otherwise specified,  $V_{VDD}$  = 15 V,  $T_A$  = -40°C to 125°C,  $T_A$  =  $T_J$

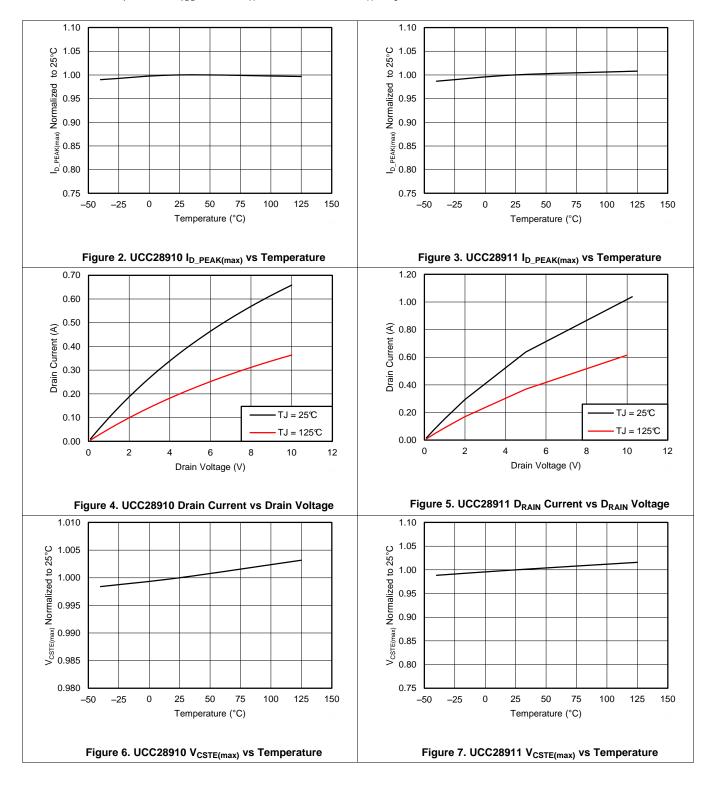

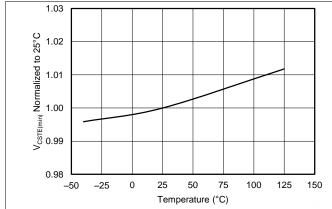

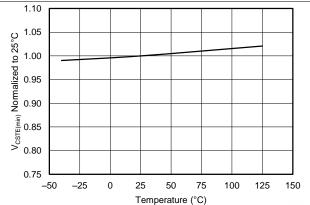

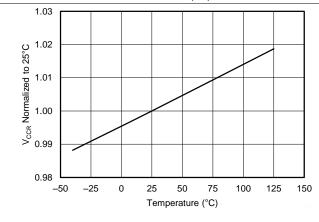

# **Typical Characteristics (continued)**

Unless otherwise specified,  $V_{VDD}$  = 15 V,  $T_A$  = -40°C to 125°C,  $T_A$  =  $T_J$

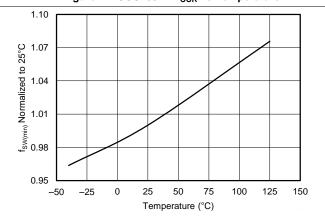

Figure 8. UCC28910  $V_{CSTE(min)}$  vs Temperature

Figure 9. UCC28911 V<sub>CSTE(min)</sub> vs Temperature

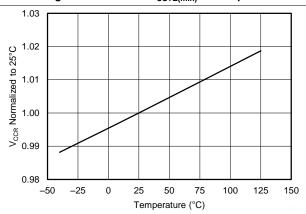

Figure 10. UCC28910 V<sub>CCR</sub> vs Temperature

Figure 11. UCC28911 V<sub>CCR</sub> vs Temperature

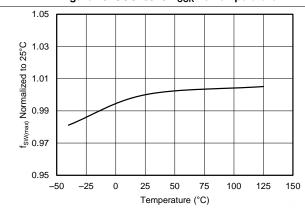

Figure 12.  $f_{SW(max)}$  vs Temperature

Figure 13.  $f_{SW(min)}$  vs Temperature

# **Typical Characteristics (continued)**

Unless otherwise specified,  $V_{VDD}$  = 15 V,  $T_A$  = -40°C to 125°C,  $T_A$  =  $T_J$

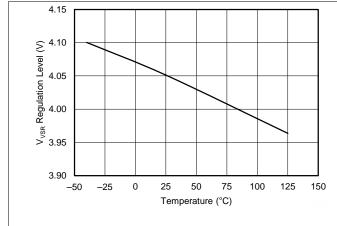

Figure 14. V<sub>VSR</sub> vs Temperature

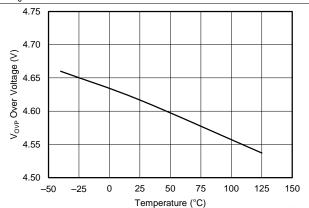

Figure 15. V<sub>OVP</sub> vs Temperature

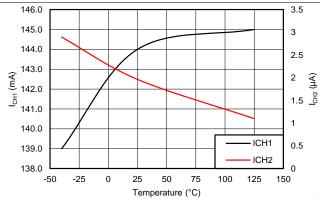

Figure 16. I<sub>CH1</sub> and I<sub>CH2</sub> vs Temperature

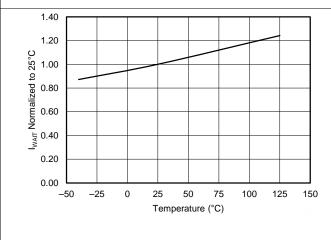

Figure 18.  $I_{WAIT}$  vs Temperature

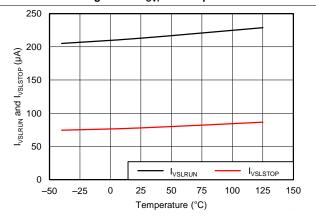

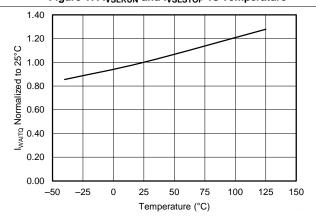

Figure 17. I<sub>VSLRUN</sub> and I<sub>VSLSTOP</sub> vs Temperature

Figure 19. I<sub>WAITQ</sub> vs Temperature

# 9 Detailed Description

#### 9.1 Overview

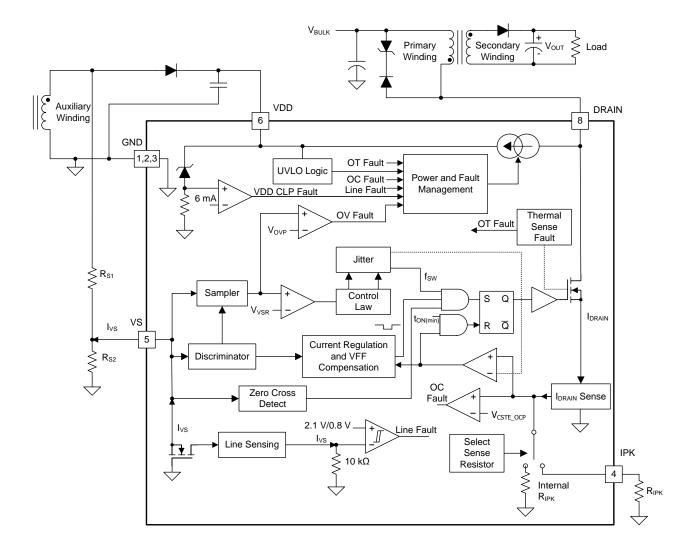

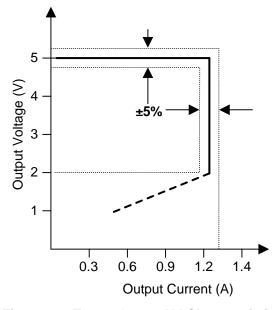

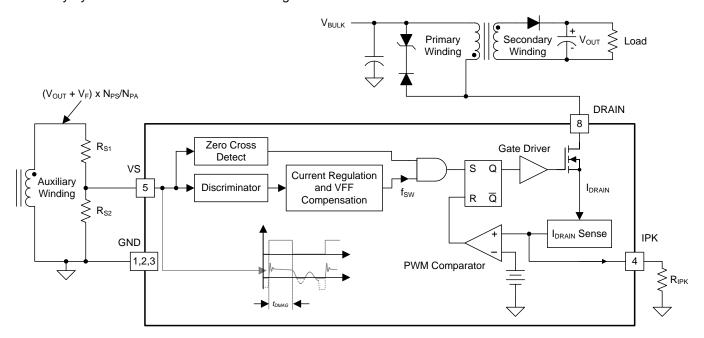

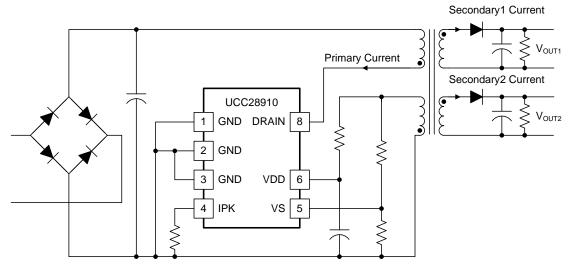

UCC28910 and UCC28911 are HV switchers dedicated to an off-line power supply in an isolated flyback configuration. HV switcher means that each device integrates the power switch, a 700-V power FET, with the control logic. The two devices have the same control logic and they are different only for the Power FET R<sub>DS(on)</sub> and for the operating current levels. The control logic controls both the output voltage and the output current without the need of an optical coupler. This control method is known as Primary-Side Regulation (PSR) and it operates by analyzing the voltage waveform on the auxiliary winding of the transformer. This allows significant cost saving with respect to traditional control scheme that uses an optical coupler for feedback from a secondaryside shunt regulator. The transformer auxiliary winding is also used to provide housekeeping supply power to the control logic. The device operates in Constant Voltage mode (CV) when it is controlling the output voltage. The device operates in Constant Current mode (CC) when the output current is controlled. The device operates in CV mode or in CC mode according to the load condition. (See Figure 24). A control algorithm that implements both modulation of the switching frequency and the amplitude modulation of the primary current peak, allows the power supply to operate efficiently over the entire load range. The high-voltage current source used for startup is kept off during normal operation thereby minimizing standby power consumption. The device also incorporates a smart power management to minimize its current consumption from the VDD pin. This power consumption is reduced when the converter is lightly loaded or unloaded allowing for a total input power of less than 30 mW when converter input voltage is 265 V<sub>AC</sub> and unloaded. A number of protection features inside the device allow for improved overall system reliability.

# 9.2 Functional Block Diagram

#### 9.3 Feature Description

UCC28911 and UCC28910 are flyback power supply switchers which provide accurate output voltage and constant current regulation with primary-side feedback, eliminating the need for optical coupler feedback circuits. The device has an internal 700-V power FET plus a controller which forces the converter to operate in discontinuous conduction mode with valley switching to minimize switching losses. The modulation scheme is a combination of frequency and primary-peak current modulation to provide optimized conversion efficiency over the entire load range. The control law provides a wide dynamic operating range to achieve less than 30-mW standby power.

UCC28911 and UCC28910 include features in the modulator to reduce the EMI peak energy of the fundamental switching frequency and harmonics. Accurate voltage and constant current regulation, fast dynamic response, and fault protection are achieved with primary-side control.

A complete charger solution can be realized with a straightforward design process, low cost and low component count solution.

# 9.3.1 Primary-Side Voltage Regulation

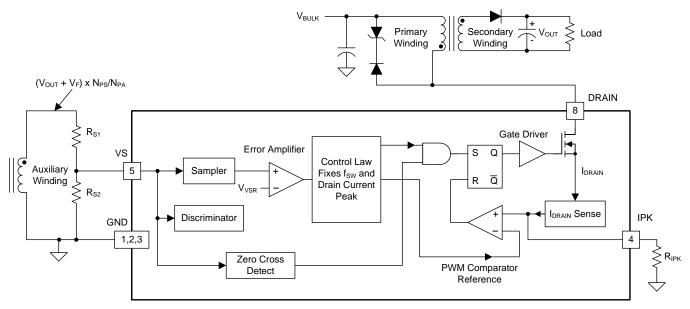

Figure 20 illustrates a flyback converter. The voltage regulation blocks of the device are shown. The power train operation is the same as any DCM flyback circuit but accurate output voltage and current sensing is the key to primary side control.

Figure 20. Voltage Loop Block Diagram

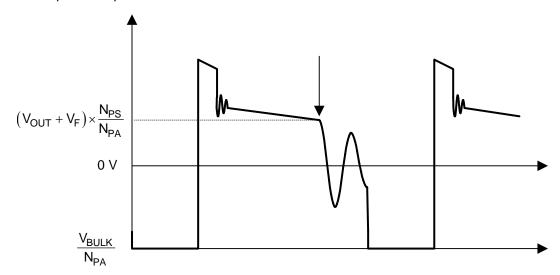

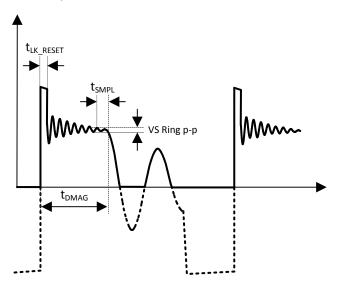

In primary-side control, the output voltage is sensed by the auxiliary winding during the transfer of transformer energy to the secondary. Figure 21 shows the down slope representing a decreasing total rectifier  $V_F$  and the secondary winding resistance voltage drop as the secondary current decreases to 0 A. To achieve an accurate representation of the secondary output voltage on the auxiliary winding, the *Discriminator Block* (Figure 20) reliably ignores the leakage inductance reset and ring, continuously samples the auxiliary voltage during the down slope after the ringing is diminished, and captures the error signal at the time the secondary winding reaches 0 current. The internal reference on VS is 4.05 V ( $V_{VSR}$  typical); the resistor divider is selected as outlined in the VS pin description.

Figure 21. Auxiliary Winding Voltage

The UCC28910 VS signal *Discriminator Block* (Figure 20) ensures accurate sampling time for an accurate sample of the output voltage from the auxiliary winding. There are however some details of the auxiliary winding signal to ensure reliable operation, specifically the reset time of the leakage inductance and the duration of any subsequent leakage inductance ring. Refer to Figure 22 for a detailed illustration of waveform criteria to ensure a reliable sample on the VS pin. The first detail to examine is the duration of the leakage inductance reset pedestal,  $t_{LK\_RESET}$ . Since this can mimic the waveform of the secondary current decay, followed by a sharp down-slope, it is important to keep the leakage reset time less than 500 ns for  $I_{DRAIN}$  minimum, and less than 1.5  $\mu$ s for  $I_{DRAIN}$  maximum. The second detail is the amplitude of ringing on the auxiliary winding waveform ( $V_{AUX}$ ) following  $t_{LK\_RESET}$ . The peak-to-peak voltage at the VS pin should be less than approximately 100 mV<sub>p-p</sub> at least 200 ns before the end of the demagnetization time,  $t_{DMAG}$ . If there is a concern with excessive ringing, it usually occurs during light or no-load conditions, when  $t_{DMAG}$  is at the minimum. The tolerable ripple on VS is scaled up to the auxiliary winding voltage by  $R_{S1}$  and  $R_{S2}$ , and is equal to 100 ( $R_{S1} + R_{S2}$ ) /  $R_{S2}$  mV.

During voltage regulation, the controller operates in frequency modulation mode and amplitude modulation mode. The internal operating frequency limits of the controller are 115 kHz maximum and 420 Hz minimum. The transformer primary inductance and turns ratio sets the maximum operating frequency of the converter. The output preload resistor and efficiency at low power determines the converter minimum operating frequency. There is no external compensation required for the UCC2891x devices.

Figure 22. VS Voltage

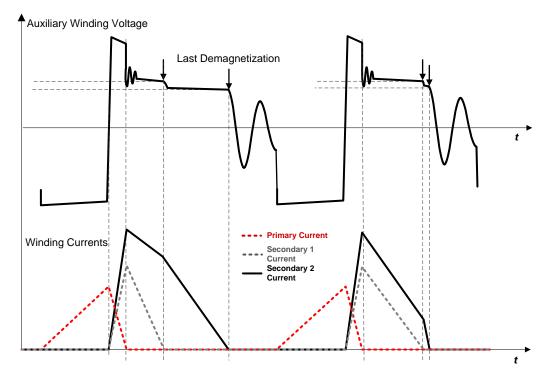

#### 9.3.2 Primary-Side Current Regulation

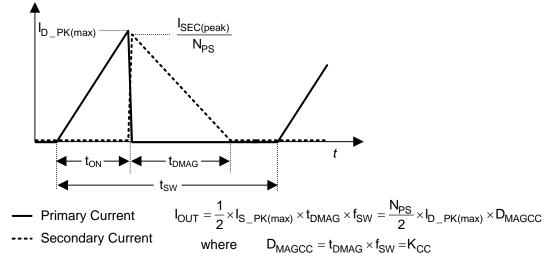

Timing information at the VS pin and the primary current information allow accurate regulation of the secondary average current. The control law dictates that as power is increased in CV regulation and approaching CC regulation the primary-peak current is at  $I_{D\_PK(max)} = V_{CSTE(max)} / R_{IPK}$ . Referring to Figure 23, the primary-peak current, turns ratio, secondary demagnetization time  $(t_{DMAG})$ , and switching period  $(t_{SW})$  establish the secondary average output current. When the average output current reaches the regulation reference in the current control block, the controller operates in frequency modulation mode to control the output current at any output voltage at or below the voltage regulation target as long as the aux winding can keep VDD above the VDD UVLO threshold  $(VDD_{OFF})$ .

Figure 23. Output Current Estimation

Figure 24. Target Output V-I Characteristic

$K_{CC}$  is defined as the maximum value of the secondary-side conduction duty cycle ( $D_{MAGCC}$  in Figure 23). It is set internally by the UCC2891x and occurs during constant current control mode.

Figure 25. Output Current Control Loop Block Diagram

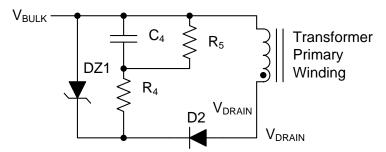

#### 9.3.3 Voltage Feed Forward Compensation

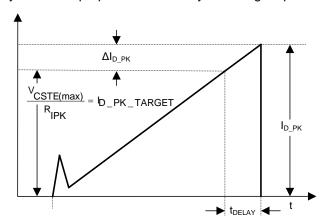

During normal operation the on-time is determined by sensing the power FET current and switching off the power FET as this current reaches a threshold fixed by the feedback loop according to the load condition. The power FET is not immediately turned off and its current, that is also the primary winding current, continues to rise for some time during the propagation delay ( $t_{DELAY}$  in Figure 26). Keeping the reference for the PWM comparator constant, the value of the primary winding peak current depends on the slope of the primary winding current and  $t_{DELAY}$ . The slope of the primary current is proportional to the flyback stage input voltage ( $V_{BULK}$ )

Figure 26. Propagation Delay Effect on the Primary Current Peak

$$\Delta I_{D_{-}PK} = \frac{V_{BULK}}{L_{P}} \times t_{delay}$$

(4)

$$I_{D\_PK} = I_{D\_PK\_TARGET} + \frac{V_{BULK}}{L_{P}} \times t_{delay}$$

(5)

The current loop estimates the output current assuming the primary winding peak current is equal to the  $I_{PK\_TARGET}$  and compares this estimated current with a reference to obtain the current regulation. Considering,  $I_{D\_PEAK}$  is different from  $I_{D\_PEAK\_TARGET}$  (see Figure 26) we need to compensate the effect of the propagation delay. The UCC28910 and the UCC28911 incorporate fully-integrated propagation-delay compensation that modifies the switching frequency keeping the output current constant during (CC) Constant Current Mode operation. This function is integrated in the controller and requires no external components. This feature keeps the output current constant despite input voltage variations and primary inductance value spread.

#### 9.3.4 Control Law

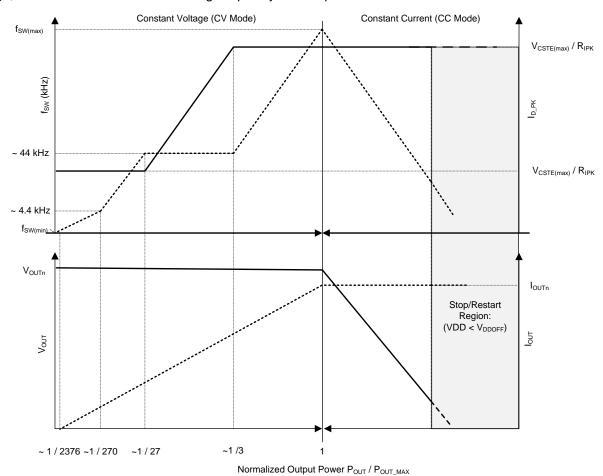

During voltage regulation, the device operates in switching frequency modulation mode and primary current peak amplitude modulation mode. The internal operating frequency limits of the device are  $f_{SW(max)}$  and  $f_{SW(min)}$ . During constant current regulation the device operates only in frequency modulation mode reducing the switching frequency as the output voltage decreases. Figure 27 shows how the primary peak current and the switching frequency change with respect to changes in load. The solid lines are primary-side peak current and the output voltage, the dotted lines are the switching frequency and output current.

Figure 27. Control Law Profile

#### 9.3.5 Valley Switching

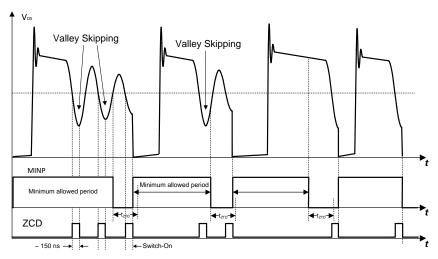

The UCC28910 and the UCC28911 utilize valley switching to reduce switching losses in the MOSFET and minimize the current spike at the FET turn on. The UCC28910 operates in valley switching in almost all load conditions until the  $V_{DS}$  ringing is diminished. By switching at the lowest  $V_{DS}$  voltage the MOSFET turn on dV / dt is minimized which is a benefit to reduce EMI.

Referring to Figure 28, devices will operate in a valley switching mode in most load conditions to switch-on at the lowest available  $V_{DS}$  voltage. According to the load it is established a minimum switching period. The MOSFET is switched-on at the first valley that occurs after this minimum period is elapsed. With this control scheme the device can be turned-on at the first valley that occurs after transformer demagnetization or it can skip some valleys before turn-on operating in this case in the so called valley skipping mode. Valley switching is maintained during constant current regulation to provide improved efficiency and EMI benefits in constant current operation. If for some reason no valley is detected at the end of the  $t_{ZTO}$  time the MOSFET turns-on. In order to guarantee discontinuous mode operation at least the first valley needs to be detected or the Mosfet is not turned-on (see Figure 28).

Figure 28. Valley Skipping

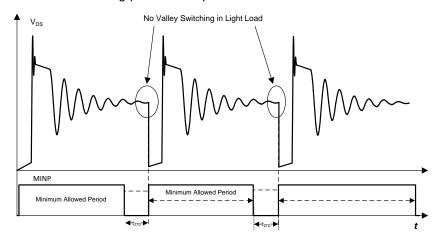

In very light-load or no-load condition the  $V_{DS}$  ringing amplitude is very low and not easy to detect, moreover with very low ringing amplitude there would be no benefit in valley switching so in this condition the valley switching is disabled (see Figure 29). The device switch on the MOSFET as soon the time  $t_{ZTO}$  is elapsed. The  $t_{ZTO}$  timer starts as soon as the minimum switching period is elapsed.

Figure 29. Valley Switching Disable at Light Load

# 9.3.6 Startup Operation

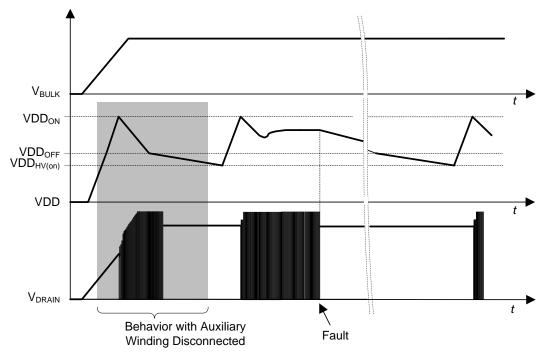

The UCC28910 and UCC28911 are provided with a high-voltage current source, connected between the DRAIN pin and the VDD pin; this current source is activated when a voltage is applied on DRAIN pin. The current source charges the capacitor connected between VDD and GND increasing the VDD voltage. As VDD exceeds VDD<sub>ON</sub> the current source is turned off and the controller internal logic is activated and the device starts switching. If the VDD voltage falls below the VDD<sub>OFF</sub> threshold, or a fault condition is detected, the controller stops operation and its current consumption is reduced to I<sub>START</sub> or I<sub>FAULT</sub>. The high-voltage current source is turned on again when VDD voltage goes below VDD<sub>HV(on)</sub> (see Figure 30 for reference).

The initial three cycles are limited to  $I_{D\_PEAK(max)}$  / 3. This allows sensing any input or output faults with minimal power delivery. After the initial three cycles at  $I_{D\_PEAK(max)}$  / 3, the controller responds to the condition dictated by the control law.

Figure 30. Start Up and Auto Re-Start Operation

The converter remains in DCM during charging of the output capacitor(s), and operates in constant current mode until the output voltage is in regulation.

To avoid high-power dissipation inside the device, such as in the event that VDD is accidentally shorted to GND, the current provided by the high-voltage current source is reduced ( $I_{CH1}$ ) when VDD < 1 V (typical).

#### 9.3.7 Fault Protection

There is comprehensive fault protection incorporated into the UCC2891x. Protection functions include:

- Output Over-Voltage Fault

- Input Under-Voltage Fault

- Primary Over-Current Fault

- VDD Clamp Over Current

- Thermal Shut Down

#### 9.3.7.1 Output Over-Voltage

The output over-voltage function is determined by the voltage feedback on the VS pin. If the voltage sample on VS exceeds 4.6 V, which correlates to 113.5% of nominal  $V_{OUT}$ , the device stops switching and reduces its current consumption to  $I_{FAULT}$ , slowly discharging the VDD capacitor to the VDD $_{HV(on)}$  threshold. At this time the standard startup sequence begins. The initial three cycles of startup at low-peak DRAIN current is important to monitor  $V_{OUT}$  and deliver minimal power. The reset and restart, or hiccup, sequence applies for all fault protection. The slow VDD capacitor discharge after a fault allows the high voltage current source to have a low duty cycle to avoid over heating of the device if a fault condition is continuously present resulting in a repetitious start up sequence.

#### 9.3.7.2 Input Under-Voltage

The input under voltage is determined by current information on the VS pin during the MOSFET on time. The VS pin is clamped close to GND during the MOSFET on time; at this time the current though  $R_{S1}$  is monitored to determine a sample of the bulk capacitor voltage. The under voltage shutdown current on VS is 75  $\mu$ A; the enable current threshold is 210  $\mu$ A. The device must sense the under-voltage condition for three consecutive switching cycles to recognize it as a fault condition. After an under-voltage fault, the same sequence described for output overvoltage occurs.

#### 9.3.7.3 Primary Over-Current

The UCC28910 and the UCC28911 always operates with cycle-by-cycle primary current control. The normal operating range for the peak DRAIN current depends on the resistance ( $R_{IPK}$ ) connected between the IPK pin and the GND pin. The peak DRAIN current should not exceed  $I_{D\_PEAK(max)}$  even if the IPK pin is shorted to GND, or should not exceed  $V_{CSTE}$  /  $R_{IPK}$  if the IPK pin is tied to GND with the resistance  $R_{IPK}$ . There are different reasons the DRAIN current can go out of control, for example a secondary winding short or hard saturation of the transformer. To avoid over-stress of the power FET additional protections are added. If the DRAIN current exceeds  $I_{DOCP}$  (~33% higher than  $I_{D\_PEAK(max)}$ ), such as when IPK pin is shorted to GND, or  $V_{CSTE\_OCP}$  /  $R_{IPK}$ , ( $V_{CSTE\_OCP}$  ~33% higher than  $V_{CSTE(max)}$ ), and the condition is sensed for three consecutive switching cycles, a fault shutdown and retry sequence, detailed in the output overvoltage fault description, occurs. If the DRAIN current exceeds a second level of current ( $V_{CSTE\_OCP2}$  /  $R_{IPK}$ ) it is not necessary to detect the fault for three consecutive switching cycles, the device will stop switching immediately.

#### 9.3.7.4 VDD Clamp Over-Current

The VDD pin is provided with an internal clamp to prevent the pin voltage from exceeding the absolute maximum rating. If the current in the clamp exceeds 6 mA (typical), in order to avoid any damage to the device and to the system, a fault condition is assumed and the device stops operation.

#### 9.3.7.5 Thermal shutdown

The internal thermal shutdown threshold is  $150^{\circ}$ C (typical) with a hysteresis of  $50^{\circ}$ C (typical). If an overtemperature is detected the device stops switching and its current consumption is reduced to  $I_{FAULT}$ . The VDD voltage will decrease to  $V_{DDHV(on)}$  where the high voltage current source is activated and the VDD voltage will rise again until  $V_{DD(on)}$  where the internal logic is re-activated. If the temperature of the device is not dropped below approximately  $100^{\circ}$ C ( $150^{\circ}$ C-  $50^{\circ}$ C) no switching cycles occurs and the fault condition is maintained and the current consumption is again  $I_{FAULT}$ . For diagnostic purpose, when a thermal shut down occurs a short voltage pulse, whose amplitude is around 2 V, is transmitted on the  $I_{PK}$  pin. Thermal shut down feature is not intended to protect the device itself but mainly to control the damage caused by the device thermally overstressed.

Copyright © 2013–2016, Texas Instruments Incorporated

#### 9.3.8 EMI Dithering

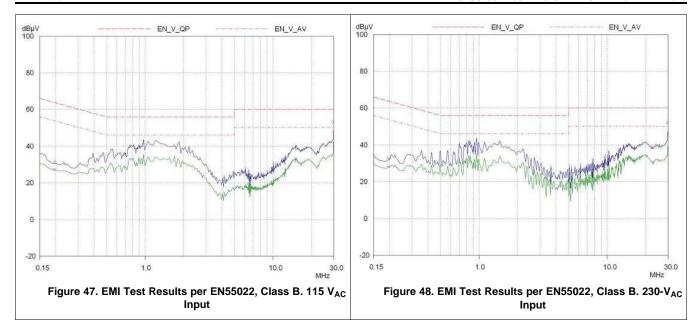

Generally, power supply designs need to pass EMI standard such as EN55022. When the device-controlled Flyback design is used as the auxiliary power supply in a larger system, such as motor drive or home appliance, the EMI filter for the entire system should be enough to filter out the EMI noise created by the Flyback converter. However, when the Flyback is a standalone power supply, the EMI noise becomes a concern.

The EMI noise is normally managed by adding necessary EMI filtering or circuit techniques such as the parasitic capacitor control, snubbering, or transformer EMI noise cancelation windings. Besides these, in both the UCC28910 and UCC28911 devices, the MOSFET switching speed is controlled so that the EMI noise can be minimized. Furthermore, EMI dithering technique is also implemented.

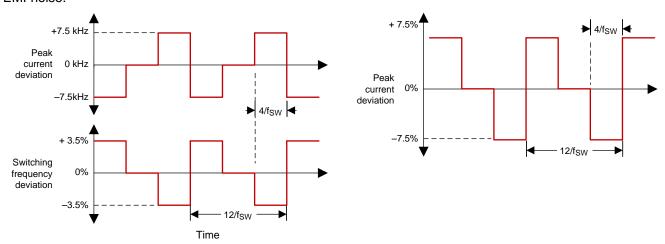

The EMI receiver uses a 9-kHz bandwidth detector to measure the noise energy within that bandwidth. If a power supply switching frequency is slightly changed with time, so that the switching frequency energy can be spread outside 9-kHz band, the measured EMI noise can be smaller. This technique makes it easier to pass the EMI standard. This switching frequency change technique is often called EMI dithering or jittering.

The EMI dithering scheme used in these devices effectively change the switching frequency outside of 9-kHz EMI receiver band, while minimize the output voltage ripple caused by the EMI dithering effect. The frequency modulation is based on a 12-cycle repeat rate. In each 12 switching cycles, there are three groups of 4 switching cycle, with three frequency deviations and three peak current settings. Figure 31 illustrates a group of 4 switching cycles, the center frequency and desired peak current. Figure 32 illustrates a group of reduced switching frequency (–7.5 kHz) with increased peak current (+3.5%) and a group of increased switching frequency (+7.5 kHz) with decreased peak current (–3.5%). The 7.5 kHz frequency deviation is selected to spread the switching frequency noise energy outside of 9-kHz EMI detector bandwidth. In turn, this frequency reduces the measured EMI noise.

Figure 31. EMI Dithering During CV Mode Operation

Figure 32. EMI Dithering During CC Mode Operation

The UCC28910 and UCC28911 devices control the Flyback converter during DCM operation only. The frequency change with fixed peak current may result in output voltage ripple because of the fluctuation of the energy delivery. By adjusting the peak current and frequency at the same time allows minimum variation on the energy delivery and reduces the output voltage ripple. During CC mode operation, the switching frequency is controlled to deliver the constant output current. Therefore, only the peak current is modulated to achieve equivalent EMI dithering.

The EMI dithering is disabled in the light load when the device enters a WAIT state.

#### 9.4 Device Functional Modes

According to the input voltage, the VDD voltage, and the load conditions, the device can operate in different modes:

- 1. At start-up with  $V_{DRAIN} > 20$  V, VDD = 0 V, the HV voltage current source is ON and starts to charge the capacitor connected to the VDD pin. With VDD < 1 V the current provided is limited < 500  $\mu$ A and VDD rises slowly.

- When VDD exceeds 1 V (VDD < VDD<sub>ON</sub>) the HV current source provides higher current and VDD rises faster.

- 3. When VDD exceeds VDD<sub>ON</sub> the device starts switching and delivers power to its output. According to its load, the converter operates in CV mode or in CC mode.

- (a) CV mode means that the converter keeps the output voltage constant. This operating mode takes place when  $R_{LOAD} > V_{OCV} / I_{OCC}$  where  $V_{OCV}$  is the target for output voltage and  $I_{OCC}$  is the maximum converter output current. In this condition the converter output voltage  $V_{OUT} = V_{OCV}$  and the converter output current  $I_{OUT} < I_{OCC}$ .

- (b) CC mode means that the converter keeps the output current constant. This operating mode takes place when  $R_{LOAD} < V_{OCV} / I_{OCC}$ . In this condition the converter output voltage  $V_{OUT} < V_{OCV}$  and the converter output current  $I_{OUT} = I_{OCC}$ .

- 4. Device operations can be stopped because of the events listed below:

- (a) If VDD drops below VDD<sub>OFF</sub>, the device stops switching and its current consumption is lowered to I<sub>START</sub>. Because the converter is not switching, no energy is delivered from the auxiliary winding, the HV current source is off, then the VDD capacitor is discharged with I<sub>START</sub> current.

- (b) If a fault is detected device stops switching and its current consumption is lowered to I<sub>FAULT</sub> that slowly discharges the VDD capacitor down to VDD<sub>OFF</sub> where the current consumption is I<sub>START</sub> < I<sub>FAULT</sub> and the VDD capacitor continues to discharge.

- After the device stops switching, because of 4a or 4b, the VDD voltage drops, when it goes below VDD<sub>HV(on)</sub>, the HV current source is turned on recharging the VDD capacitor up to VDD<sub>ON</sub>.

- 6. When a fault condition is permanently present, the device operates in auto restart-mode. This means that a fault condition is detected, the device stops operation as described in 4b, then VDD drops down to VDD<sub>HV(on)</sub> when the device start-up sequence takes place. At device turn-on, the fault is again detected and the cycle repeats.

# 10 Applications and Implementation

# **10.1** Application Information

The UCC28910 and UCC28911 devices are HV switcher that integrates an HV power FET plus a controller that uses primary-side-regulated (PSR), supporting magnetically-sensed output voltage regulation via the transformer bias winding. This sensing eliminates the need for a secondary-side reference, error amplifier and optical-isolator for output voltage regulation. The devices deliver accurate output voltage static load and line regulation, and accurate control of the output current. The magnetic sampling scheme allows operation only in discontinuous conduction mode (DCM) so the device is not allowed to turn on the Power FET if it doesn't sense a ZCD event. A ZCD event is when auxiliary winding voltage crosses zero from high to low after transformer demagnetization is completed. The modulator adjusts both frequency and peak current in different load regions to maximize efficiency throughout the operating range. The smart management of the control logic power consumption and the HV current source, used for startup that is off during operation and have very low leakage current, allow designing converters with very low standby input power. The less than 30mW can be easily achieved with these devices.

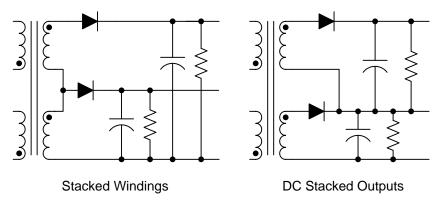

# 10.2 Typical Application

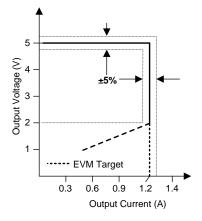

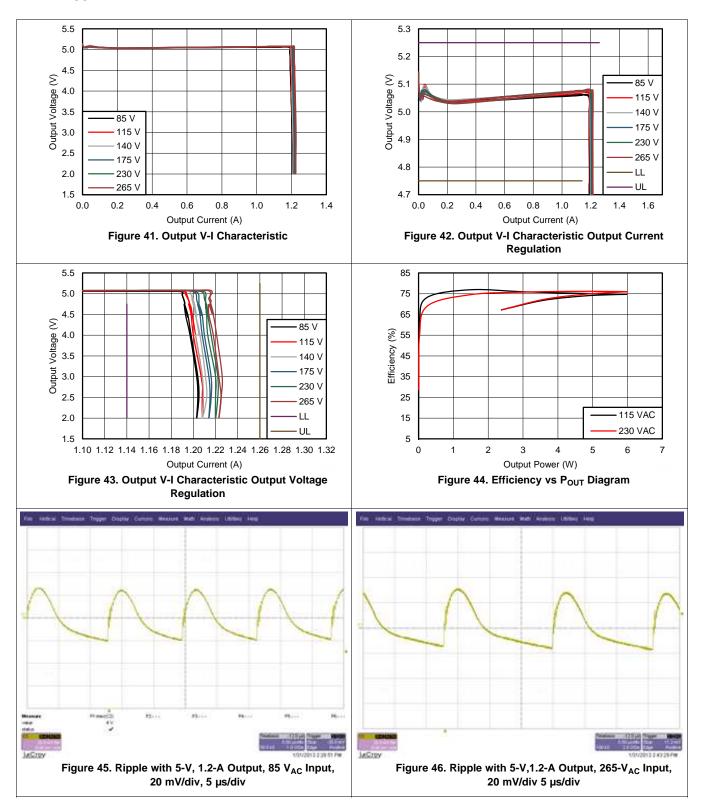

# 10.2.1 Battery Charger, 5 V, 6 W

This design example describes the UCC28910FBEVM-526 design and outlines the design steps required to design a constant-voltage, constant-current flyback converter for a 5-V/6-W charger. Discontinuous conduction mode (DCM) with valley switching is used to reduce switching losses. A combination of switching frequency and peak primary current amplitude modulation is used to keep conversion efficiency high across the full load and input voltage range. Figure 33 below details the output V-I characteristic. Low system parts count and built in advanced protection features result in a cost-effective solution that meets stringent world-wide energy efficiency requirements.

Figure 33. Target Output V-I Characteristic

# **Typical Application (continued)**

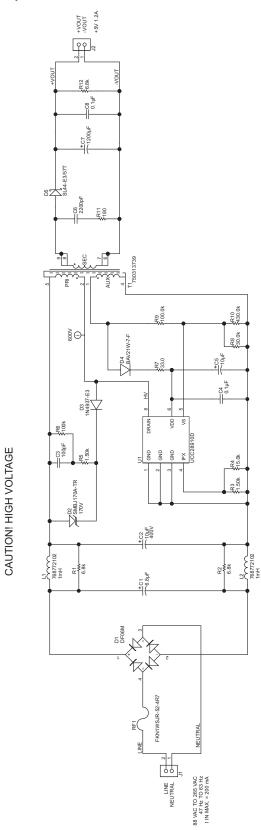

Figure 34. UCC28910FBEVM-526 Schematic

# **Typical Application (continued)**

# 10.2.1.1 Design Requirements

For this design example, use the parameters listed in Table 1.

**Table 1. Design Parameters**

|                       | PARAMETER                 | TEST CONDITIONS                                                | MIN  | TYP         | MAX       | UNIT |

|-----------------------|---------------------------|----------------------------------------------------------------|------|-------------|-----------|------|

| INPUT CI              | HARACTERISTICS            |                                                                |      |             |           |      |

| V <sub>IN</sub>       | Input voltage             |                                                                | 90   | 115/230     | 265       | V    |

| f <sub>LINE</sub>     | Frequency                 |                                                                | 47   | 50/60       | 64        | Hz   |

| P <sub>NL</sub>       | No load power             | $V_{IN} = V_{NOM} I_{OUT} = 0 A$                               |      | 15          | 20        | mW   |

| $V_{\text{INUVLO}}$   | Brownout voltage          | $I_{OUT} = I_{NOM}$                                            |      | 70          |           | V    |

| $V_{INOV}$            | Brownout recovery voltage |                                                                |      | 80          |           | V    |

| I <sub>IN</sub>       | Input current             | $V_{IN} = V_{MIN}$ , $I_{OUT} = max$                           |      | 0.2         |           | Α    |

| OUTPUT                | CHARACTERISTICS           |                                                                |      |             |           |      |

| V <sub>OUT</sub>      | Output voltage            | $V_{IN} = V_{MIN}$ to $V_{MAX}$ , $I_{OUT} = 0$ V to $I_{NOM}$ | 4.75 | 5.00        | 5.25      | V    |

| I <sub>OUT(max)</sub> | Maximum output current    | $V_{IN} = V_{MIN}$ to $V_{MAX}$                                | 1.14 | 1.20        | 1.26      | Α    |

| I <sub>OUT(min)</sub> | Minimum output current    | $V_{in} = V_{min}$ to $V_{MAX}$                                |      | 0           |           | Α    |

| $\Delta V_{OUT}$      | Output voltage ripple     | $V_{IN} = V_{MIN}$ to $V_{MAX}$ , $I_{OUT} = 0$ V to $I_{NOM}$ |      | 150         |           | mV   |

| $P_{OUT}$             | Output power              | $V_{IN} = V_{MIN}$ to $V_{MAX}$                                |      |             |           |      |

| SYSTEM                | CHARACTERISTICS           |                                                                |      |             |           |      |

| η                     | Average efficiency        | 25%, 50%, 75%, 100% of I <sub>OUT</sub>                        |      | 75%         |           |      |

| ENVIRON               | MENTAL                    |                                                                |      |             |           |      |

|                       | Conducted EMI             |                                                                | Me   | ets CISPR22 | 2B/EN5502 | 2B   |

#### 10.2.1.2 Detailed Design Procedure

This procedure outlines the steps to design a constant-voltage, constant-current flyback converter based on UCC28910 switcher. Refer to the Figure 35 for component names and network locations. The design procedure equations use terms that are defined below.

Figure 35. Standard Flyback Converter Based on UCC2891x

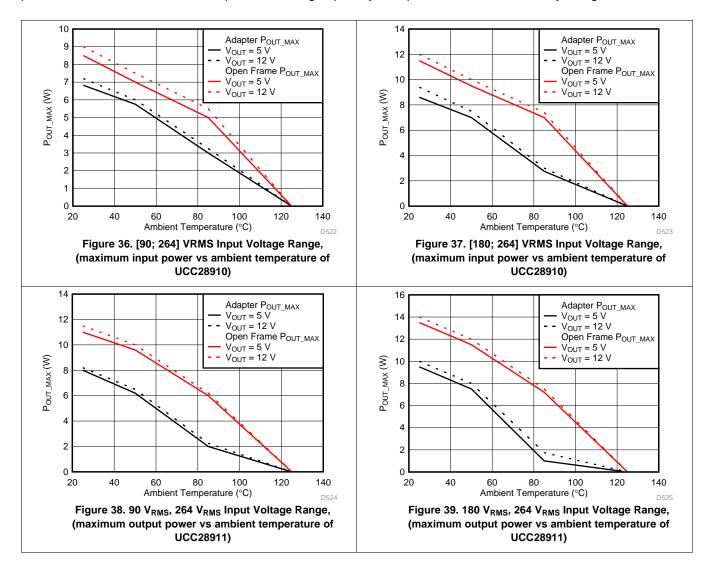

#### 10.2.1.2.1 Power Handling Curves

The power handling curves give the maximum output power that can be handled by the devices versus the ambient temperature. These curves give the maximum output power achievable considering that the losses inside the device can cause rise of the junction temperature up to 125°C. The thermal resistance junction to ambient were provided with considerations to two different values. Thermal resistances values of 50°C /W and of 100°C / W were considered.

The device handling capability depends on the overall design and input and output voltage. Figure 36 and Figure 38 refer to a wide-range input voltage (90  $V_{AC}$ ; 264  $V_{AC}$ ) converter; Figure 37 and Figure 39 refer to a European range input voltage (180  $V_{AC}$ ; 265  $V_{AC}$ ). The dotted line curves refer to 12-V output voltage AC-to-DC converter, the continuous line curves refer to 5-V output voltage converter.

Figure 36 and Figure 37 show the power handling capabilities of UCC28910 and Figure 38 and Figure 39 show the power handling capabilities of UCC28911.

Table 2. Maximum Output Power<sup>(1)</sup>

| PART NUMBER | 180 V <sub>AC</sub> to 265 V <sub>AC</sub> |                | 90 V <sub>AC</sub> to  | UNITS          |   |

|-------------|--------------------------------------------|----------------|------------------------|----------------|---|

|             | Adapter (2)                                | Open Frame (3) | Adapter <sup>(2)</sup> | Open Frame (3) |   |

| UCC28910    | 6.5                                        | 9.5            | 6                      | 7.5            | W |

| UCC28911    | 8                                          | 12             | 7.5                    | 10             | W |

<sup>(1)</sup> Table 2 is obtained considering 125°C as maximum junction temperature. For lower operating maximum junction temperature, the maximum output power should be lower.

Product Folder Links: UCC28910 UCC28911

<sup>(2)</sup> Typical continuous power in enclosed adapter at 50°C ambient, with adequate ( > 560 mm<sup>2</sup>) copper area connected on GND pin to have 90°C/W as junction to ambient thermal resistance.

<sup>(3)</sup> Maximum continuous power with open frame design at 50°C ambient, with adequate copper area connected on GND pin and/or adequate air flow to have 50°C/W as junction to ambient thermal resistance.

The curves provided show the maximum power obtained through optimized designs.

A lower-efficiency design requires the converter to process more input power to deliver the same amount of power to the load. Therefore, less power handling capability is expected for lower-efficiency designs.

#### 10.2.1.2.2 Input Stage Design and Bulk Capacitance

The input stage consists of:

- 1. Input fuse resistor (R<sub>IN</sub>) is generally used to:

- (a) Limit the inrush current on the input capacitor when the line voltage is applied.

- (b) Disconnect the line in case of input over current.

- 2. A bridge diode or a single-wave rectifier diode used to rectify the main voltage.

- 3. A bulk capacitor (capacitors C1 and C2) that stores the energy and reduces input voltage ripple.

- 4. A line filter (L1, L2, R1, and R2) to reduce EMI generated by switching.

The minimum input capacitance voltage, the input power of the converter based on target full-load efficiency, minimum input RMS voltage, and minimum AC input frequency are used to determine the input capacitance requirement.

The maximum converter input power can be estimated from the output voltage in voltage constant mode,  $V_{OCV}$ , the converter's output current when operating in constant current more,  $I_{OCC}$ , and the full-load efficiency target,  $\eta$ .

$$P_{IN} = \frac{V_{OCV} \times I_{OCC}}{\eta}$$

(6)

The following equation provides an accurate solution for input capacitance based on a target minimum bulk capacitor voltage. To target a given input capacitance value, iterate the minimum capacitor voltage to achieve the target capacitance.

$$C_{BULK} = \frac{\frac{2 \times P_{IN}}{f_{LINE(min)}} \times \left(\frac{1}{RCT} - \frac{1}{2 \times \pi} \times \arccos\left(\frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}}\right)\right)}{2 \times V_{IN(min)}^2 - V_{BULK(min)}^2}$$

(7)

In the case where the input rectifier is a single diode (half wave rectifier), and for applications with bridge input rectifier (full wave rectifier), as in the schematic of Figure 31.

The voltage  $V_{BULK(min)}$  is generally selected around 65% to 60% of  $\sqrt{2}$  x  $V_{IN(min)}$ .  $V_{BULK(min)}$  is determined by the selection of the high-voltage input capacitors.

For the considered example we have:

$$P_{IN} = \frac{V_{OCV} \times I_{OCC}}{\eta} = \frac{5V \times 1.2 \,\text{A}}{0.72} = 8.33 \,\text{W} \tag{8}$$

$$C_{BULK} = \frac{\frac{2 \times 8.33 \,\text{W}}{57 \,\text{Hz}} \times \left\{ \frac{1}{2} - \frac{1}{2 \times \pi} \times \arccos\left(\frac{80 \,\text{V}}{124 \,\text{V}}\right) \right\}}{2 \times (88 \,\text{V})^2 - (80 \,\text{V})^2} = 11.7 \,\mu\text{F} \tag{9}$$

Taking into account that electrolytic capacitance, with 20% of tolerance, the values selected for C1 and C2 are: C1 = 6.8  $\mu$ F and C2 = 10  $\mu$ F.

#### 10.2.1.2.3 Transformer Turns Ratio

The maximum primary-to-secondary turns ratio can be determined by the target maximum switching frequency at full load, the minimum input capacitor bulk voltage, and the estimated DCM quasi-resonant time. Initially determine the maximum available total duty cycle of the on-time and secondary conduction time based on target switching frequency and DCM resonant time. For DCM resonant time, assume  $t_R=1$  / 500 kHz if you do not have an estimate from previous designs. For the transition mode operation limit, the period required from the end of secondary current conduction to the first valley of the  $V_{DS}$  voltage is half of the DCM resonant period, or 1  $\mu$ s assuming 500-kHz resonant frequency.  $D_{MAX}$  can be determined using the equation below.

$$D_{MAX} = 1 - \left(\frac{t_R}{2} \times f_{SW(max)}\right) - K_{CC}$$

(10)

Where  $K_{CC}$  is the regulation gain in constant current control mode and is equal to the secondary diode conduction duty cycle when the converter is operating at maximum output current.

Once  $D_{\text{MAX}}$  is known, the maximum turn ratio of the primary-to-secondary can be determined with the equation below.

$$N_{PS(max)} = \frac{D_{MAX} \times V_{BULK(min)}}{K_{CC} \times (V_{OCV} + V_F)}$$

(11)

The total voltage on the secondary winding needs to be determined; the sum of  $V_{OCV}$  and the secondary rectifier  $V_F$ . The voltage  $V_{BULK(min)}$  is generally selected around 65% or 60% of the peak of low-line.  $V_{BULK(min)}$  is determined by the selection of the high-voltage input capacitors.

For the 5-V USB charger applications N<sub>PS</sub> values from 13 to 17 are typically used.

For our example the maximum value for primary to secondary turn ratio will be:

$$N_{PS(max)} = \frac{0.482 \times 80 \text{ V}}{0.413 \times (5\text{V} + 0.35\text{ V})} = 17.45$$

(12)

In this example we fix  $N_{PS} = 16.5$