**TUSB216I** SLLSFM9A - MARCH 2021 - REVISED DECEMBER 2023

# TUSB216I USB 2.0 High-Speed Signal Conditioner With BC 1.2 Controller

#### 1 Features

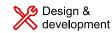

- Wide supply voltage range: 2.3 6.5 V

- Ultra-low USB disconnect and shutdown power consumption

- Provides USB 2.0 high-speed signal conditioning

- Compatible with USB 2.0, OTG 2.0 and BC 1.2

- Support for low-speed, full-speed, high-speed

- Integrated BC 1.2 CDP battery charging controller

- Host or device agnostic

- Supports up to 5-m cable length

- Four selectable signal boost (edge boost along with DC boost) settings through the external pull-down resistor values

- Three selectable RX sensitivity settings through the pull-up-or-down to compensate ISI jitter for high-loss applications

- Supports up to 10-m cable length with two TUSB216I devices

- Scalable solution devices can be daisy chained for high loss applications

- · Pin compatible with TUSB211A, 212, 214, and 217A (3.3 V)

# 2 Applications

- Laptop, desktop or docking stations

- Portable electronics

- **Tablets**

- Cell phones

- **Televisions**

- Active cable, cable extenders, backplane

# 3 Description

The TUSB216I is a third-generation USB 2.0 highspeed signal conditioner designed to compensate both AC loss (due to capacitive load) and DC loss (due to resistive loss) in the transmission channel.

The TUSB216I leverages a patented design to speedup transition edges of USB 2.0 high-speed signal with an edge booster and increases static levels with a DC boost function.

In addition, the TUSB216I includes a pre-equalization function to improve the receiver sensitivity and compensate the inter-symbol interference (ISI) jitter in application with longer cable length. USB low-speed and full-speed signal characteristics are unaffected by the TUSB216I.

The TUSB216I improves signal quality without altering packet timing or adding propagation delay or latency.

The TUSB216I helps a system to pass the USB 2.0 high-speed near end eye compliance with a cable as long as 5 meters.

The TUSB216I is compatible with the USB On-The-Go (OTG) and battery charging (BC 1.2) protocols. The Integrated BC 1.2 battery charging controller can be enabled through a control pin.

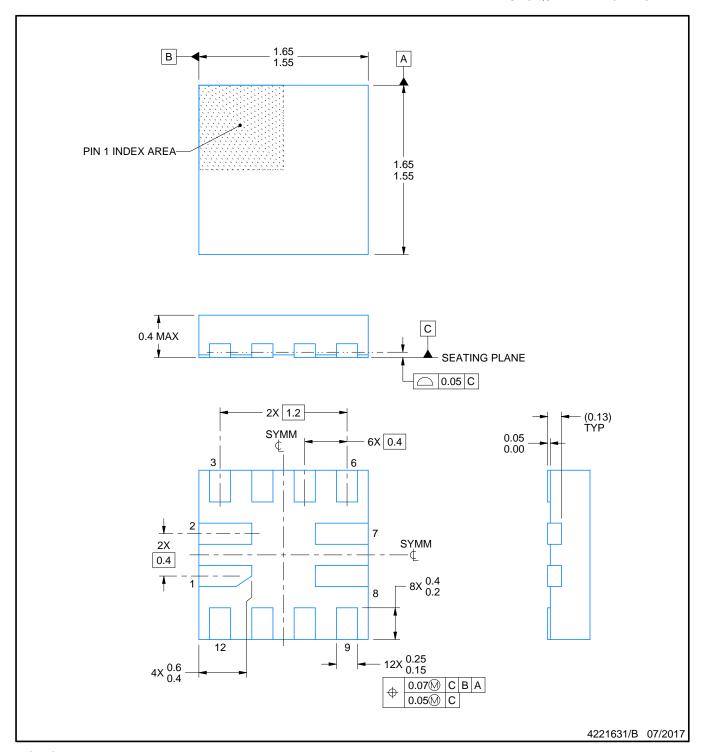

#### **Device Information**

| PART NUMBER(1) | PACKAGE <sup>(2)</sup> | OP TEMP (T <sub>A</sub> ) °C | PACKAGE SIZE(3) |

|----------------|------------------------|------------------------------|-----------------|

| TUSB216        |                        | 0 to 70                      |                 |

| TUSB216I       | RWB (X2QFN, 12)        | -40 to 85                    | 1.6 mm × 1.6 mm |

| TUSB216-Q1     |                        | -40 to 105                   |                 |

- See Device Comparison

- For more information, see Section 11.

- The package size (length × width) is a nominal value and includes pins, where applicable.

Simplified Schematic

# **Table of Contents**

| 1 Features                           | 1        | 7.4 Device Functional Modes                         | 9  |

|--------------------------------------|----------|-----------------------------------------------------|----|

| 2 Applications                       | 1        | 7.5 TUSB216 Registers                               | 10 |

| 3 Description                        |          | 8 Application and Implementation                    | 14 |

| 4 Device Comparison                  | <b>2</b> | 8.1 Application Information                         | 14 |

| 5 Pin Configuration and Functions    | 3        | 8.2 Typical Application                             | 14 |

| 6 Specifications                     | 5        | 8.3 Power Supply Recommendations                    | 22 |

| 6.1 Absolute Maximum Ratings         |          | 8.4 Layout                                          |    |

| 6.2 ESD Ratings                      | 5        | 9 Device and Documentation Support                  |    |

| 6.3 Recommended Operating Conditions |          | 9.1 Receiving Notification of Documentation Updates | 32 |

| 6.4 Thermal Information              | 5        | 9.2 Support Resources                               | 23 |

| 6.5 Electrical Characteristics       | 6        | 9.3 Trademarks                                      |    |

| 6.6 Switching Characteristics        | 7        | 9.4 Electrostatic Discharge Caution                 |    |

| 6.7 Timing Requirements              | 8        | 9.5 Glossary                                        |    |

| 7 Detailed Description               |          | 10 Revision History                                 |    |

| 7.1 Overview                         |          | 11 Mechanical, Packaging, and Orderable             |    |

| 7.2 Functional Block Diagram         | 9        | Information                                         | 23 |

| 7.3 Feature Description              |          |                                                     |    |

# **4 Device Comparison**

|                                                                                                                                                           | TUSB211A                                                         | TUSB212     | TUSB214     | TUSB216                                                          | TUSB217A                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------|-------------|------------------------------------------------------------------|------------------------------------------------------------------|

| Industrial Variant Available                                                                                                                              | Υ                                                                | Υ           | Υ           | Υ                                                                | Υ                                                                |

| Automotive Variant Available                                                                                                                              | Υ                                                                | Υ           | Υ           | Υ                                                                | Υ                                                                |

| Supply (V)                                                                                                                                                | 2.3 to 6.5                                                       | 3.3         | 3.3         | 2.3 to 6.5                                                       | 2.3 to 6.5                                                       |

| DC Boost                                                                                                                                                  | Tandem with AC<br>Boost                                          | 3 levels    | 3 levels    | Tandem with AC<br>Boost                                          | Tandem with AC<br>Boost                                          |

| I2C Control                                                                                                                                               | N                                                                | Υ           | Υ           | Υ                                                                | Υ                                                                |

| RX pre-equalization for ISI compensation                                                                                                                  | N/A                                                              | N/A         | N/A         | 3 levels                                                         | 3 levels                                                         |

| Charging Downstream Port (CDP) controller                                                                                                                 | N/A                                                              | N/A         | Always ON   | Pin Controlled                                                   | Always ON.<br>Dynamically<br>selected by<br>DCP/CDP pin          |

| Dedicated Charging Port (DCP) controller                                                                                                                  | N/A                                                              | N/A         | N/A         | N/A                                                              | Always ON.<br>Dynamically<br>selected by<br>DCP/CDP pin          |

| Cable length compensation for near-end high-speed eye mask Compliance (pre-channel before redriver/post-channel after redriver) (meter - gauge)           | 6/3 - 28AWG (10<br>- 24AWG with one<br>redriver on each<br>end)  | 4/2 - 28AWG | 4/2 - 28AWG | 6/3 - 28AWG (10<br>- 24AWG with one<br>redriver on each<br>end)  | 6/3 - 28AWG (10<br>- 24AWG with one<br>redriver on each<br>end)  |

| Cable length compensation for far-<br>end high-speed eye mask Compliance<br>(pre-channel before redriver/post-<br>channel after redriver) (meter - gauge) | 10/8 - 26AWG (10<br>- 28AWG with one<br>redriver on each<br>end) | 8/6 - 28AWG | 8/6 - 28AWG | 10/8 - 26AWG (10<br>- 28AWG with one<br>redriver on each<br>end) | 10/8 - 26AWG (10<br>- 28AWG with one<br>redriver on each<br>end) |

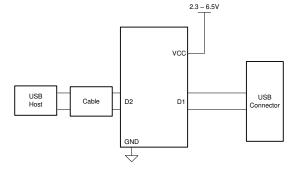

# **5 Pin Configuration and Functions**

Figure 5-1. TUSB216I RWB Package, 12-Pin X2QFN (Top View)

**Table 5-1. Pin Functions**

| PIN                           |    | TYPE(1) INTERNAL |                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------|----|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO.                      |    | ITPE\"           | PULLUP/PULLDOWN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BOOST                         | 6  | I                | N/A             | USB High-speed boost select via external pull down resistor. Both edge boost and DC boost are controlled by a single pin in non-<br>I2C mode. In I2C mode edge boost and DC boost can be individually controlled. Sampled upon power up. Does not recognize real time adjustments. Auto selects BOOST LEVEL = 3 when left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CDP_ENZ                       | 11 | I                | 500 kΩ PU       | Set CDP_ENZ is low to enable BC 1.2 CDP controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RX_SEN <sup>(3)</sup> /ENA_HS | 9  | l/O              | N/A             | In I2C mode: Reserved for TI test purpose. In non-I2C mode: At reset: 3-level input signal RX_SEN. USB High-speed RX Sensitivity Setting to Compensate ISI Jitter H (pin is pulled high) – high RX sensitivity (high loss channel) M (pin is left floating) – medium RX sensitivity (medium loss channel) L (pin is pulled low) – low RX sensitivity (low loss channel) After reset: Output signal ENA_HS. Flag indicating that channel is in High-speed mode. Asserted upon: 1. Detection of USB-IF High-speed test fixture from an unconnected state followed by transmission of USB TEST_PACKET pattern. 2. Squelch detection following USB reset with a successful HS handshake [HS handshake is declared to be successful after single chirp J chirp K pair where each chirp is within 18 µs – 128 µs]. |

| D2P                           | 7  | I/O              | N/A             | USB High-speed positive port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# **Table 5-1. Pin Functions (continued)**

| PIN                    |    | TVDE(1)         | INTERNAL                                | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|------------------------|----|-----------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO.               |    | PULLUP/PULLDOWN |                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                |

| D2M                    | 8  | I/O             | N/A                                     | USB High-speed negative port.                                                                                                                                                                                                                                                                              |

| GND                    | 10 | Р               | N/A                                     | Ground                                                                                                                                                                                                                                                                                                     |

| D1M                    | 1  | I/O             | N/A                                     | USB High-speed negative port                                                                                                                                                                                                                                                                               |

| D1P                    | 2  | I/O             | N/A                                     | USB High-speed positive port.                                                                                                                                                                                                                                                                              |

| SDA <sup>(2)</sup>     | 3  | I/O             | 500 kΩ PU<br>1.8 MΩ PD                  | I2C Mode: Bidirectional I2C data pin [7-bit I2C slave address = 0x2C]. In non I2C mode: Reserved for TI test purpose.                                                                                                                                                                                      |

| VCC                    | 12 | Р               | N/A                                     | Supply power                                                                                                                                                                                                                                                                                               |

| RSTN                   | 5  | I               | 500 kΩ PU<br>1.8 MΩ PD                  | Device disable/enable.  Low – Device is at reset and in shutdown, and  High - Normal operation.  Recommend 0.1-µF external capacitor to GND to ensure clean power on reset if not driven. If the pin is driven, it must be held low until the supply voltage for the device reaches within specifications. |

| SCL <sup>(2)</sup> /CD | 4  | 1/0             | When RSTN asserted there is a 500 kΩ PD | In I2C mode: I2C clock pin [I2C address = 0x2C]. Non I2C mode: After reset: Output CD. Flag indicating that a USB device is attached (connection detected). Asserted from an unconnected state upon detection of DP or DM pull-up resistor. De-asserted upon detection of disconnect.                      |

- (1) I = input, O = output, P = power

- (2) Pull-up resistors for SDA and SCL pins in I<sup>2</sup>C mode should be R<sub>Pull-up</sub> (depending on I2C bus voltage). If both SDA and SCL are pulled up at power-up the device enters into I<sup>2</sup>C mode.

- (3) Pull-down and pull-up resistors for RX\_SEN pin must follow R<sub>RXSEN1</sub> and R<sub>RXSEN2</sub> resistor recommendations in non I<sup>2</sup>C mode.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                 | MIN  | MAX  | UNIT |

|---------------------------------------|---------------------------------|------|------|------|

| Supply voltage range                  | VCC                             | -0.3 | 7    | V    |

| Voltage range USB data                | DxP, DxM                        | -0.3 | 5.5  | V    |

| Voltage range on BOOST pin            | BOOST                           | -0.3 | 1.98 | V    |

| Voltage range other pins              | RX_SEN, CDP_ENZ, SDA, SCL, RSTN | -0.3 | 5.5  | V    |

| Storage temperature, T <sub>stg</sub> |                                 | -65  | 150  | °C   |

| Maximum junction temperature, T       | J (max)                         | 125  |      | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                                            |                                                                   |                                                                       | VALUE | UNIT     |

|--------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|-------|----------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                                 | V     |          |

|                                            | Electrostatic discriarge                                          | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±750  | <b>v</b> |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                      |                                                    | MIN  | NOM | MAX  | UNIT |

|----------------------|----------------------------------------------------|------|-----|------|------|

| V <sub>CC</sub>      | Supply voltage                                     | 2.3  | 5   | 6.5  | V    |

| T <sub>A</sub>       | Operating free-air temperature (Industrial)        | -40  |     | 85   | °C   |

| TJ                   | Junction temperature (Industrial)                  |      |     | 105  | °C   |

| V <sub>I2C_BUS</sub> | I2C Bus Voltage                                    | 1.62 |     | 3.6  | V    |

| DxP, DxM             | Voltage range USB data                             | 0    |     | 3.6  | V    |

| BOOST                | Voltage range BOOST pin                            | 0    |     | 1.98 | V    |

| DIGITAL              | Voltage range other pins (SCL, SDA, RSTN, CDP_ENZ) | 0    |     | 3.6  | V    |

| RX_SEN               | Voltage range RX_SEN pin                           | 0    |     | 5.0  | V    |

### 6.4 Thermal Information

|                        | THERMAL METRIC (1)                           |       | LIMIT |

|------------------------|----------------------------------------------|-------|-------|

|                        |                                              |       | UNIT  |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 137.4 | °C/W  |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 62    | °C/W  |

| R <sub>0JB</sub>       | Junction-to-board thermal resistance         | 67.2  | °C/W  |

| ΨЈТ                    | Junction-to-top characterization parameter   | 1.9   | °C/W  |

| ΨЈВ                    | Junction-to-board characterization parameter | 67.3  | °C/W  |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | N/A   | °C/W  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# **6.5 Electrical Characteristics**

Over operating free-air temperature range (unless otherwise noted)

|                          | PARAMETER                                                                                                        | TEST CONDITIONS                                                                          | MIN | TYP (1) | MAX  | UNIT     |

|--------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|---------|------|----------|

| POWER                    |                                                                                                                  |                                                                                          |     |         |      |          |

| I <sub>ACTIVE_HS</sub>   | High Speed Active Current                                                                                        | USB channel = HS mode. 480 Mbps traffic. V <sub>CC</sub> supply stable, with Boost = Max |     | 22      | 36   | mA       |

| I <sub>IDLE_HS</sub>     | High Speed Idle Current                                                                                          | USB channel = HS mode, no traffic.  V <sub>CC</sub> supply stable, Boost = Max           |     | 22      | 36   | mA       |

| I <sub>HS_SUPSPEND</sub> | High Speed Suspend Current                                                                                       | USB channel = HS Suspend mode. V <sub>CC</sub> supply stable                             |     | 0.75    | 1.4  | mA       |

| I <sub>FS</sub>          | Full-Speed Current                                                                                               | USB channel = FS mode, 12 Mbps traffic, V <sub>cc</sub> supply stable                    |     | 0.75    | 1.4  | mA       |

| I <sub>DISCONN</sub>     | Disconnect Power                                                                                                 | Host side application. No device attachment.                                             |     | 0.80    | 1.4  | mA       |

| I <sub>SHUTDN</sub>      | Shutdown Power                                                                                                   | RSTN driven low, V <sub>CC</sub> supply stable                                           |     | 60      | 115  | μA       |

| CONTROL PIN LE           | EAKAGE                                                                                                           |                                                                                          |     |         |      |          |

| I <sub>LKG_FS</sub>      | Pin failsafe leakage current for SDA, RSTN                                                                       | V <sub>CC</sub> = 0 V, pin at V <sub>IH, max</sub>                                       |     | 10      | 15   | μA       |

| I <sub>LKG_FS</sub>      | Pin failsafe leakage current for RX_SEN                                                                          | V <sub>CC</sub> = 0 V, pin at V <sub>IH, max</sub>                                       |     | 6       | 15   | μA       |

| I <sub>LKG_FS</sub>      | Pin failsafe leakage current for SCL                                                                             | V <sub>CC</sub> = 0 V, pin at V <sub>IH, max</sub>                                       |     |         | 70   | nA       |

| INPUT RSTN               |                                                                                                                  | ,                                                                                        |     |         |      |          |

| V <sub>IH</sub>          | High level input voltage                                                                                         |                                                                                          | 1.5 |         | 3.6  | V        |

| V <sub>IL</sub>          | Low-level input voltage                                                                                          |                                                                                          | 0   |         | 0.5  | V        |

| I <sub>IH</sub>          | High level input current                                                                                         | V <sub>IH</sub> = 3.6 V, R <sub>PU</sub> enabled                                         |     |         | ±15  | μA       |

| I <sub>IL</sub>          | Low level input current                                                                                          | V <sub>IL</sub> = 0V, R <sub>PU</sub> enabled                                            |     |         | ±20  | μA       |

| INPUT DIGITAL            | ·                                                                                                                |                                                                                          |     |         |      | <u> </u> |

| V <sub>IH</sub>          | High level input voltage (CDP_ENZ)                                                                               |                                                                                          | 1.5 |         | 3.6  | V        |

| V <sub>IL</sub>          | Low-level input voltage (CDP_ENZ)                                                                                |                                                                                          | 0   |         | 0.5  | V        |

| I <sub>IL</sub>          | Low level input current                                                                                          | V <sub>IL</sub> = 0V                                                                     |     |         | ±20  | μA       |

| I <sub>IH</sub>          | High level input current                                                                                         | V <sub>IH</sub> = 3.6 V                                                                  |     |         | ±15  | μA       |

| INPUT RX_SEN (           | 3-level input, for mid level leave pin f                                                                         | loating)                                                                                 |     |         |      |          |

| V <sub>IH(Max)</sub>     | Maximum High level input voltage                                                                                 | VCC = 2.3V to 6.5V                                                                       |     |         | 5.0  | ٧        |

|                          |                                                                                                                  | VCC > 4.5V                                                                               | 3.3 |         |      | V        |

| $V_{IH(Min)}$            | Minimum High level input voltage                                                                                 | VCC = 2.3V to 4.5V (% of VCC)                                                            | 75  |         |      | %        |

|                          |                                                                                                                  | VCC > 4.5V                                                                               |     |         | 0.75 | V        |

| $V_{IL}$                 | Low level input voltage                                                                                          | VCC = 2.3V to 4.5V (% of VCC)                                                            |     |         | 15   | %        |

| INPUT BOOST              | 1                                                                                                                | 1                                                                                        |     |         |      |          |

| R <sub>BOOST_LVL0</sub>  | External pulldown resistor for BOOST Level 0                                                                     |                                                                                          |     |         | 160  | Ω        |

| R <sub>BOOST_LVL1</sub>  | External pulldown resistor for BOOST Level 1                                                                     |                                                                                          | 1.5 | 1.8     | 2    | kΩ       |

| R <sub>BOOST_LVL2</sub>  | External pulldown resistor for BOOST Level 2                                                                     |                                                                                          | 3.4 | 3.6     | 3.96 | kΩ       |

| R <sub>BOOST_LVL3</sub>  | External pulldown resistor for<br>BOOST Level 3 to remove upper<br>limit for resistor value, can be left<br>open |                                                                                          | 7.5 |         |      | kΩ       |

| OUTPUTS CD, EN           | NA_HS                                                                                                            |                                                                                          |     |         |      |          |

| V <sub>OH</sub>          | High level output voltage for CD and ENA_HS                                                                      | I <sub>O</sub> = -50 μA, VCC >= 3.0V                                                     | 2.5 |         |      | V        |

| V <sub>OH</sub>          | High level output voltage for CD                                                                                 | I <sub>O</sub> = -25 μA, VCC = 2.3V                                                      | 1.7 |         |      | V        |

Product Folder Links: TUSB216I

Submit Document Feedback

# **6.5 Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                             | TEST CONDITIONS                                                           | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------------------|-----|--------------------|-----|------|

| V <sub>OH</sub>      | High level output voltage for ENA_HS                  | I <sub>O</sub> = -25 μA, VCC = 2.3V                                       | 1.8 |                    |     | V    |

| V <sub>OL</sub>      | Low level output voltage for CD and ENA_HS            | Ι <sub>Ο</sub> = 50 μΑ                                                    |     |                    | 0.3 | V    |

| 12C                  | ·                                                     |                                                                           |     |                    | '   |      |

| C <sub>I2C_BUS</sub> | I <sup>2</sup> C Bus Capacitance                      |                                                                           | 4   |                    | 150 | pF   |

| I <sub>OL</sub>      | I <sup>2</sup> C open drain output current            | V <sub>OL</sub> = 0.4V                                                    | 1.5 |                    |     | mA   |

| V <sub>IL</sub>      | 2.3V<= VCC<= 4.3V, V <sub>I2C_BUS</sub> = 1.8V +/-10% | $R_{Pull-up}$ =1.6kΩ to 2.5kΩ, % of $V_{I2C\_BUS}$                        |     |                    | 25  | %    |

| V <sub>IL</sub>      | V <sub>I2C_BUS</sub> = 3.3V +/-10%                    | $R_{Pull-up}$ =2.8kΩ to 7kΩ, % of $V_{I2C\_BUS}$                          |     |                    | 25  | %    |

| V <sub>IH</sub>      | 2.3V<= VCC<= 4.3V, V <sub>I2C_BUS</sub> = 1.8V +/-10% | $R_{Pull-up}$ =1.6kΩ to 2.5kΩ, % of $V_{I2C\_BUS}$                        | 80  |                    |     | %    |

| V <sub>IH</sub>      | V <sub>I2C_BUS</sub> = 3.3V +/-10%                    | $R_{Pull-up}$ =2.8kΩ to 7kΩ, % of $V_{I2C\_BUS}$                          | 75  |                    |     | %    |

| R <sub>Pull-up</sub> | V <sub>I2C_BUS</sub> = 1.8V +/-10%                    |                                                                           | 1.6 | 2                  | 2.5 | kΩ   |

| R <sub>Pull-up</sub> | V <sub>I2C_BUS</sub> = 3.3V +/-10%                    |                                                                           | 2.8 | 4.7                | 7   | kΩ   |

| SCL Frequency        |                                                       |                                                                           |     |                    | 400 | kHz  |

| DxP, DxM             |                                                       |                                                                           |     |                    |     |      |

| C <sub>IO_DXX</sub>  | Capacitance to GND                                    | Measured with VNA at 240 MHz, V <sub>CC</sub> supply stable, Redriver off |     | 2.5                |     | pF   |

<sup>(1)</sup> All typical values are at  $V_{CC}$  = 5 V, and  $T_A$  = 25°C.

# **6.6 Switching Characteristics**

Over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER      | TEST CONDITIONS                                                        | MIN | TYP <sup>(1)</sup> | MAX | UNIT |  |

|----------------------|----------------|------------------------------------------------------------------------|-----|--------------------|-----|------|--|

| DxP, DxM USB Signals |                |                                                                        |     |                    |     |      |  |

| F <sub>BR_DXX</sub>  | Bit Rate       | USB channel = HS mode. 480 Mbps traffic. V <sub>CC</sub> supply stable |     |                    | 480 | Mbps |  |

| t <sub>R/F_DXX</sub> | Rise/Fall time |                                                                        | 100 |                    |     | ps   |  |

<sup>(1)</sup> All typical values are at  $V_{CC}$  = 5 V, and  $T_A$  = 25°C.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# **6.7 Timing Requirements**

|                      |                                                                                                                                 | MIN | NOM MAX | UNIT |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|

| POWER U              | P TIMING                                                                                                                        |     |         | •    |

| T <sub>RSTN_PW</sub> | Minimum width to detect a valid RSTN signal assert when the pin is actively driven low                                          | 100 |         | μs   |

| T <sub>STABLE</sub>  | VCC must be stable before RSTN de-assertion                                                                                     | 300 |         | μs   |

| T <sub>READY</sub>   | Maximum time needed for the device to be ready after RSTN is deasserted.                                                        |     | 50      | ) µs |

| T <sub>RAMP</sub>    | V <sub>CC</sub> ramp time                                                                                                       |     | 10      | ) ms |

| T <sub>RAMP</sub>    | V <sub>CC</sub> ramp time                                                                                                       | 0.2 |         | ms   |

| I2C (STD)            |                                                                                                                                 | ,   |         |      |

| t <sub>susto</sub>   | Stop setup time, SCL ( $T_r$ =600ns-1000ns), SDA ( $T_f$ =6.5ns-106.5ns), 100kHz STD                                            | 4   |         | μs   |

| t <sub>HDSTA</sub>   | Start hold time, SCL (Tr=600ns-1000ns), SDA (Tf=6.5ns-106.5ns), 100kHz STD                                                      | 4   |         | μs   |

| t <sub>SUSTA</sub>   | Start setup time, SCL ( $T_r$ =600ns-1000ns), SDA ( $T_f$ =6.5ns-106.5ns), 100kHz STD                                           | 4.7 |         | μs   |

| t <sub>SUDAT</sub>   | Data input or False start/stop, setup time, SCL (T <sub>r</sub> =600ns-1000ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 100kHz STD | 250 |         | ns   |

| t <sub>HDDAT</sub>   | Data input or False start/stop, hold time, SCL (T <sub>r</sub> =600ns-1000ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 100kHz STD  | 5   |         | μs   |

| t <sub>BUF</sub>     | Bus free time between START and STOP conditions                                                                                 | 4.7 |         | μs   |

| t <sub>LOW</sub>     | Low period of the I2C clock                                                                                                     | 4.7 |         | μs   |

| t <sub>HIGH</sub>    | High period of the I2C clock                                                                                                    | 4   |         | μs   |

| t <sub>F</sub>       | Fall time of both SDA and SCL signals                                                                                           |     | 30      | ) ns |

| t <sub>R</sub>       | Rise time of both SDA and SCL signals                                                                                           |     | 100     | ) ns |

| I2C (FM)             |                                                                                                                                 |     |         | '    |

| t <sub>SUSTO</sub>   | Stop setup time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM                             | 0.6 |         | μs   |

| t <sub>HDSTA</sub>   | Start hold time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM                             | 0.6 |         | μs   |

| t <sub>SUSTA</sub>   | Start setup time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM                            | 0.6 |         | μs   |

| t <sub>SUDAT</sub>   | Data input or False start/stop, setup time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM  | 100 |         | ns   |

| t <sub>HDDAT</sub>   | Data input or False start/stop, hold time, SCL (T <sub>r</sub> =180ns-300ns), SDA (T <sub>f</sub> =6.5ns-106.5ns), 400 kHz FM   | 0   |         | μs   |

| t <sub>BUF</sub>     | Bus free time between START and STOP conditions                                                                                 | 1.3 |         | μs   |

| t <sub>LOW</sub>     | Low period of the I2C clock                                                                                                     | 1.3 |         | μs   |

| t <sub>HIGH</sub>    | High period of the I2C clock                                                                                                    | 0.6 |         | μs   |

| t <sub>F</sub>       | Fall time of both SDA and SCL signals                                                                                           | ,   | 30      | ) ns |

| t <sub>R</sub>       | Rise time of both SDA and SCL signals                                                                                           |     | 30      | ) ns |

# 7 Detailed Description

#### 7.1 Overview

The TUSB216I is a USB High-Speed (HS) signal conditioner designed to compensate for ISI signal loss in a transmission channel. TUSB216I has a patented design for USB Low Speed (LS) and Full Speed (FS) signals. It does not alter the signal characteristics. HS signals are compensated. The design is compatible with USB On-The-Go (OTG) and Battery Charging (BC) specifications.

Programmable signal gain through an external resistor permits fine tuning device performance to optimize signals. This helps pass USB HS electrical compliance tests at the connector. Additional RX sensitivity, tuned by external pull-up resistor and pull-down resistor, allows to overcome attenuation in cables. The TUSB216I allows application in series to cover longer distances, or high loss transmission paths. A maximum of 4 devices can be daisy-chained.

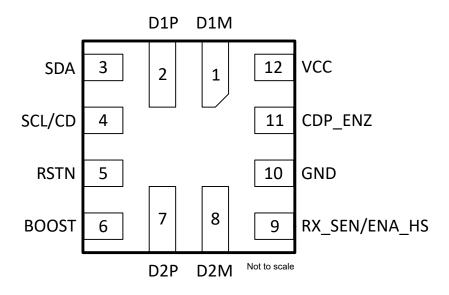

### 7.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

# 7.3 Feature Description

#### 7.3.1 High-Speed Boost

The high-speed booster (combination of edge boost and DC boost) improves the eye width for USB2.0 high-speed signals. It is direction independent and by that is compatible to OTG systems. The BOOST pin is configuring the booster strength with different values of pull down resistors to set 4 levels of boosts, alternatively the boost level can be set through the I2C register according to Section 7.4.6. Internal circuitry of the signal conditioner reduces possible overshoot.

#### 7.3.2 RX Sensitivity

The RX\_SEN pin is a tri-level pin. It is used to set the gain of the device according to system channel loss. RX sensitivity can be increased to recover incoming signals with low vertical eye opening to be able to boost weak signals and helps overcoming high attenuation.

# 7.4 Device Functional Modes

### 7.4.1 Low-Speed (LS) Mode

TUSB216I automatically detects a LS connection and does not enable signal compensation. CD pin is asserted high but ENA\_HS will be low.

## 7.4.2 Full-Speed (FS) Mode

TUSB216I automatically detects a FS connection and does not enable signal compensation. CD pin is asserted high but ENA HS will be low

#### 7.4.3 High-Speed (HS) Mode

TUSB216I automatically detects a HS connection and will enable signal compensation as determined by the configuration of the RX\_SEN pin and the external pull down resistance on its BOOST pin.

CD pin and ENA HS pin are asserted high when high-speed boost is active.

#### 7.4.4 High-Speed Downstream Port Electrical Compliance Test Mode

TUSB216I will detect HS compliance test fixture and enter downstream port high-speed eye diagram test mode. CD pin will be low and ENA\_HS pin is asserted high when TUSB216I is in HS eye compliance test mode.

If RSTN pin is asserted low and de-asserted high while TUSB216I is operating in HS functional mode, TUSB216I will transition to HS eye compliance test mode and CD asserts low and ENA\_HS remains high. When this occurs signal compensation is enabled.

#### 7.4.5 Shutdown Mode

TUSB216I can be disabled when its RSTN pin is asserted low. DP, DM traces are continuous through the device in shutdown mode. The USB channel is still fully operational, but there is neither signal compensation, nor any indication from the CD pin as to the status of the channel.

Table 7-1. CD and ENA\_HS Pins in Different Modes

| MODE                                       | CD   | ENA_HS |

|--------------------------------------------|------|--------|

| Low-speed                                  | HIGH | LOW    |

| Full-speed                                 | HIGH | LOW    |

| High-speed                                 | HIGH | HIGH   |

| High-speed downstream port electrical test | LOW  | HIGH   |

| Shutdown                                   | LOW  | LOW    |

#### 7.4.6 I<sup>2</sup>C Mode

TUSB216I supports 100 and 400 kHz I2C for device configuration, status read back and test purposes. For detail electrical and functional specifications refer to I2C Bus Specification – STANDARD and FAST MODE. This controller is enabled after SCL and SDA pins are sampled high shortly after return from shutdown. In this mode, the CSR can be accessed by I2C read/write transaction to 7-bit slave address 0x2C. It is advised to set CFG\_ACTIVE bit before changing values. This halts the FSM, and reset it after all changes are made. This ensure proper startup into high-speed mode.

### 7.4.7 BC 1.2 Battery Charging Controller

The TUSB216I main function is a signal conditioner offering the boost and pre-equalization features to the incoming DP/DM signals. For applications in which USB host or hub does not provide USB BC charging controller functionality, the TUSB216I can perform this task when CDP\_ENZ is low and BC 1.2 CDP Controller is enabled. When battery charging CDP controller feature is enabled (CDP\_ENZ=low) TUSB216I supports CDP charging downstream port functionality. CDP\_ENZ has an internal pull up when the pin is left unconnected CDP controller will be disabled.

Table 7-2. TUSB216I Battery Charging Controller Modes

| Pin 11 (CDP_ENZ) | CDP |

|------------------|-----|

| High             | NO  |

| Low              | YES |

#### 7.5 TUSB216 Registers

Submit Document Feedback

Table 7-3 lists the memory-mapped registers for the TUSB216 registers. All register offset addresses not listed in Table 7-3 should be considered as reserved locations and the register contents should not be modified.

Table 7-3. TUSB216 Registers

| Offset | Acronym       | Register Name                                  | Section |

|--------|---------------|------------------------------------------------|---------|

| 0x1    | EDGE_BOOST    | This register is setting EDGE BOOST level.     | Go      |

| 0x3    | CONFIGURATION | This register is selecting device mode.        | Go      |

| 0xE    | DC_BOOST      | This register is setting DC BOOST level.       | Go      |

| 0x25   | RX_SEN        | This register is setting RX Sensitivity level. | Go      |

Complex bit access types are encoded to fit into small table cells. Table 7-4 shows the codes that are used for access types in this section.

Table 7-4. TUSB216 Access Type Codes

| Access Type      | Code   | Description                            |

|------------------|--------|----------------------------------------|

| Read Type        |        |                                        |

| RH               | H<br>R | Set or cleared by hardware<br>Read     |

| Write Type       |        |                                        |

| W                | W      | Write                                  |

| Reset or Default | Value  |                                        |

| -n               |        | Value after reset or the default value |

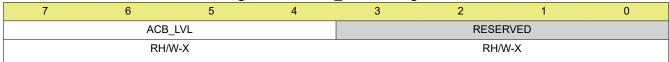

# 7.5.1 EDGE\_BOOST Register (Offset = 0x1) [reset = X]

EDGE\_BOOST is shown in Figure 7-1 and described in Table 7-5.

Return to Summary Table.

This register is setting EDGE BOOST level.

Figure 7-1. EDGE\_BOOST Register

Table 7-5. EDGE\_BOOST Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                         |

|-----|----------|------|-------|---------------------------------------------------------------------|

| 7-4 | ACB_LVL  | RH/W | X     | XXXXb (sampled at startup from BOOST pin)                           |

|     |          |      |       | 0000b to 1111b range                                                |

|     |          |      |       | 0x0 = BOOST PIN LEVEL 0 (lowest edge boost setting)                 |

|     |          |      |       | 0x3 = BOOST PIN LEVEL 1                                             |

|     |          |      |       | 0x6 = BOOST PIN LEVEL 2                                             |

|     |          |      |       | 0xA = BOOST PIN LEVEL 3                                             |

|     |          |      |       | 0xF = (highest edge boost setting)                                  |

| 3-0 | RESERVED | RH/W | Х     | These bits are reserved bits and set by hardware at reset.          |

|     |          |      |       | When this register is modified the software should first read these |

|     |          |      |       | reserved bits and rewrite with the same values                      |

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: TUSB216/

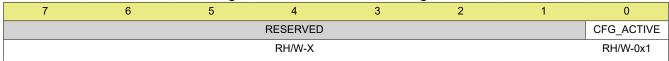

# 7.5.2 CONFIGURATION Register (Offset = 0x3) [reset = X]

CONFIGURATION is shown in Figure 7-2 and described in Table 7-6.

Return to Summary Table.

This register is selecting device mode.

### Figure 7-2. CONFIGURATION Register

#### Table 7-6, CONFIGURATION Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                                                                                                                                                                        |

|-----|------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1 | RESERVED   | RH/W | Х     | These bits are reserved bits and set by hardware at reset.  When this register is modified the software should first read these reserved bits and rewrite with the same values                                     |

| 0   | CFG_ACTIVE | RH/W | 0x1   | Configuration mode After reset, if I2C mode is true (SCL and SDA are both pulled high) set the bit to get into configuration mode and clear to return to normal mode.  0x0 = NORMAL MODE  0x1 = CONFIGURATION MODE |

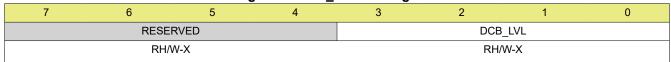

# 7.5.3 DC\_BOOST Register (Offset = 0xE) [reset = X]

DC\_BOOST is shown in Figure 7-3 and described in Table 7-7.

Return to Summary Table.

This register is setting DC BOOST level.

### Figure 7-3. DC\_BOOST Register

# Table 7-7. DC\_BOOST Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                 |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | RESERVED | RH/W | X     | These bits are reserved bits and set by hardware at reset.  When this register is modified the software should first read these reserved bits and rewrite with the same values                              |

| 3-0 | DCB_LVL  | RH/W | X     | XXXXb (sampled at startup from BOOST pin) 0000b to 1111b range  0x0 = BOOST PIN LEVEL 0 (lowest dc boost setting)  0x2 = BOOST PIN LEVEL 1 and 2  0x6 = BOOST PIN LEVEL 3  0xF = (highest dc boost setting) |

# 7.5.4 RX\_SEN Register (Offset = 0x25) [reset = X]

RX\_SEN is shown in Figure 7-4 and described in Table 7-8.

Return to Summary Table.

This register is setting RX Sensitivity level.

# Figure 7-4. RX\_SEN Register

# Table 7-8. RX\_SEN Register Field Descriptions

| Bit | Field  | Туре | Reset | Description                                |

|-----|--------|------|-------|--------------------------------------------|

| 7-0 | RX_SEN | RH/W | X     | XXXXb (sampled at startup from RX_SEN pin) |

|     |        |      |       | 0000000b to 11111111b range                |

|     |        |      |       | 0x0 = RX_SEN LEVEL LOW                     |

|     |        |      |       | 0x33 = RX_SEN LEVEL MID                    |

|     |        |      |       | 0x66 = RX_SEN LEVEL HIGH                   |

|     |        |      |       | 0xFF = (highest setting)                   |

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: *TUSB216I*

# 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 8.1 Application Information

The purpose of the TUSB216I is to re-store the signal integrity of a USB High-speed channel up to the USB connector. The loss in signal quality stems from reduced channel bandwidth due to high loss PCB trace and other components that contribute a capacitive load. This can cause the channel to fail the USB near end eye mask. Proper use of the TUSB216I can help to pass this eye mask.

A secondary purpose is to use the CD pin of the TUSB216I to control other blocks on the customer platform, if so desired.

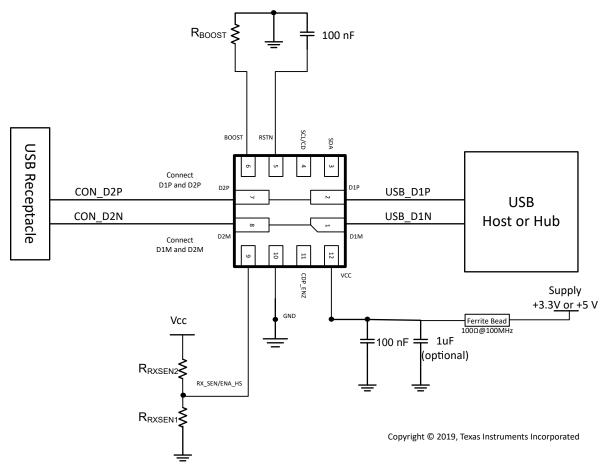

# 8.2 Typical Application

A typical application for TUSB216I is shown in Figure 8-1. In this setup, D2P and D2M face the USB connector while D1P and D1M face the USB host. The orientation may be reversed [that is, D2 faces transceiver and D1 faces connector].

Figure 8-1. TUSB216I Reference Schematic (Design Example with CDP disabled), CDP\_ENZ Can Be Left Floating but an Option for a Decoupling Capacitor of 0.1 μF is Recommended So the Design is Compatible with Older Devices: TUSB211, TUSB212, TUSB214

# 8.2.1 Design Requirements

TUSB216I requires a valid reset signal as described in the *Power Supply Recommendations* section. The capacitor at RSTN pin is not required if a micro controller drives the RSTN pin according to recommendations.

For this design example, use the parameters shown in Table 8-1, Table 8-2 and Table 8-3.

Table 8-1. Design Parameters for 5-V Supply With High Loss System

|                                  | 14510 0 11 2001911 1 41411    | ictors for a v dapping vittin | mgn zeec cyclem | VALUE <sup>(1)</sup>                                |  |

|----------------------------------|-------------------------------|-------------------------------|-----------------|-----------------------------------------------------|--|

| PARAMETER                        |                               |                               |                 |                                                     |  |

| V <sub>CC</sub>                  |                               |                               |                 | 5 V ±10%                                            |  |

| I <sup>2</sup> C support require | ed in system (Yes/No)         |                               |                 | No                                                  |  |

|                                  | BOOST Level                   |                               |                 |                                                     |  |

|                                  |                               | 0-Ω                           | 0               |                                                     |  |

| Edge and DC Boo                  | est                           | 1.8 kΩ ±1%                    | 1               | Boost Level 1:<br>$R_{BOOST} = 1.8 \text{ k}\Omega$ |  |

|                                  |                               | 3.6 kΩ ± 1%                   | 2               | 1,80021 1.0 1.22                                    |  |

|                                  |                               | Do Not Install (DNI)          | 3               |                                                     |  |

|                                  | R <sub>RXSEN1</sub>           | R <sub>RXSEN2</sub>           | RX_SEN Level    | High RX                                             |  |

|                                  | 22 kΩ - 40 kΩ (27 kΩ typical) | Do Not Install (DNI)          | Low             | Sensitivity Level:  R <sub>RXSEN1</sub> = 37.5      |  |

| RX Sensitivity                   | Do Not Install (DNI)          | Do Not Install (DNI)          | Medium          | kΩ                                                  |  |

|                                  | 37.5 kΩ <sup>(2)</sup>        | 12.5 kΩ                       | High            | $R_{RXSEN2}$ = 12.5 $kΩ$                            |  |

<sup>(1)</sup> These parameters are starting values for a high loss system. Further tuning might be required based on specific host or device as well as cable length and loss profile. These settings are not specific to a 5 V supply system could be applicable to 3.3 V supply system as well.

Table 8-2. Design Parameters for 3.3-V Supply With Low to Medium Loss System

| PARAMETER                        |                               |                               |              |                                                 |  |

|----------------------------------|-------------------------------|-------------------------------|--------------|-------------------------------------------------|--|

| V <sub>CC</sub>                  |                               |                               |              | 3.3 V ±10%                                      |  |

| I <sup>2</sup> C support require | ed in system (Yes/No)         |                               |              | No                                              |  |

|                                  |                               | R <sub>BOOST</sub>            | BOOST Level  |                                                 |  |

|                                  |                               | 0-Ω                           | 0            |                                                 |  |

| Edge and DC Boos                 | st                            | 1.8 kΩ ±1%                    | 1            | Boost Level 0:<br>$R_{BOOST} = 0-\Omega$        |  |

|                                  |                               | 3.6 kΩ ±1%                    | 2            | 1,80031 0 11                                    |  |

|                                  |                               | Do Not Install (DNI)          | 3            | 7                                               |  |

|                                  | R <sub>RXSEN1</sub>           | R <sub>RXSEN2</sub>           | RX_SEN Level | Medium RX                                       |  |

| RX Sensitivity                   | 22 kΩ – 40 kΩ (27 kΩ typical) | Do Not Install (DNI)          | Low          | Sensitivity Level:<br>R <sub>RXSEN1</sub> = DNI |  |

| TA Sensitivity                   | Do Not Install (DNI)          | Do Not Install (DNI)          | Medium       |                                                 |  |

|                                  | Do Not Install (DNI)          | 22 kΩ – 40 kΩ (27 kΩ typical) | High         | $R_{RXSEN2} = DNI$                              |  |

<sup>(1)</sup> These parameters are starting values for a low to medium loss system. Further tuning might be required based on specific host or device as well as cable length and loss profile. These settings are not specific to a 3.3 V supply system could be applicable to 5 V supply system as well.

<sup>(2)</sup> This resistor is needed for a 5 V supply to divide the voltage down so the RX SEN pin voltage does not exceed 5.0 V.

Table 8-3. Design Parameters for 2.3-V to 4.3-V VBAT Supply With Low to Medium Loss System

| PARAMETER                        |                                                      |                      |              |                                     |  |  |

|----------------------------------|------------------------------------------------------|----------------------|--------------|-------------------------------------|--|--|

| V <sub>CC</sub>                  | 2.3 V to 4.3V                                        |                      |              |                                     |  |  |

| I <sup>2</sup> C support require | I <sup>2</sup> C support required in system (Yes/No) |                      |              |                                     |  |  |

|                                  |                                                      | R <sub>BOOST</sub>   | BOOST Level  |                                     |  |  |

|                                  |                                                      | 0-Ω                  | 0            |                                     |  |  |

| Edge and DC Boo                  | ost                                                  | 1.8 kΩ ±1%           | 1            | Boost Level 0:<br>$R_{BOOST} = 0-Ω$ |  |  |

|                                  |                                                      | 3.6 kΩ ±1%           | 2            | 1,80031 0 12                        |  |  |

|                                  | Do Not Install (DNI)                                 |                      | 3            |                                     |  |  |

|                                  | R <sub>RXSEN1</sub>                                  | R <sub>RXSEN2</sub>  | RX_SEN Level | Medium RX                           |  |  |

| RX Sensitivity                   | 22 kΩ – 40 kΩ (27 kΩ typical)                        | Do Not Install (DNI) | Low          | Sensitivity Level:                  |  |  |

|                                  | Do Not Install (DNI)                                 | Do Not Install (DNI) | Medium       | R <sub>RXSEN1</sub> = DNI           |  |  |

|                                  | 37.5 kΩ <sup>(2)</sup>                               | 12.5 kΩ              | High         | R <sub>RXSEN2</sub> = DNI           |  |  |

<sup>(1)</sup> These parameters are starting values for a low to medium loss system. Further tuning might be required based on specific host or device as well as cable length and loss profile. These settings are not specific to a 2.3 V – 4.3 V supply system could be applicable to 5 V supply system as well.

### 8.2.2 Detailed Design Procedure

The ideal BOOST setting is dependent upon the signal chain loss characteristics of the target platform. The recommendation is to start with BOOST level 0, and then increment to BOOST level 1, and so on. Same applies to the RX sensitivity setting where it is recommended to plan for the required pads or connections to change boost settings, but to start with RX sensitivity level Low.

In order for the TUSB216I to recognize any change to the BOOST setting, the RSTN pin must be toggled. This is because the BOOST pin is latched on power up and the pin is ignored thereafter.

#### **Note**

The TUSB216I compensates for extra attenuation in the signal path according to the configuration of the RX\_SEN pin. This maximum recommended voltage for this pin is 5 V when selecting the highest RX sensitivity level.

Placement of the device is also dependent on the application goal. Table 8-4 summarizes our recommendations.

**Table 8-4. Platform Placement Guideline**

| PLATFORM GOAL                                            | SUGGESTED TUSB216I PLACEMENT           |

|----------------------------------------------------------|----------------------------------------|

| Pass USB Near End Mask at the receptacle                 | Close to measurement point (connector) |

| Pass USB Far End Eye Mask at the plug                    | Close to USB PHY                       |

| Cascade multiple TUSB216Is to improve device enumeration | Midway between each USB interconnect   |

<sup>(2)</sup> This resistor is needed for a VBAT supply (2.3 V – 4.3 V) to divide the voltage down so the RX\_SEN pin voltage does not exceed 5.0 V

Table 8-5. Table of Recommended Settings

| Tubic of the commended octaings                                |         |                |  |  |  |  |  |  |

|----------------------------------------------------------------|---------|----------------|--|--|--|--|--|--|

| BOOST and RX_SEN settings (1)for channel loss                  |         |                |  |  |  |  |  |  |

| Pre-channel cable length (Between USB PHY and TUSB216I)        | BOOST   | RX_SEN         |  |  |  |  |  |  |

| 0-3 meter                                                      | Level 0 | Medium or High |  |  |  |  |  |  |

| 2-5 meter                                                      | Level 1 | Medium or High |  |  |  |  |  |  |

| Post-channel cable length (Between TUSB216l and inter-connect) | BOOST   | RX_SEN         |  |  |  |  |  |  |

| 0-2 meter                                                      | Level 0 | Medium or High |  |  |  |  |  |  |

| 1-4 meter                                                      | Level 1 | Medium or High |  |  |  |  |  |  |

<sup>(1)</sup> These parameters are starting values for different cable lengths. Further tuning might be required based on specific host or device as well as cable length and loss profile.

### 8.2.2.1 Test Procedure to Construct USB High-speed Eye Diagram

#### Note

USB-IF certification tests for High-speed eye masks require the *mandated use* of the USB-IF developed test fixtures. These test fixtures do not require the use of oscilloscope probes. Instead they use SMA cables. More information can be found at the USB-IF Compliance Updates Page. It is located under the *Electrical Specifications* section, ID 86 dated March 2013.

The following procedure must be followed before using any oscilloscope compliance software to construct a USB High-speed Eye Mask:

### 8.2.2.1.1 For a Host Side Application

- 1. Configure the TUSB216I to the desired BOOST setting

- 2. Power on (or toggle the RSTN pin if already powered on) the TUSB216I

- 3. Using SMA cables, connect the oscilloscope and the USB-IF host-side test fixture to the TUSB216I

- 4. Enable the host to transmit USB TEST PACKET

- 5. Execute the oscilloscope USB compliance software.

- 6. Repeat the above steps in order to re-test TUSB216I with a different BOOST setting (must reset to change)

#### 8.2.2.1.2 For a Device Side Application

- 1. Configure the TUSB216I to the desired BOOST setting

- 2. Power on (or toggle the RSTN pin if already powered on) the TUSB216I

- 3. Connect a USB host, the USB-IF device-side test fixture, and USB device to the TUSB216I. Ensure that the USB-IF device test fixture is configured to the 'INIT' position

- 4. Allow the host to enumerate the device

- 5. Enable the device to transmit USB TEST PACKET

- 6. Using SMA cables, connect the oscilloscope to the USB-IF device-side test fixture and ensure that the device-side test fixture is configured to the 'TEST' position.

- 7. Execute the oscilloscope USB compliance software.

- 8. Repeat the above steps in order to re-test TUSB216I with a different BOOST setting (must reset to change)

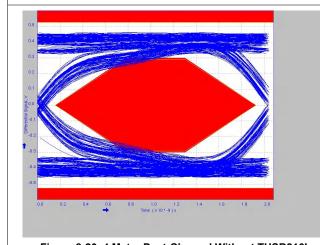

### 8.2.3 Application Curves

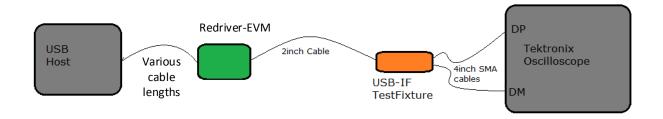

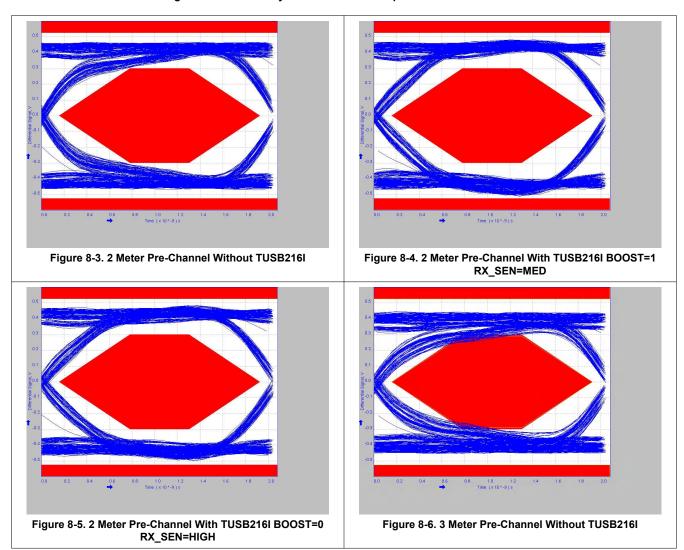

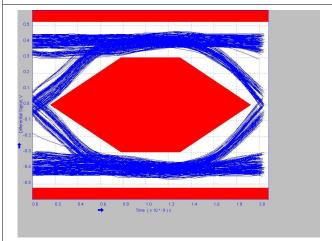

Figure 8-2. Near End Eye Measurement Set-Up With Pre-Channel Cable

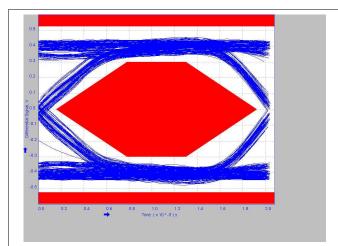

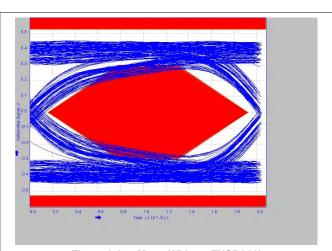

# 8.2.3 Application Curves (continued)

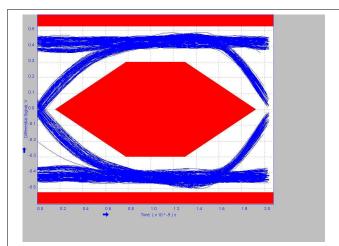

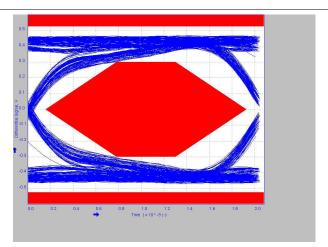

Figure 8-7. 3 Meter Pre-Channel With TUSB216I BOOST=0 RX\_SEN=HIGH

Figure 8-8. 5 Meter Without TUSB216I

Figure 8-9. 5 Meter Pre-Channel With TUSB216I BOOST=1 RX\_SEN=MED

Figure 8-10. 5 Meter Pre-Channel With TUSB216I BOOST=2 RX\_SEN=MED

### 8.2.3 Application Curves

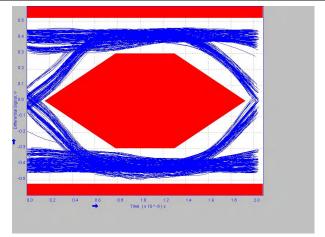

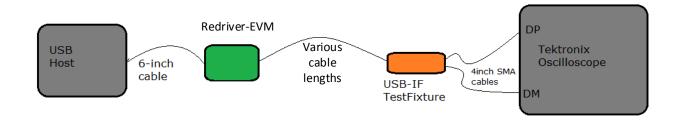

Figure 8-11. Near End Eye Measurement Set-Up With Post-Channel Cable

Product Folder Links: TUSB216I

Ibmit Document Feedback

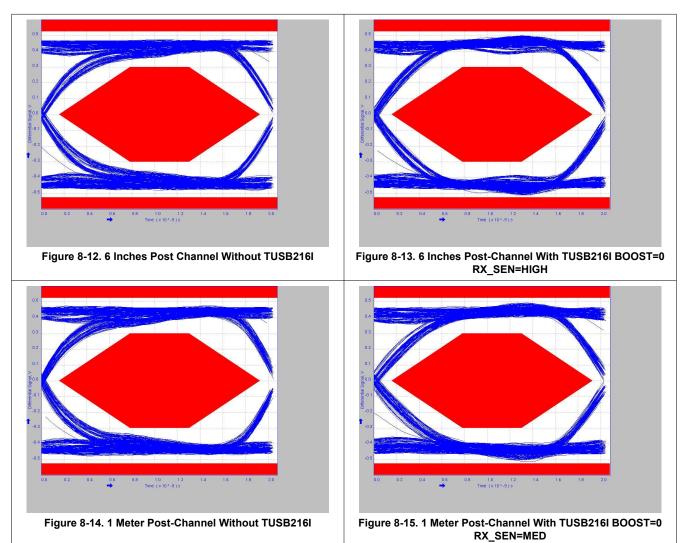

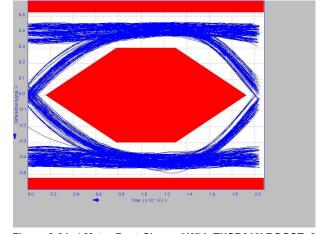

# 8.2.3 Application Curves (continued)

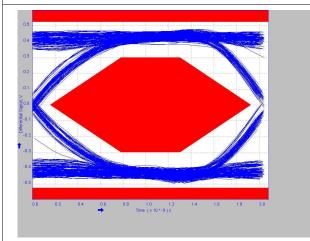

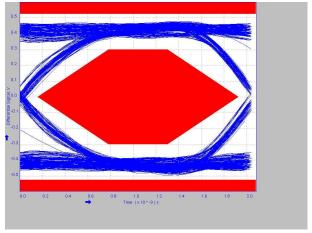

Figure 8-16. 1 Meter Post-Channel With TUSB216I BOOST=0 RX\_SEN=HIGH

Figure 8-17. 2 Meter Post-Channel Without TUSB216I

Figure 8-18. 2 Meter Post-Channel With TUSB216I BOOST=1 RX\_SEN=MED

Figure 8-19. 2 Meter Post-Channel With TUSB216I BOOST=1 RX\_SEN=HIGH

Figure 8-20. 4 Meter Post-Channel Without TUSB216I

Figure 8-21. 4 Meter Post-Channel With TUSB216I BOOST=2 RX\_SEN=MED

### 8.3 Power Supply Recommendations

On power up, the interaction of the RSTN pin and power on ramp could result in digital circuits not being set correctly. The device should not be enabled until the power on ramp has settled to minimum recommended supply voltage or higher to ensure a correct power on reset of the digital circuitry. If RSTN cannot be held low by microcontroller or other circuitry until the power on ramp has settled, then an external capacitor from the RSTN pin to GND is required to hold the device in the low power reset state.

The RC time constant should be larger than five times of the power on ramp time (0 to  $V_{CC}$ ). With a typical internal pullup resistance of 500 k $\Omega$ , the recommended minimum external capacitance is calculated as:

[Ramp Time x 5]

$$\div$$

[500 k $\Omega$ ] (1)

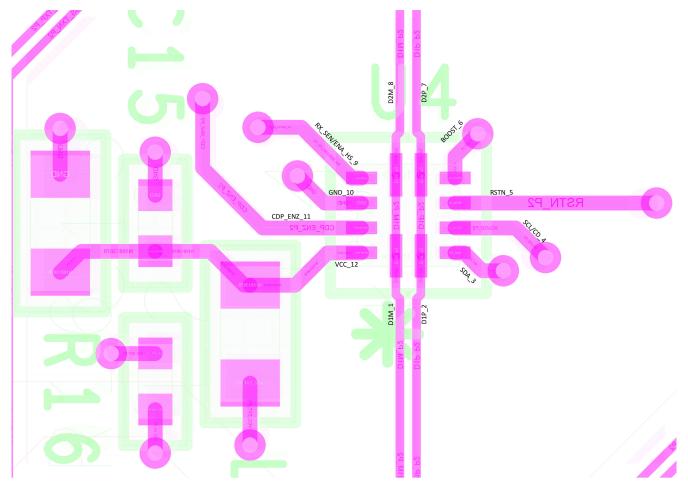

### 8.4 Layout

## 8.4.1 Layout Guidelines

Although the land pattern has matched trace width to pad width, optimal impedance control is based on the user's own PCB stack-up. The recommendation is to maintain  $90 \Omega$  differential routing underneath the device.

# 8.4.2 Layout Example

Figure 8-22. Layout Example

# 9 Device and Documentation Support

# 9.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Notifications* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 9.2 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 9.3 Trademarks

TI E2E™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

# 9.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# 9.5 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

# 10 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | Changes from Revision * (March 2021) to Revision A (December 2023) | Page |

|---|--------------------------------------------------------------------|------|

| • | Added Device Comparison section                                    | 2    |

|   | • Added 400 kHz I2C support                                        |      |

|   | Added timing table for 400 kHz I2C Fast Mode                       |      |

|   | Added I2C standard and fast mode support in Detailed Description   |      |

|   | 11                                                                 |      |

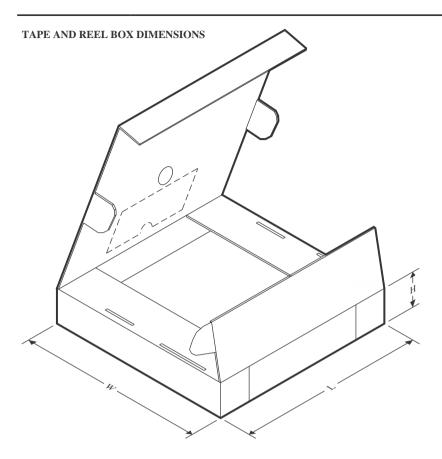

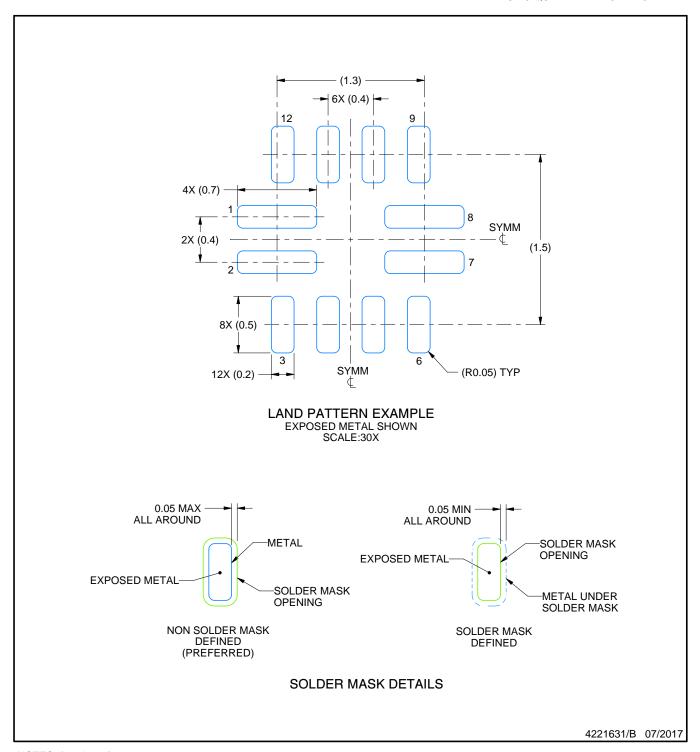

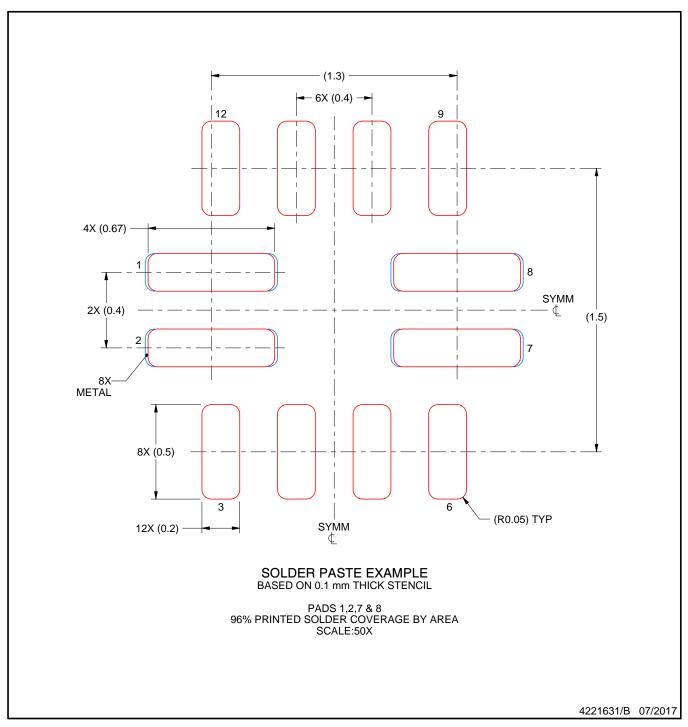

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/ Op temp (°C) Peak reflow |           | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|--------------------------------------|-----------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material |                                      |           | (6)          |