TPSF12C3 SNVSCB8A - MARCH 2023 - REVISED APRIL 2023

## TPSF12C3 Standalone, Active, EMI Filter for Common-mode Noise Mitigation in Three-Phase, AC, Power Systems

#### 1 Features

- **Functional Safety-Capable**

- Documentation available to aid functional safety system design

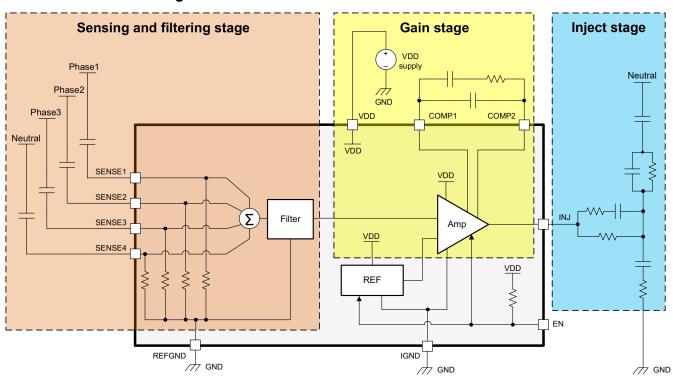

- Voltage-sense, current-inject active EMI filter

- Optimized for CISPR 11 and CISPR 32 Class B conducted EMI requirements

- Low impedance for common-mode emissions over the applicable EMI frequency range (150 kHz to 3 MHz)

- 50%+ reduction in choke size, weight and cost

- Peak inject current of ±80 mA (typical)

- Amplifier with unity gain bandwidth of 113 MHz

- Wide supply voltage range of 8 V to 16 V

- Junction temperature range of -40°C to 150°C

- Simple external configuration for three-phase AC power systems

- Integrated sensing filter and summing network

- Low leakage current at line frequency

- Simplified compensation network

- Inherent protection features for robust design

- Withstands surge of 6 kV (IEC 61000-4-5) with minimal external component count

- Enable pin for remote ON and OFF control

- VDD voltage UVLO protection with hysteresis

- Thermal shutdown protection with hysteresis

- 4.2-mm × 2-mm SOT-23 14-pin (DYY) package

## 2 Applications

- Grid infrastructure EV charging station

- HVAC motor control, aerospace and defense

- Welders, inverters and other industrial systems

- Telecom AC/DC rectifiers

# $\frac{1}{2}$ SENSE2 SENSE3 VDD SENSE4 TPSF12C3 **Simplified Schematic**

## 3 Description

The TPSF12C3 is an active filter IC designed to reduce common-mode (CM) electromagnetic interference (EMI) in three-phase AC power systems.

The active EMI filter (AEF) configured with voltage sense and current inject (VSCI) uses a capacitive multiplier circuit to emulate the Y-capacitors in a conventional passive filter design. The device senses the high-frequency noise on each power line using a set of sense capacitors and injects noise-canceling currents back into the power lines using an injection capacitor. The effective active capacitance is set by the circuit gain and the injection capacitance. The AEF sensing and injection impedances use relatively low capacitance values with small component footprints. The device includes integrated filtering, compensation and protection circuitry, and an enable

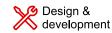

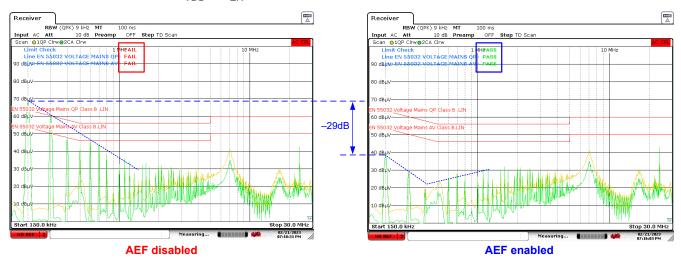

The TPSF12C3 provides a very low impedance path for CM noise in the frequency range of interest for EMI measurement. Enabling up to 30 dB of CM noise reduction at the lower end of specified frequency ranges (for example, 150 kHz to 3 MHz) significantly reduces the size, weight and cost of the CM filter implementation.

## **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| TPSF12C3    | DYY (SOT-23-THIN, 14)  | 4.20 mm × 2.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

**EMI Mitigation Result**

## **Table of Contents**

| 1 Features                           | 1 | 8.3 Feature Description                             | 9                   |

|--------------------------------------|---|-----------------------------------------------------|---------------------|

| 2 Applications                       |   | 8.4 Device Functional Modes                         |                     |

| 3 Description                        |   | 9 Applications and Implementation                   | 13                  |

| 4 Revision History                   | 2 | 9.1 Application Information                         |                     |

| 5 Device Comparison Table            |   | 9.2 Typical Applications                            |                     |

| 6 Pin Configuration and Functions    | 3 | 9.3 Power Supply Recommendations                    |                     |

| 7 Specifications                     | 4 | 9.4 Layout                                          | 20                  |

| 7.1 Absolute Maximum Ratings         |   | 10 Device and Documentation Support                 |                     |

| 7.2 ESD Ratings                      | 4 | 10.1 Device Support                                 | 23                  |

| 7.3 Recommended Operating Conditions | 4 | 10.2 Documentation Support                          |                     |

| 7.4 Thermal Information              | 5 | 10.3 Receiving Notification of Documentation Update | es <mark>2</mark> 4 |

| 7.5 Electrical Characteristics       | 5 | 10.4 Support Resources                              | 24                  |

| 7.6 System Characteristics           | 7 | 10.5 Trademarks                                     | 24                  |

| 7.7 Typical Characteristics          |   | 10.6 Electrostatic Discharge Caution                | 24                  |

| 8 Detailed Description               |   | 10.7 Glossary                                       |                     |

| 8.1 Overview                         |   | 11 Mechanical, Packaging, and Orderable             |                     |

| 8.2 Functional Block Diagram         | 9 | Information                                         | 24                  |

| _                                    |   |                                                     |                     |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision * (March 2023) to Revision A (April 2023) | Page |

|----|----------------------------------------------------------------|------|

| •  | Changed status from Advance Information to Production Data     | 1    |

## **5 Device Comparison Table**

| DEVICE      | ORDERABLE PART NUMBER | PHASES | GRADE      | JUNCTION TEMPERATURE RANGE |

|-------------|-----------------------|--------|------------|----------------------------|

| TPSF12C3    | TPSF12C3DYYR          | 3      | Commerical | –40°C to 150°C             |

| TPSF12C1    | TPSF12C1DYYR          | 1      | Commercial | –40°C to 150°C             |

| TPSF12C3-Q1 | TPSF12C3QDYYRQ1       | 3      | Automotive | -40°C to 150°C             |

| TPSF12C1-Q1 | TPSF12C1QDYYRQ1       | 1      | Automotive | -40°C to 150°C             |

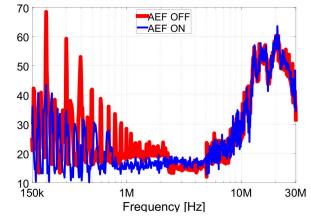

## **6 Pin Configuration and Functions**

Figure 6-1. 14-Pin SOT-23-THIN DYY Package (Top View)

**Table 6-1. Pin Functions**

|          | PIN    | TYPE(1) | DESCRIPTION                                                            |

|----------|--------|---------|------------------------------------------------------------------------|

| NO.      | NAME   | 1115    | DESCRIPTION                                                            |

| 1, 3, 12 | NC     | _       | No internal connection. Tie to the GND plane on the PCB.               |

| 2        | VDD    | Р       | Power supply for IC. Bypass to IGND with a 1-µF X7R ceramic capacitor. |

| 4        | SENSE1 | I       | Sense input (power line 1, 2, 3, or neutral)                           |

| 5        | SENSE2 | I       | Sense input (power line 1, 2, 3, or neutral)                           |

| 6        | SENSE3 | I       | Sense input (power line 1, 2, 3, or neutral)                           |

| 7        | SENSE4 | I       | Sense input (power line 1, 2, 3, or neutral)                           |

| 8        | EN     | I       | Enable signal to activate noise cancellation                           |

| 9        | REFGND | G       | Reference ground (Kelvin connected to IGND)                            |

| 10       | COMP1  | I       | Connection 1 for external compensation circuit                         |

| 11       | COMP2  | I       | Connection 2 for external compensation circuit                         |

| 13       | INJ    | 0       | Injection signal output                                                |

| 14       | IGND   | G       | Injection ground                                                       |

(1) P = Power, G = Ground, I = Input, O = Output

## 7 Specifications

## 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of –40°C to 150°C (unless otherwise noted)(1)

|                  |                                          | MIN         | MAX       | UNIT |

|------------------|------------------------------------------|-------------|-----------|------|

| Pin voltage      | VDD to IGND and REFGND                   | -0.3        | 18        | V    |

| Pin voltage      | SENSE1, SENSE2, SENSE3, SENSE4 to REFGND | -5.5        | 5.5       | V    |

| Pin voltage      | COMP1 to IGND and REFGND                 | -0.3        | 5.5       | V    |

| Pin voltage      | COMP2 to IGND and REFGND                 | -0.3        | 15        | V    |

| Pin voltage      | INJ to IGND                              | -0.3        | $V_{VDD}$ | V    |

| Pin voltage      | EN to IGND and REFGND                    | -0.3        | 18        | V    |

| Pin voltage      | IGND to REFGND                           | -0.3        | 0.3       | V    |

| Sink current     | INJ                                      |             | 150       | mA   |

| Source current   | INJ                                      |             | 150       | mA   |

| TJ               | Operating junction temperature           | -40         | 150       | °C   |

| T <sub>stg</sub> | Storage temperature                      | <b>–</b> 55 | 150       | °C   |

<sup>1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|         |                                            |                                                              | VALUE | UNIT |

|---------|--------------------------------------------|--------------------------------------------------------------|-------|------|

| V       | Electrostatic discharge                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)       | ±2000 | \/   |

| v (ESD) | V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 ((2)) | ±500  | v    |

- 1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)

|                    | , 3,                        | j 5                       | J , , , , , , , , , , , , , , , , , , , |     |                      |      |  |  |  |

|--------------------|-----------------------------|---------------------------|-----------------------------------------|-----|----------------------|------|--|--|--|

|                    |                             |                           | MIN                                     | NOM | MAX                  | UNIT |  |  |  |

| $V_{VDD}$          | VDD voltage range           |                           | 8                                       | 12  | 16                   | V    |  |  |  |

| V <sub>INJ</sub>   | Output voltage range        |                           | 2.5                                     |     | V <sub>VDD</sub> – 2 | V    |  |  |  |

| V <sub>SENSE</sub> | Sense voltage range         | Sense voltage range       |                                         |     | 5                    | V    |  |  |  |

| V <sub>EN</sub>    | Pin voltage                 | Pin voltage               |                                         |     | 16                   | V    |  |  |  |

| I <sub>INJ</sub>   | Output current range        | Source and sink magnitude |                                         |     | 80                   | mA   |  |  |  |

| T <sub>A</sub>     | Operating ambient temperatu | re                        | -40                                     |     | 105                  | °C   |  |  |  |

|                    |                             |                           |                                         |     |                      |      |  |  |  |

Submit Document Feedback

## 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | DYY (SOT-23-THIN) | LINUT |

|-----------------------|----------------------------------------------|-------------------|-------|

|                       | THERMAL METRIC                               | 14 PINS           | UNIT  |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 94                | °C/W  |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 43                | °C/W  |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 30                | °C/W  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1.3               | °C/W  |

| ΨЈВ                   | Junction-to-board characterization parameter | 28                | °C/W  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

Limits apply over the junction temperature ( $T_J$ ) range of  $-40^{\circ}$ C to 150°C, unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{VDD}$  = 12  $V^{(1)}$ .

|                         | PARAMETER                                                | TEST CONDITIONS                                                                                                          | MIN  | TYP  | MAX  | UNIT |

|-------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY                  |                                                          |                                                                                                                          |      |      | '    |      |

| I <sub>Q</sub>          | V65                                                      | SENSE1, SENSE2, SENSE3, and SENSE4 grounded, $V_{EN}$ = 5 V, 8 V $\leq$ $V_{VDD} \leq$ 16 V                              | 6.25 | 13.2 | 25.5 | mA   |

| IQ                      | VDD quiescent current                                    | SENSE1, SENSE2, SENSE3, and<br>SENSE4 grounded, V <sub>EN</sub> = 5 V, V <sub>VDD</sub> =<br>12 V, T <sub>J</sub> = 25°C | 11   | 13.2 | 15.5 | IIIA |

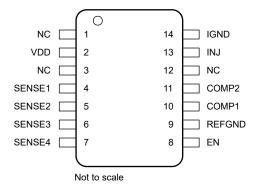

| I <sub>SD</sub>         | VDD shutdown supply current                              | V <sub>EN</sub> = 0 V                                                                                                    |      | 55   |      | μΑ   |

| SUPPLY VOLT             | AGE UVLO                                                 |                                                                                                                          |      |      | •    |      |

| V <sub>VDD-UV-R</sub>   | UVLO rising threshold                                    | V <sub>VDD</sub> rising                                                                                                  | 7.35 | 7.7  | 7.95 | V    |

| V <sub>VDD-UV-F</sub>   | UVLO falling threshold                                   | V <sub>VDD</sub> falling                                                                                                 | 6.4  | 6.7  | 7.0  | V    |

| V <sub>VDD-UV-HYS</sub> | UVLO hysteresis                                          |                                                                                                                          |      | 0.97 |      | V    |

| ENABLE                  |                                                          |                                                                                                                          |      |      |      |      |

| V <sub>EN-H</sub>       | EN voltage high                                          |                                                                                                                          | 2.2  |      |      | V    |

| V <sub>EN-L</sub>       | EN voltage low                                           |                                                                                                                          |      |      | 0.8  | V    |

| R <sub>EN</sub>         | EN pin pull-up resistance to VDD                         | V <sub>EN</sub> = 0 V                                                                                                    |      | 850  |      | kΩ   |

| I <sub>EN-LKG</sub>     | EN input leakage current                                 | V <sub>EN</sub> = 12 V                                                                                                   |      | 840  |      | nA   |

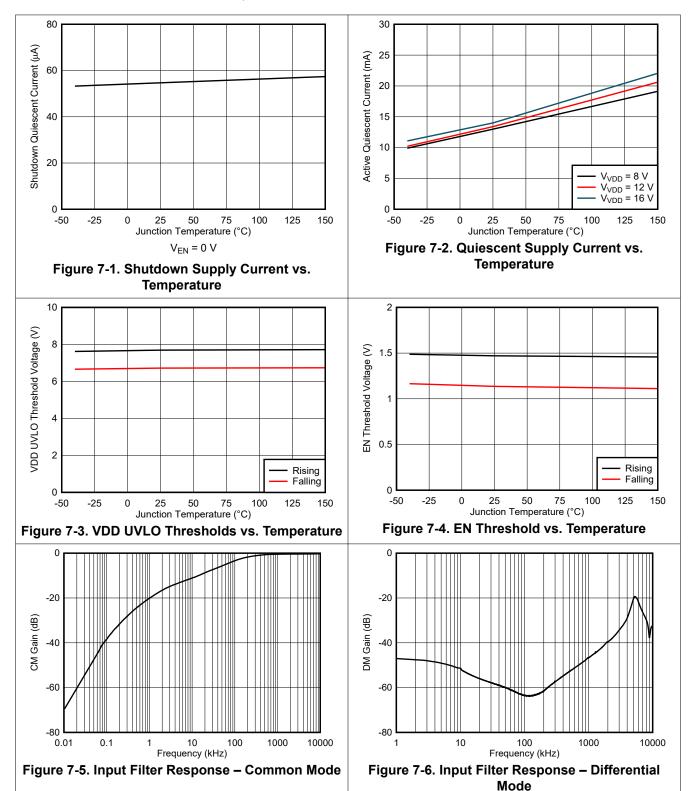

| INPUT FILTER            | NETWORK                                                  |                                                                                                                          |      |      | '    |      |

|                         |                                                          | $C_{SEN} = 2 \mu F^{(2)}, 60 \text{ Hz}$                                                                                 |      | -44  |      |      |

|                         | Gain from shorted power lines through                    | $C_{SEN} = 2 \mu F^{(2)}, 50 \text{ kHz}$                                                                                |      | -4   |      | ٦D   |

| A <sub>CM</sub>         | single sense cap, C <sub>SEN</sub> , to COMP1 vs. REFGND | $C_{SEN} = 2 \mu F^{(2)}, 500 \text{ kHz}^{(3)}$                                                                         |      | -2   |      | dB   |

|                         |                                                          | $C_{SEN} = 2 \mu F^{(2)}, 1 \text{ MHz}^{(3)}$                                                                           |      | -1   |      |      |

## 7.5 Electrical Characteristics (continued)

Limits apply over the junction temperature ( $T_J$ ) range of  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{VDD} = 12$   $V_{VDD}^{(1)}$ .

|                                                                                                                 | PARAMETER                                                                | TEST CONDITIONS                                                                                                                                | MIN                  | TYP  | MAX | UNIT |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----|------|

|                                                                                                                 |                                                                          | SENSE1 shorted to SENSE2,<br>SENSE3 shorted to SENSE4,<br>$C_{SEN1} = C_{SEN3} = 1 \mu F^{(2)}$ , 60 Hz                                        |                      | -71  |     |      |

| AMPLIFIER  ADC  fBW  fBW40  VOFST  VINJ-MAX  VINJ-MIN  INJ-MAX-OP  PSRR  PSRR <sub>10</sub> PSRR <sub>100</sub> |                                                                          | SENSE1 shorted to SENSE2,<br>SENSE3 shorted to SENSE4,<br>$C_{SEN1} = C_{SEN3} = 1 \mu F^{(2)}$ , 1 kHz                                        |                      | -59  |     |      |

| A <sub>DM</sub>                                                                                                 | Gain from differential signal applied to SENSE lines to COMP1 vs. REFGND | SENSE1 shorted to SENSE2,<br>SENSE3 shorted to SENSE4,<br>C <sub>SEN1</sub> = C <sub>SEN3</sub> = 1 µF <sup>(2)</sup> , 500 kHz <sup>(3)</sup> |                      | -42  |     | dB   |

| AMPLIFIED                                                                                                       |                                                                          | SENSE1 shorted to SENSE2, SENSE3 shorted to SENSE4, $C_{SEN1} = C_{SEN3} = 1 \ \mu F^{(2)}$ , 1 MHz <sup>(3)</sup>                             |                      | -43  |     |      |

|                                                                                                                 |                                                                          | SENSE1 shorted to SENSE2,<br>SENSE3 shorted to SENSE4,<br>$C_{SEN1} = C_{SEN3} = 1 \ \mu F^{(2)}$ , 10 MHz <sup>(3)</sup>                      |                      | -35  |     |      |

| AMPLIFIER                                                                                                       |                                                                          |                                                                                                                                                |                      |      |     |      |

| A <sub>DC</sub>                                                                                                 | DC gain                                                                  |                                                                                                                                                | 52                   | 58   | 69  | dB   |

| f <sub>BW</sub>                                                                                                 | Unity gain bandwidth <sup>(3)</sup>                                      |                                                                                                                                                |                      | 113  |     | MHz  |

| f <sub>BW40</sub>                                                                                               | 40 dB gain frequency                                                     |                                                                                                                                                |                      | 1    |     | MHz  |

| V <sub>OFST</sub>                                                                                               | COMP1 offset voltage                                                     |                                                                                                                                                |                      | 2    |     | V    |

| V <sub>INJ-MAX</sub>                                                                                            | Maximum output voltage for linear operation <sup>(3)</sup>               | COMP2 to INJ gain > 36 dB                                                                                                                      | V <sub>VDD</sub> – 2 |      |     | V    |

| V <sub>INJ-MIN</sub>                                                                                            | Minimum output voltage for linear operation <sup>(3)</sup>               | COMP2 to INJ gain > 36 dB                                                                                                                      |                      |      | 2.5 | V    |

| INLLMAY OR                                                                                                      | INJ current at linearity limits <sup>(3)</sup>                           | $V_{INJ} = V_{VDD} - 2 V$                                                                                                                      | 80                   |      |     | mA   |

| 'INJ-MAX-OP                                                                                                     | into ourient at infoarity infinoa                                        | $V_{INJ} = V_{IGND} + 2.5 V$                                                                                                                   |                      |      | -80 | mA   |

| PSRR                                                                                                            |                                                                          |                                                                                                                                                |                      |      |     |      |

| PSRR <sub>10</sub>                                                                                              |                                                                          | 10 pF in parallel with the series combination of 10 nF and 2 k $\Omega$ between COMP1 and COMP2, 10 kHz                                        |                      | 0    |     |      |

| PSRR <sub>100</sub>                                                                                             |                                                                          | 10 pF in parallel with the series combination of 10 nF and 2 k $\Omega$ between COMP1 and COMP2, 100 kHz                                       |                      | 6    |     | dB   |

| STARTUP                                                                                                         |                                                                          |                                                                                                                                                | 1                    |      |     |      |

| t <sub>W</sub>                                                                                                  | Startup delay <sup>(3)</sup>                                             | Time from VDD = EN applied until output valid                                                                                                  |                      | 43   |     | ms   |

| t <sub>SU</sub>                                                                                                 | EN high to valid output                                                  |                                                                                                                                                |                      | 42   |     | ms   |

| t <sub>SD</sub>                                                                                                 | EN low to stop output signal                                             |                                                                                                                                                |                      | 0.32 |     | μs   |

| THERMAL SHU                                                                                                     | JTDOWN                                                                   |                                                                                                                                                | •                    |      | 1   |      |

| T <sub>J-SHD</sub>                                                                                              | Thermal shutdown threshold <sup>(3)</sup>                                | Temperature rising                                                                                                                             |                      | 175  |     | °C   |

| J-SHD                                                                                                           |                                                                          | , ,                                                                                                                                            |                      |      |     |      |

<sup>(1)</sup> MIN and MAX limits are 100% production tested at 25°C unless otherwise specified. Limits over the operating temperature range verified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

Submit Document Feedback

<sup>(2)</sup> Capacitance chosen for effective test only. Do not use this capacitance in applications.

<sup>(3)</sup> Parameter specified by design, statistical analysis and production testing of correlated parameters.

## 7.6 System Characteristics

The following specifications apply only to the typical applications circuit, with nominal component values. Specifications in the typical (TYP) column apply to  $T_J$  = 25°C and  $V_{VDD}$  = 12 V only. Specifications in the minimum (MIN) and maximum (MAX) columns apply to the case of typical components over the temperature range of  $T_J$  = -40°C to 150°C. These specifications are not ensured by production testing.

|                     | PARAMETER                            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------------------|-----------------|-----|-----|-----|------|

| SUPPLY              |                                      |                 |     |     |     |      |

| I <sub>SUPPLY</sub> | Input supply current with INJ loaded |                 |     | 15  |     | mA   |

## 7.7 Typical Characteristics

$V_{VDD} = V_{EN} = 12 \text{ V}$ , unless otherwise specified.

## 8 Detailed Description

## 8.1 Overview

The TPSF12C3 is an active electromagnetic interference (EMI) filter that is designed to reduce common-mode (CM) conducted emissions in off-line power converter systems. Using a VSCI architecture, the device senses the high-frequency noise on each power line using a set of Y-rated capacitors,  $C_{SEN1-4}$ , then injects noise-canceling currents back into the power lines using a Y-rated capacitor,  $C_{INJ}$ , along with a damping circuit that ensures stability. The device includes integrated filtering, compensation and protection circuitry.

The TPSF12C3 provides a low-impedance shunt path for CM noise in the frequency range of interest for EMI measurement. This feature can achieve approximately 15 to 30 dB of CM attenuation over the applicable frequency range (for example, 100 kHz to 3 MHz) helping to reduce the size of CM chokes, typically the largest components in the filter.

The TPSF12C3 operates over a supply voltage range of 8 V to 16 V and can withstand 18 V. The device features include:

- Internal circuitry that simplifies compensation and design

- Built-in supply voltage UVLO to ensure proper operation

- Built-in thermal shutdown protection

- An EN input that allows power saving when the system is idling

The active EMI filter circuit significantly reduces EMI filter cost, size, and weight, while helping to meet CISPR 11 and CISPR 32 Class B limits for conducted emissions. Leveraging a pin arrangement designed for simple layout that requires relatively few external components, the TPSF12C3 is specified for maximum ambient and junction temperatures of 105°C and 150°C, respectively.

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Active EMI Filtering

A compact and efficient design of the input EMI filter is one of the main challenges in high-density switching regulator design and is critical to achieving the full benefits of electrification in industrial, enterprise, aerospace

and other highly constrained system environments. For AC-input applications in general, CM chokes and Y-capacitors provide CM filtering, whereas the leakage inductance of the CM chokes and the X-capacitors provide DM filtering. However, CM filters for such applications may have limited Y-capacitance due to touch-current safety requirements and thus require large-sized CM chokes to achieve the requisite attenuation – ultimately resulting in filter designs with bulky, heavy and expensive passive components. Fortunately, the deployment of active filter circuits enable more compact filter solutions for next-generation power conversion systems.

#### 8.3.1.1 Schematics

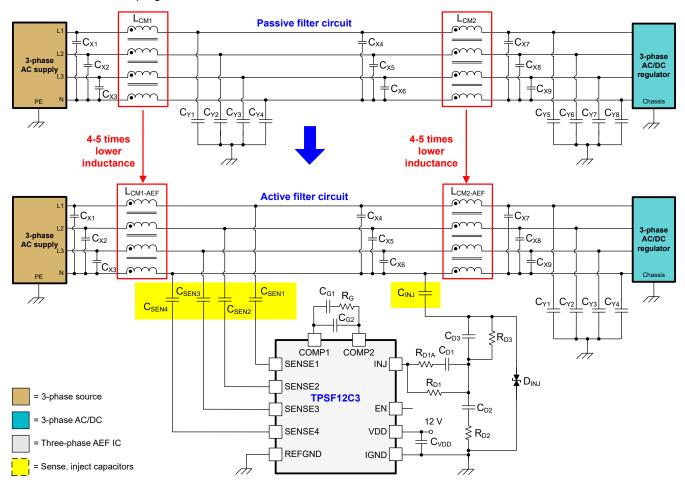

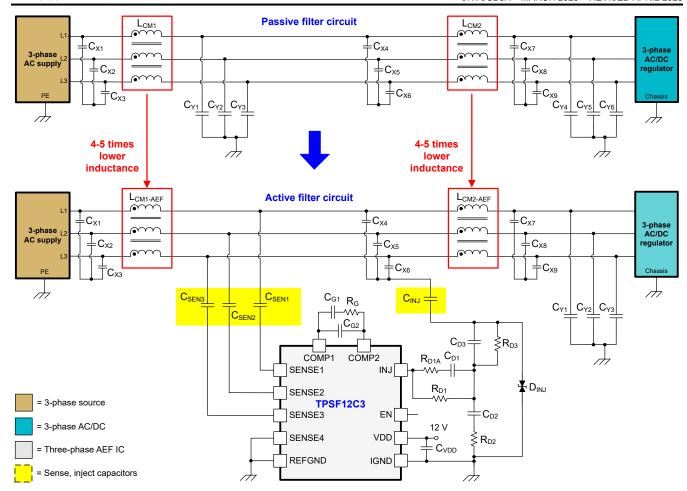

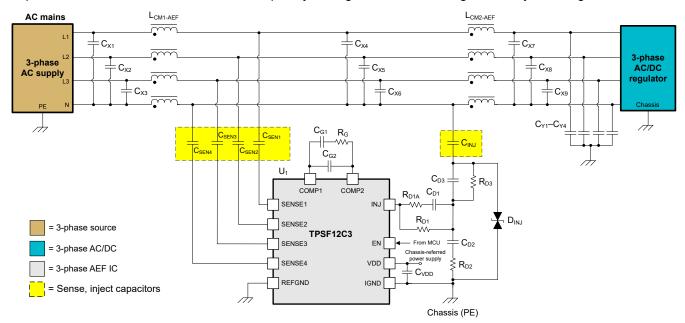

Figure 8-1 and Figure 8-2 show schematics for conventional two-stage passive EMI filters with and without neutral, respectively, in kilowatt-scale, grid-connected applications. L, N and PE refer to the respective live, neutral and protective earth connections. Multistage filters as shown provide high roll-off and are widely used in high-power AC line applications where CM noise is often more challenging to mitigate than DM noise. The low-order switching harmonics usually dictate the size of the reactive filter components based on the required corner frequency (or multiple corner frequencies in multistage designs).

Also included in Figure 8-1 and Figure 8-2 are the corresponding active filter designs. The active circuit replaces the bank of Y-capacitors positioned between the CM chokes with a three-phase AEF circuit using the TPSF12C3 to provide a lower impedance shunt path for CM currents. The sense pins of the TPSF12C3 interface with the power lines using a set of Y-rated sense capacitors, typically 680 pF, and feed into an internal high-pass filter and signal combiner. The IC rejects both line-frequency (50-Hz or 60-Hz) AC voltage as well as DM disturbances, while amplifying high-frequency CM disturbances and maintaining closed-loop stability using an external tunable damping circuit.

Figure 8-1. Circuit Schematic of a Three-Phase, Four-Wire Passive Filter and Corresponding Active Filter Solution for CM Attenuation

Figure 8-2. Circuit Schematic of a Three-Phase, Three-Wire Passive Filter and Corresponding Active Filter Solution for CM Attenuation

The X-capacitors placed between the two CM chokes effectively provide a low-impedance path between the power lines from a CM standpoint, typically up to low-MHz frequencies. This allows current injection onto one power line, typically neutral, using only one inject capacitor. If the three-phase filter is a three-wire system without neutral as shown in Figure 8-2, the SENSE4 pin of the TPSF12C3 ties to ground and the inject capacitor couples through a star-point connection of the X-capacitors.

## 8.3.2 Capacitive Amplification

An AEF circuit for CM noise mitigation fundamentally either amplifies the apparent inductance of a CM choke or the apparent capacitance of a Y-capacitor over the frequency range of interest. A VSCI AEF circuit configured for CM attenuation uses an amplifier stage as a capacitive multiplier of the inject capacitor,  $C_{\text{INJ}}$ . This higher value of the active capacitance supports lower values for the CM chokes to achieve a target attenuation. More specifically, the amplified Y-capacitance enables a reduction of each CM choke inductance by up to 80% (while keeping the filter corner frequencies effectively unchanged), resulting in lower size, weight, and cost of the CM chokes.

Capacitive multiplication of the inject capacitance occurs over a relevant frequency range for low- and midfrequency emissions, while not impacting the value at low frequency applicable for touch current measurement. The total capacitance of the sense and inject capacitors (highlighted in yellow in Figure 8-1 and Figure 8-2) is kept less than or equal to that of the replaced Y-capacitors in the equivalent passive filter, which results in the total line-frequency leakage current remaining effectively unchanged or reduced.

## 8.3.3 Integrated Line Rejection Filter

The TPSF12C3 has a built-in input line filter. The high-pass filter stage attenuates the large line-frequency (50 Hz or 60 Hz) components of the power-line voltages, both line-to-line and line-to-earth, thus maximizing the useful voltage range of the low-voltage output at INJ.

The circuit also sums the signals in a CM combiner, rejecting the DM components of the voltages and extracting a signal that represents the CM noise signature without line-frequency components. Combined with the action of the high-pass filter, the net result is that the COMP1 pin voltage represents the sensed high-frequency CM noise that the device attempts to cancel. Because the entire filter is integrated in the device, matching is better than what can be achieved using discrete components.

#### 8.3.4 Compensation

The TPSF12C3 contains partial internal compensation that, when combined with two capacitors and a resistor between COMP1 and COMP2, forms a lead-lag network. This internal network allows fewer external components to be used.

#### 8.3.5 Remote Enable

The TPSF12C3 has an enable input, EN, that allows the device to be shut down, drastically reducing power consumption during intervals when EMI mitigation is not required. The typical quiescent current consumption is 13.2 mA and 55  $\mu$ A when the device is enabled and disabled, respectively. Because many designs may not use this feature, a 850-k $\Omega$  pullup resistor connects internally between VDD and EN, allowing the EN pin to be left open.

In addition, INJ is pulled low when the device is disabled to reduce the effective resistance in series with C<sub>INJ</sub>.

#### 8.3.6 Supply Voltage UVLO Protection

To ensure that the TPSF12C3 operates safely while VDD is powered on and off as well as during brownout conditions, this device has a built-in UVLO protection to provide predictable behavior while VDD is below its operating voltage. UVLO releases when the VDD voltage exceeds 7.7 V (typical), allowing normal operation. UVLO engages if the VDD voltage falls below approximately 6.7 V (typical). There is approximately 1 V of UVLO hysteresis.

#### 8.3.7 Thermal Shutdown Protection

The TPSF12C3 provides built-in overtemperature protection that shuts down the device if the junction temperature exceeds approximately 175°C. After the junction temperature decreases by approximately 20°C, the device restarts. This process is repeated until the ambient temperature or power dissipation is reduced. The device has a relatively low thermal time constant and can cycle into and out of thermal shutdown at a high rate during a sustained overtemperature condition.

#### 8.4 Device Functional Modes

#### 8.4.1 Shutdown Mode

The EN pin provides ON and OFF control for the TPSF12C3. When the EN voltage is below approximately 0.8 V, the device is in shutdown mode. Most internal circuitry is shutdown. The quiescent current in shutdown mode drops to  $55~\mu$ A (typical). The TPSF12C3 also employs VDD internal undervoltage protection. If the VDD voltage is below its UVLO threshold, the device remains off. The INJ output pulls to ground while in shutdown mode.

#### 8.4.2 Active Mode

The TPSF12C3 is in active mode when  $V_{VDD}$  is above its UVLO threshold, EN is high, and there is no overtemperature fault. The simplest way to enable operation is to connect EN to VDD, which allows startup when the applied supply voltage exceeds the UVLO threshold voltage. In this mode, the device amplifies signals on COMP2 and outputs the amplified signal on the INJ pin.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 9 Applications and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 9.1 Application Information

The TPSF12C3 common-mode AEF IC helps to improve the CM EMI signature of three-phase AC power systems. The device provides a very low impedance path for CM noise in the frequency range of interest for EMI measurement and helps to meet prescribed limits for EMI standards, such as:

- CISPR 11, EN 55011 Industrial, Scientific and Medical (ISM) applications

- CISPR 25, EN 55025 Automotive applications

- CISPR 32, EN 55032 Multimedia applications

To expedite and streamline the process of designing of a TPSF12C3-based solution, a comprehensive TPSF12C3 quickstart calculator is available by download to assist the system designer with component selection for a given application.

## 9.2 Typical Applications

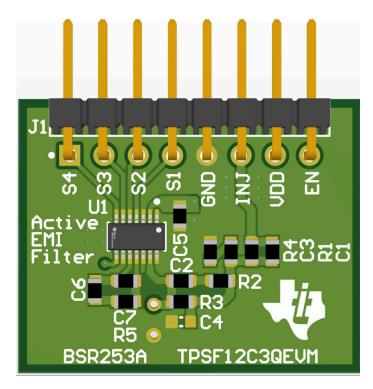

For the circuit schematic, bill of materials, PCB layout files, and test results of a TPSF12C3-powered implementation, see the TPSF12C3 EVM.

#### 9.2.1 Design 1 - AEF Circuit for Grid Infrastructure Applications

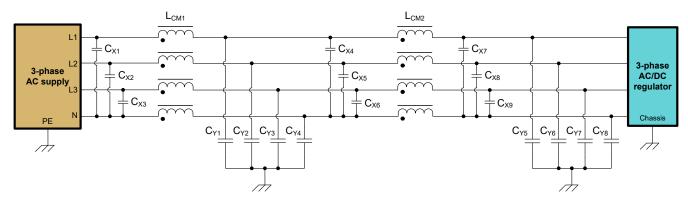

Figure 9-1 shows a schematic diagram of a 10-kW high-density AC/DC regulator with conventional two-stage passive EMI filter. The CM chokes and Y-capacitors provide CM filtering, whereas the leakage inductance of the CM chokes and the X-capacitors provide DM filtering. Similar to TI reference designs TIDA-01606, the circuit uses a three-phase power-factor correction (PFC) stage with SiC power MOSFETs.

The PFC stage runs at a fixed switching frequency of 100 kHz. Even though the use of GaN or SiC power switches enables a high power density, the conventional passive EMI filter typically occupies over 20% of the total solution size.

Figure 9-1. Circuit Schematic of a Three-phase AC/DC Regulator With a Conventional Two-Stage Passive EMI Filter

The AC/DC stage increases the CM EMI signature based on the high dv/dt of the SiC power switches as well as the various switch-node parasitic capacitances to chassis ground.

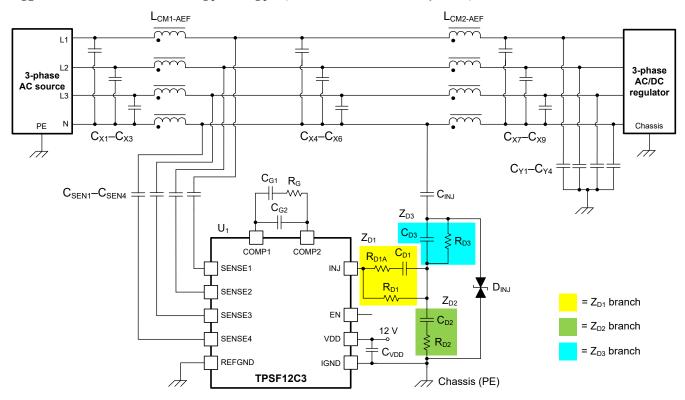

This application example replaces the four Y-capacitors, designated as  $C_{Y1}$ ,  $C_{Y2}$ ,  $C_{Y3}$  and  $C_{Y4}$  in Figure 9-1, with a three-phase AEF circuit using the TPSF12C3. See Figure 9-2. The AEF circuit provides effective capacitive multiplication of the inject capacitor, which reduces the inductance values to maintain the target LC corner

frequencies and thus the size, weight, and cost of the CM chokes, now designated as  $L_{CM1-AEF}$  and  $L_{CM2-AEF}$ . The total capacitance of the sense and inject capacitors is kept less than or equal to that of the replaced Y-capacitors, which results in the total line-frequency leakage current remaining effectively unchanged or reduced.

Figure 9-2. Circuit Schematic of a Three-phase Regulator With AEF Circuit Connected

## 9.2.1.1 Design Requirements

Table 9-1 shows the intended operating parameters for this application example. Also included is the total Y-rated filter capacitance that is allowed in order to meet the applicable touch current fault specification.

| VALUE                        |

|------------------------------|

|                              |

| 230 V L-N or 400 V L-L (RMS) |

| 47 Hz to 63 Hz               |

| 600 V to 1 kV                |

| 18 A                         |

| 10 kW                        |

| 100 kHz                      |

| 10 nF                        |

| _                            |

Table 9-1. Design Parameters

## 9.2.1.2 Detailed Design Procedure

Table 9-2 gives the selected component values, which are the same as those used in the TPSF12C3 EVM. This design uses a TVS diode placed at the low-voltage side of the inject capacitor for clamping during input surge conditions.

Table 9-2. AEF Circuit Components for Application Circuit 1

| REFERENCE<br>DESIGNATOR                                                              | QTY                           | SPECIFICATION                                                | MANUFACTURER <sup>(1)</sup> | PART NUMBER        |

|--------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------|-----------------------------|--------------------|

| C <sub>SEN1</sub> , C <sub>SEN2</sub> ,<br>C <sub>SEN3</sub> , C <sub>SEN4</sub> (2) | 4                             | Capacitor, ceramic, 680 pF, 300 VAC, Y2                      | MuRata                      | DE2B3SA681KN3AX02F |

| C <sub>INJ</sub> (2)                                                                 | 1                             | Capacitor, ceramic, 4.7 nF, 300 VAC, Y2                      | MuRata                      | DE2E3SA472MA3BX02F |

| C <sub>D1</sub> (2)                                                                  | 1                             | Capacitor, ceramic, 4.7 nF, 50 V, 0603                       | Various                     | _                  |

| C <sub>D2</sub> (2)                                                                  | 1                             | Capacitor, ceramic, 22 nF, 50 V, 0603                        | Various                     | _                  |

| C <sub>D3</sub>                                                                      | 1                             | Capacitor, ceramic, 4.7 nF, 50 V, 0603                       | Various                     | _                  |

| C <sub>G1</sub>                                                                      | 1                             | Capacitor, ceramic, 10 nF, 50 V, 0603                        | Various                     | _                  |

| C <sub>VDD</sub> 1 Cap                                                               |                               | Capacitor, ceramic, 10 pF, 50 V, 0603                        | Various                     | _                  |

|                                                                                      |                               | Capacitor, ceramic, 1 µF, 25 V, X7R, 0603                    | Various                     | _                  |

|                                                                                      |                               | TVS diode, bidirectional, 24 V, SOD-323                      | Eaton                       | STS321240B301      |

| R <sub>D1</sub>                                                                      | 1                             | Resistor, 1 kΩ, 0.1 W, 0603                                  | Various                     | _                  |

| R <sub>D1A</sub>                                                                     | 1 Resistor, 50 Ω, 0.1 W, 0603 |                                                              | Various                     | _                  |

| R <sub>D2</sub>                                                                      | 1                             | Resistor, 200 Ω, 0.1 W, 0603                                 | Various                     | _                  |

| R <sub>D3</sub>                                                                      | 1                             | Resistor, 698 Ω, 0.1 W, 0603                                 | Various                     | _                  |

| R <sub>G</sub>                                                                       | 1                             | Resistor, 1.5 kΩ, 0.1 W, 0603                                | Various                     | _                  |

| U <sub>1</sub>   1                                                                   |                               | TPSF12C3 common-mode AEF IC for three-phase AC power systems | Texas Instruments           | TPSF12C3DYYR       |

<sup>(1)</sup> See the *Third-Party Products Disclaimer*.

More generally, the TPSF12C3 AEF IC is designed to operate with a wide range of passive filter components and system parameters.

#### 9.2.1.2.1 Sense Capacitors

The sense pins of the TPSF12C3 feed into a high-pass filter and signal combiner within the IC, which rejects the line-frequency and DM components of the power line voltages, extracting the high-frequency CM component.

The sense pins externally interface to the power lines using Y-rated capacitors, designated as  $C_{SEN1}$ ,  $C_{SEN2}$ ,  $C_{SEN3}$  and  $C_{SEN4}$  in Figure 9-2. Choose Y2-rated sense capacitors of 680 pF, 300 VAC in this application to establish voltages at the SENSE pins of less than 1-V peak-to-peak when operating at maximum line voltage.

#### 9.2.1.2.2 Inject Capacitor

The INJ node interfaces to a power line using a Y-rated capacitor, designated as  $C_{\text{INJ}}$  in Figure 9-2. Choose a Y2-rated inject capacitor of 4.7 nF, 300 VAC in this design to accommodate an AC voltage swing at INJ with at least a 2.5-V margin of headroom from the positive and negative supply rails. The INJ pin biases at half the VDD supply voltage. Assuming a 12-V supply rail and allowing 2.5 V of upper and lower headroom, this implies that a swing of  $\pm 3.5$  V is available around the DC operating midpoint.

#### Note

Many commercially available Y-rated capacitors yield an effective capacitance that derates significantly with operating temperature. The effective capacitance value can be much lower than the nameplate capacitance, particularly when operating near the boundaries of the rated operating temperature range. Select the dielectric of the sense and inject capacitors to meet the required temperature range. Depending on the implementation, lower than expected sense and inject capacitances can affect the stability performance.

<sup>(2)</sup> Check the effective capacitance value based on the applied voltage and operating temperature.

#### 9.2.1.2.3 Compensation Network

The CM noise signal derived from the internal sensing filter and summation network of the TPSF12C3 is internally inverted and amplified by a gain stage. The components between the COMP1 and COMP2 pins of the IC, designated as as  $R_G$ ,  $C_{G1}$  and  $C_{G2}$  in Figure 9-2, set the gain characteristic.

More specifically, resistor  $R_G$  establishes a high midband AEF gain at frequencies where EMI filtering is required. Capacitor  $C_{G1}$  increases the impedance of that branch at low frequencies, which sets a lower AEF amplifer gain to further reject line-frequency components appearing at the INJ output. Capacitor  $C_{G2}$  preserves gain at high frequencies, which extends the AEF bandwidth.

Choose a value for  $R_G$  between 1 k $\Omega$  and 2 k $\Omega$ . A resistance of 1.5 k $\Omega$  is a common choice and selected in this example to set a midband gain of 50 dB. Choose capacitances for  $C_{G1}$  and  $C_{G2}$  of 10 nF and 10 pF, respectively, which establishes a gain rolloff below approximately 10 kHz for line- and low-frequency attenuation.

#### 9.2.1.2.4 Injection Network

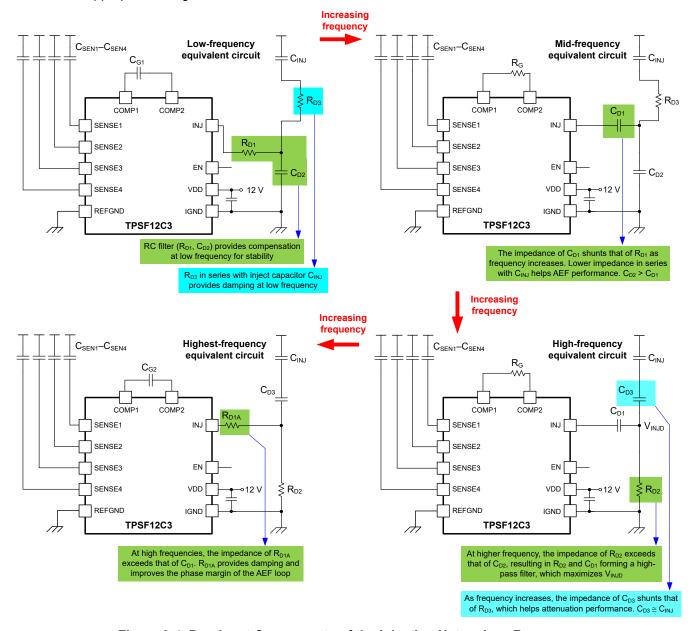

The components connected between the INJ pin and inject capacitor establish a damped injection network. Damping is specifically required to manage resonance between the CM choke inductance and inject capacitance, which manifests in the AEF loop gain as a pair of complex zeros.

Figure 9-3 highlights three specific RC branches:  $R_{D1}$ ,  $R_{D1A}$  and  $C_{D1}$  form one branch from the INJ pin;  $R_{D2}$  and  $C_{D2}$  in series connect to GND;  $R_{D3}$  and  $C_{D3}$  in parallel connect to the inject capacitor.

Figure 9-3. Injection Network

Based on the injection mechanism, the AEF circuit presents a low shunt impedance to CM noise. Given the three damping impedance branches highlighted in Figure 9-3, Equation 1 approximates the AEF impedance as:

$$Z_{AEF}(s) \approx \frac{Z_{INJ}(s) + Z_{D3}(s) + \left(Z_{D1}(s) \| Z_{D2}(s)\right)}{1 - G_{AEF}(s) \cdot \frac{Z_{D2}(s)}{Z_{D1}(s) + Z_{D2}(s)}}$$

(1)

Submit Document Feedback

where the term  $G_{AEF}$  is the gain from the power lines to the INJ node (see the TPSF12C3 quickstart calculator for related detail).

Equation 1 shows that the impedance  $Z_{INJ}$  appears in series with  $Z_{D3}$  and a parallel combination of  $Z_{D1}$  and  $Z_{D2}$ . Furthermore, the gain  $G_{AEF}$  is reduced by the voltage divider ratio between  $Z_{D2}$  and  $Z_{D1}$ . These effects combine to increase the effective impedance of the AEF and hence reduce its attenuation performance, thus illustrating a trade-off between performance and stability.

So while an injection network is needed for stability, it also adds impedance in series with the inject capacitor, thus compromising EMI mitigation. As shown below, the user can minimize the impact on performance with careful and appropriate design.

Figure 9-4. Dominant Components of the Injection Network vs Frequency

Illustrated in Figure 9-4, at low frequencies in the range of 5 kHz to 50 kHz, components  $R_{D1}$  and  $C_{D2}$  provide compensation and  $R_{D3}$  damps the effects of LC resonance. At higher frequencies (above 10 kHz), the dominant component impedance of each branch transitions to enable better attenuation performance:

R<sub>D1</sub> transitions to C<sub>D1</sub>

- C<sub>D2</sub> transitions to R<sub>D2</sub>

- R<sub>D3</sub> transitions to C<sub>D3</sub>

Finally, C<sub>D1</sub> transitions to R<sub>D1A</sub> if needed for phase margin of the AEF loop at high frequencies, typically above 100 kHz. When viewed in a clockwise direction, Figure 9-4 shows these transitions in sequence as frequency increases.

Below are basic guidelines to select the component values for the injection network:

- 1. The undamped loop gain characteristic is likely to be unstable within the range of 5 kHz to 50 kHz, which, as mentioned previously, relates to an LC resonance between CM choke inductance and inject capacitance. Observe from circuit simulation or by using the TPSF12C3 quickstart calculator the frequency, f<sub>LFstability</sub>, at which the phase crosses –180° with positive gain, indicating negative gain margin.

- 2. Choose a corner frequency with R<sub>D1</sub> and C<sub>D2</sub> equal to one fifth of the instability frequency:

$$\frac{1}{2\pi \cdot R_{D1} \cdot C_{D2}} = \frac{f_{LFstability}}{5} \tag{2}$$

Assigning  $R_{D1}$  = 1 k $\Omega$  and assuming instablity at 35 kHz, use Equation 3 to find a value for the capacitance of  $C_{D2}$ :

$$C_{D2}[nF] = \frac{5000}{2\pi \cdot R_{D1}[k\Omega] \cdot f_{LFstability}[kHz]} = \frac{5000}{2\pi \cdot 1 \cdot 35} = 22nF$$

(3)

- 3. Select  $C_{D1} < C_{D2}$ , where a typical choice is  $C_{D1} = C_{D2}/5 = 4.7$  nF.

- 4. Choose the resistance of R<sub>D2</sub> such that the R<sub>D2</sub>, C<sub>D2</sub> corner frequency is equal to that of R<sub>D1</sub>, C<sub>D1</sub>:

$$R_{D2} \left[ \Omega \right] = \frac{R_{D1} \left[ \Omega \right] \cdot C_{D1} \left[ nF \right]}{C_{D2} \left[ nF \right]} = \frac{R_{D1} \left[ \Omega \right]}{5} = \frac{1000}{5} = 200 \Omega$$

$$\tag{4}$$

- Select the resistance of R<sub>D3</sub> to damp the resonance around the instability frequency, f<sub>LFstability</sub>.

- A typical choice for  $R_{D3}$  is 500  $\Omega$  to 1 k $\Omega$ .

- Assign C<sub>D3</sub> equal to C<sub>INJ</sub> or a suitable value such that the R<sub>D3</sub>, C<sub>D3</sub> corner frequency is less than switching frequency.

- A lower resistance for R<sub>D3</sub> results in more damping but at the penalty of reduced high-frequency attenuation (or forces a higher value for C<sub>D3</sub> to maintain the applicable corner frequency below the switching frequency).

- 6. Select a resistance for  $R_{D1A}$  of 50  $\Omega$  to improve the phase margin of the AEF loop (if needed).

## 9.2.1.2.5 Surge Protection

EMI filter designs, both passive and active, typically use MOVs connected from the power lines to chassis ground to clamp surge voltage transients. While the sense pins of the TPSF12C3 have internal clamp protection, the higher value of inject capacitance produces larger currents during surge events and thus requires external protection. Place a bidirectional TVS diode on the low-voltage side of the inject capacitor with standoff voltage of 24 V. Using the SOD-323 packaged device given in Table 9-2, clamping occurs at 40 V and 50 V with surge currents of 1 A and 8 A, respectively.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 9.2.1.3 Application Curves

Unless otherwise indicated,  $V_{VDD} = V_{EN} = 12 \text{ V}$ .

#### Note

A high DM noise signature may mask improvement in CM noise performance related to AEF. A reduction of CM choke inductance may also reduce leakage inductance, which could impact DM noise attenuation. Install higher X-capacitance or a discrete DM filter inductor to manage DM attenuation as needed. Also, use a DM-CM noise splitter to isolate the CM component of the measured total noise.

Figure 9-5. CISPR 32 Class B EMI Mitigation Result with AEF On and Off (EN Tied High and Low)

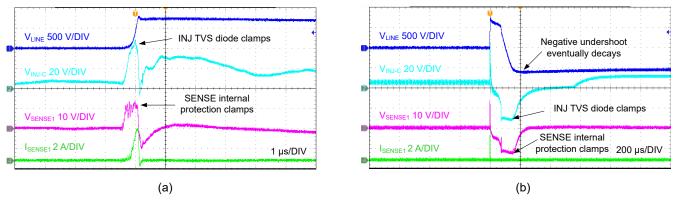

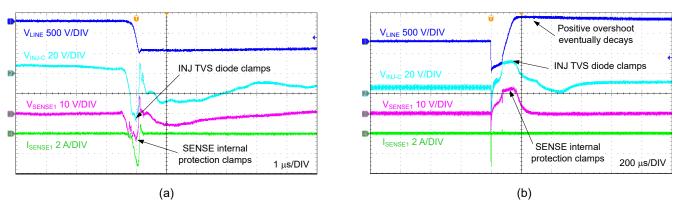

Figure 9-6. IEC 61000-4-5 Positive Surge, 5-kV Single Strike – 1 µs/div (a), 200 µs/div (b)

Figure 9-7. IEC 61000-4-5 Negative Surge, 5-kV Single Strike – 1 µs/div (a), 200 µs/div (b)

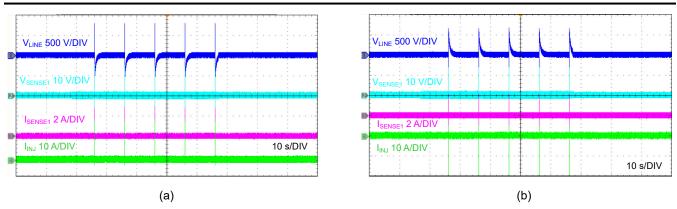

Figure 9-8. IEC 61000-4-5 Surge, 5-kV Repetitive Strike at 10-Second Intervals – Positive (a), Negative (b)

#### Note

The surge test circuit used MOVs (Littelfuse V20E300P) connected from line and neutral filter inputs to chassis ground. See Figure 9-11.

## 9.3 Power Supply Recommendations

The TPSF12C3 AEF IC operates over a wide supply voltage range of 8 V to 16 V (typically 12 V) and is referenced to chassis ground of the system. The characteristics of this VDD bias supply must be compatible with the *Absolute Maximum Ratings* and *Recommended Operating Conditions* in this data sheet. In addition, the VDD supply must be capable of delivering the required supply current to the loaded AEF circuit.

The supply rail can already be present in the system or can be derived using a low-cost solution with an auxiliary winding from an isolated flyback regulator. Connect a ceramic capacitor of at least 1  $\mu$ F close to the VDD and IGND pins of the TPSF12C3. Ensure that the ripple voltage at VDD is less than 20 mV peak-to-peak to avoid low-frequency noise amplification.

#### 9.4 Layout

Proper PCB design and layout is important in active EMI circuits (where high regulator voltage and current slew rates exist) to achieve reliable device operation and design robustness. Furthermore, the EMI performance of the design depends to a large extent on PCB layout.

## 9.4.1 Layout Guidelines

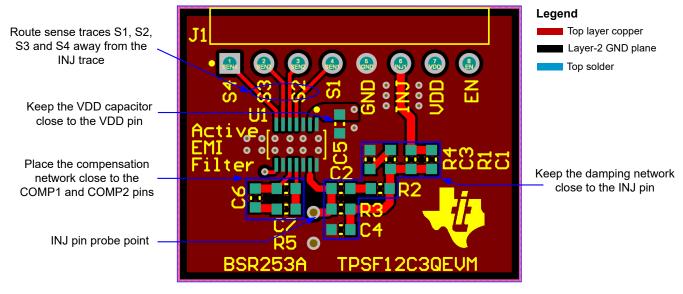

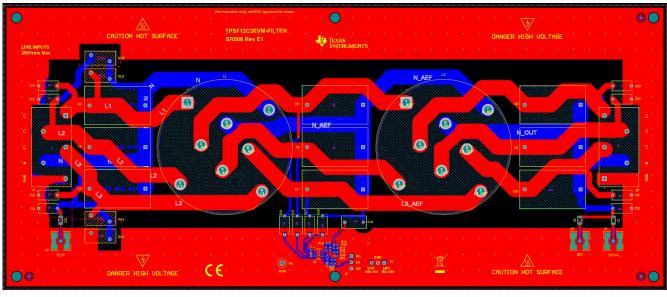

The following list summarizes the essential guidelines for PCB layout and component placement to optimze AEF performance. Figure 9-9 and Figure 9-10 show a recommended layout for the TPSF12C3 circuit specifically with optimized placement and routing of the IC and small-signal components. Figure 9-11 shows an example of a three-phase, four-wire filter board design with CM chokes, X-capacitors, Y-capacitors, protection components (varistors and X-capacitor discharge resistors), and AEF circuit.

- Position the sense and inject capacitors between the CM chokes near the X-capacitor that couples the injected signal to the other power lines. Avoid placement close to the CM choke windings that may result in parasitic coupling to the sense and inject capacitors.

- Maintain adequate clearance spacing between high-voltage and low-voltage traces. As an example, Figure

9-11 has 150 mils (3.8 mm) copper-to-copper spacing from power lines (lives and neutral) to chassis ground.

- Route the sense lines S1, S2, S3 and S4 away from the INJ line. Avoid coupling between the sense and inject traces.

- Use a solid ground connection between the TPSF12C3 and the filter board. Minimize parasitic inductance from the AEF circuit return to the chassis ground connections on the board.

- Place a ceramic capacitor close to VDD and IGND. Minimize the loop area to the VDD and IGND pins.

- Place the compensation network copnponents close to the COMP1 and COMP2 pins. Reduce noise

sensitivity of the feedback compensation network path by placing components R<sub>G</sub>, C<sub>G1</sub> and C<sub>G2</sub> close to

the COMP pins. COMP2 is the inverting input to the AEF anplifier and represents a high-impedance node

sensitive to noise.

Provide enough PCB area for proper heatsinking. Use sufficient copper area to acheive a low thermal

impedance. Provide adequate heatsinking for the TPSF12C3 to keep the junction temperature below 150°C.

A top-side ground plane is an important heat-dissipating area. Use several heat-sinking vias to connect

REFGND (pin 9) and IGND (pin 14) to ground copper on other layers.

## 9.4.2 Layout Example

Figure 9-9. Typical Layout

Figure 9-10. Typical Top-Layer Design

## Legend

Top layer copper

Bottom layer copper

Top solder

Figure 9-11. Typical Three-Phase Filter Board Design With AEF

## 10 Device and Documentation Support

## 10.1 Device Support

## 10.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 10.1.2 Development Support

All AEF devices from the family shown in Table 10-1 are rated for a maximum junction temperature of 150°C and are functional safety-capable. See the Texas Instruments power-supply filter ICs landing page for more detail.

| Table 10-1. | Common-mode | <b>AEF IC</b> | Family |

|-------------|-------------|---------------|--------|

|-------------|-------------|---------------|--------|

| DEVICE      | ORDERABLE PART NUMBER | PHASES | GRADE      | JUNCTION TEMPERATURE RANGE |

|-------------|-----------------------|--------|------------|----------------------------|

| TPSF12C3    | TPSF12C3DYYR          | 3      | Commercial | –40°C to 150°C             |

| TPSF12C1    | TPSF12C1DYYR          | 1      | Commercial | –40°C to 150°C             |

| TPSF12C3-Q1 | TPSF12C3QDYYRQ1       | 3      | Automotive | –40°C to 150°C             |

| TPSF12C1-Q1 | TPSF12C1QDYYRQ1       | 1      | Automotive | –40°C to 150°C             |

#### For development support see the following:

- TPSF12C3 guickstart calculator

- TPSF12C3 EVM Altium layout source files

- TPSF12C3 PSPICE for TI and SIMPLIS simulation models

- TPSF12C3 EVM user's guide

- · For TI's reference design library, visit TI Reference Design library

- To design a low-EMI power supply, review TI's comprehensive EMI Training Series

- TI Reference Designs:

- 3-kW, 180-W/in3 single-phase totem-pole bridgeless PFC reference design with 16-A max input

- 1-kW reference design with CCM totem pole PFC and current-mode LLC realized by C2000™ and GaN

- 7.4-kW on-board charger reference design with CCM totem pole PFC and CLLLC DC/DC using C2000™ MCU

- GaN-based, 6.6-kW, bidirectional, onboard charger reference design

- 10-kW, bidirectional three-phase three-level (T-type) inverter and PFC reference design

- Technical Articles:

- Texas Instruments, How a stand-alone active EMI filter IC shrinks common-mode filter size

- Texas Instruments, How device-level features and package options can help minimize EMI in automotive designs

- Texas Instruments, How to use slew rate for EMI control

- White Papers:

- Texas Instruments, How Active EMI Filter ICs Mitigate Common-Mode Emissions and Save PCB Space in Single- and Three-Phase Systems

- Texas Instruments, An Overview of Conducted EMI Specifications for Power Supplies

- Texas Instruments, An Overview of Radiated EMI Specifications for Power Supplies

- Video:

- Texas Instruments, Single- and three-phase active EMI filter ICs mitigate common-mode EMI, save space and reduce cost

- To view a related device of this product, see the TPSF12C1 single-phase active EMI filter for common-mode noise mitigation or refer to the Texas Instruments power-supply filter ICs landing page

## **10.2 Documentation Support**

#### 10.2.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, TI pioneers the industry's first stand-alone active EMI filter ICs, supporting high-density power supply designs press release

- Texas Instruments, An Engineer's Guide To EMI In DC/DC Regulators e-book

- Texas Instruments, Reduce Buck Converter EMI and Voltage Stress by Minimizing Inductive Parasitics ADJ article

- · Texas Instruments, Designing High Performance, Low-EMI, Automotive Power Supplies application report

- Texas Instruments, EMI Filter Components And Their Nonidealities For Automotive DC/DC Regulators technical brief

## 10.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 10.4 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 10.5 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

#### 10.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 10.7 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

## 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this datasheet, refer to the left-hand navigation.

Submit Document Feedback

www.ti.com 31-Oct-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins            | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|---------------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                           |                       |      | (4)                           | (5)                        |              |                  |

| TPSF12C3DYYR          | Active | Production    | SOT-23-THIN<br>(DYY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 150   | TPSF12C3         |

| TPSF12C3DYYR.A        | Active | Production    | SOT-23-THIN<br>(DYY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 150   | TPSF12C3         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPSF12C3:

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## PACKAGE OPTION ADDENDUM

www.ti.com 31-Oct-2025

• Automotive : TPSF12C3-Q1

NOTE: Qualified Version Definitions:

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-May-2023

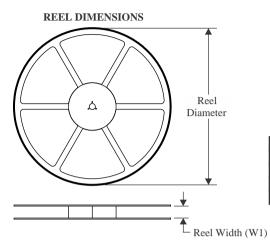

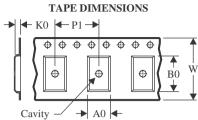

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

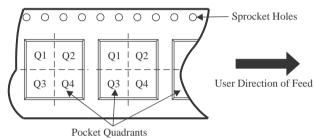

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       |                 | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPSF12C3DYYR | SOT-23-<br>THIN | DYY                | 14 | 3000 | 330.0                    | 12.4                     | 4.8        | 3.6        | 1.6        | 8.0        | 12.0      | Q3               |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-May-2023

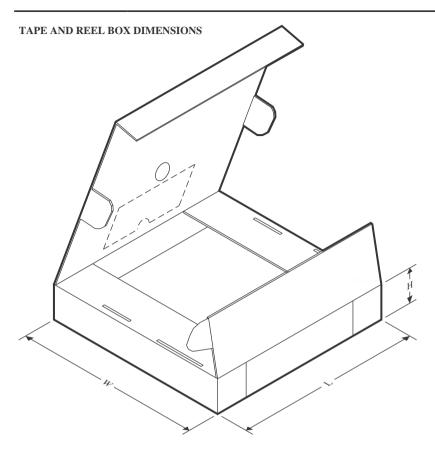

## \*All dimensions are nominal

|   | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı | TPSF12C3DYYR | SOT-23-THIN  | DYY             | 14   | 3000 | 336.6       | 336.6      | 31.8        |

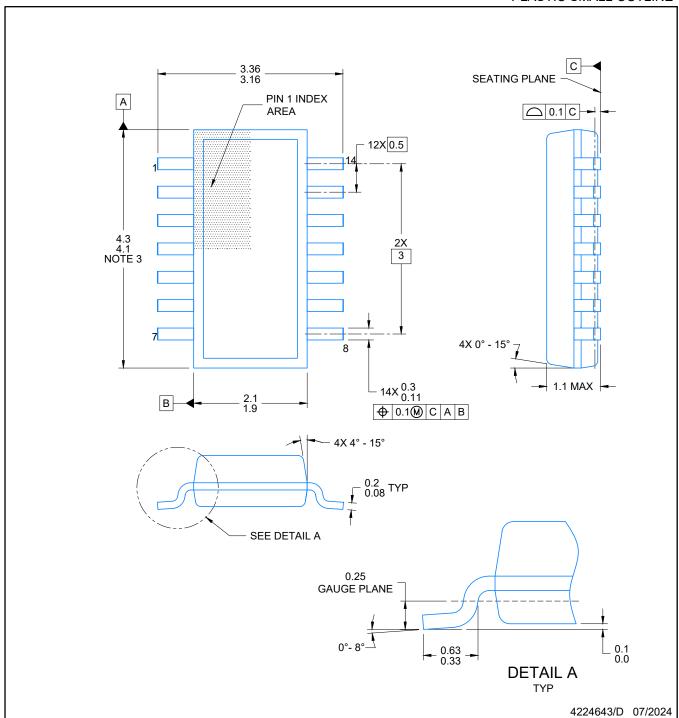

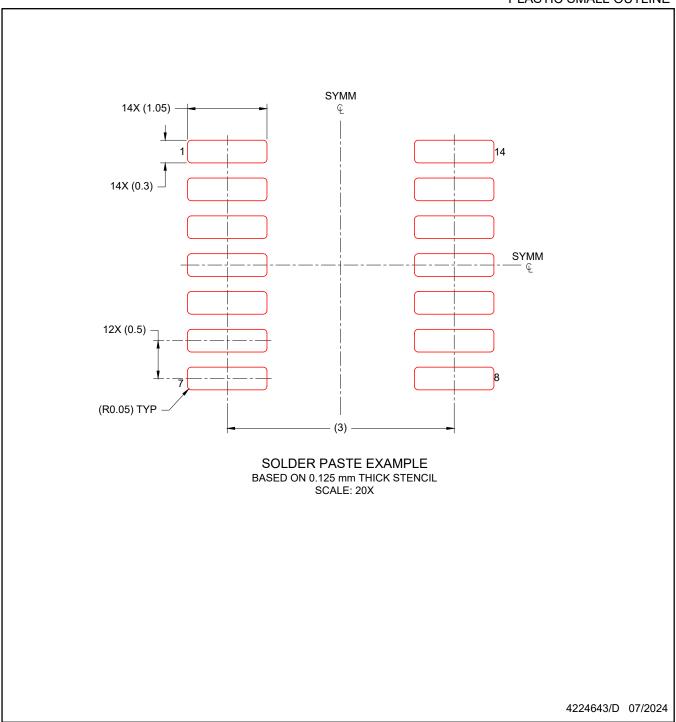

PLASTIC SMALL OUTLINE

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per side

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- 5. Reference JEDEC Registration MO-345, Variation AB

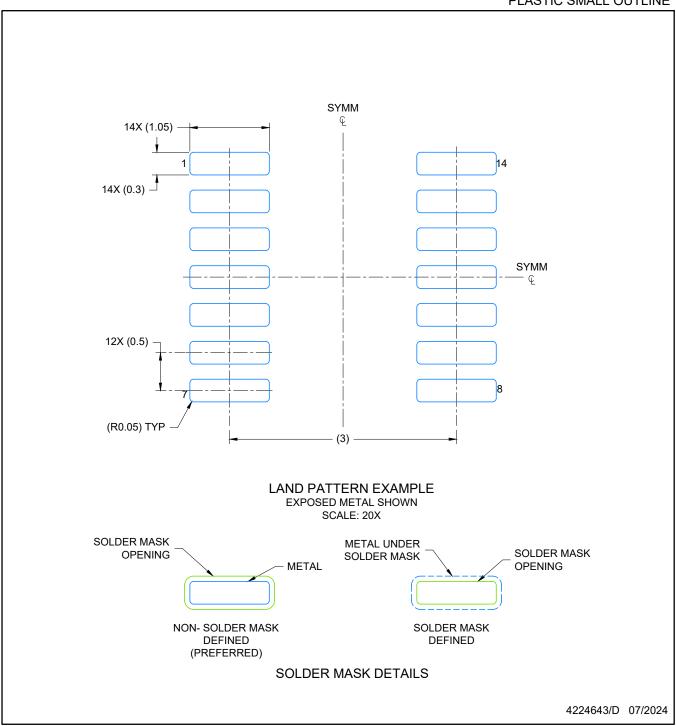

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025