DLPS133B - JUNE 2019 - REVISED JULY 2024

# **TPS99001-Q1 System Management Controller**

### 1 Features

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Temperature grade 2: -40°C to 105°C ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- Automotive system management device for DLP® products:

- Advanced power monitoring, sequencing, and protection circuits

- Two die temperature monitors, MCU external watchdog timer, and clock frequency monitor

- SPI port with parity, checksum, and password register protection

- Second SPI port for independent system monitoring

- On-chip DMD mirror voltage regulators

- Generates +16V, +8.5V, and –10V DMD control

- 12-bit ADC with up to 63 time sequence samples per frame

# 2 Applications

- Automotive advanced lighting applications (high resolution headlight)

- Adaptive driving beam (ADB)

## 3 Description

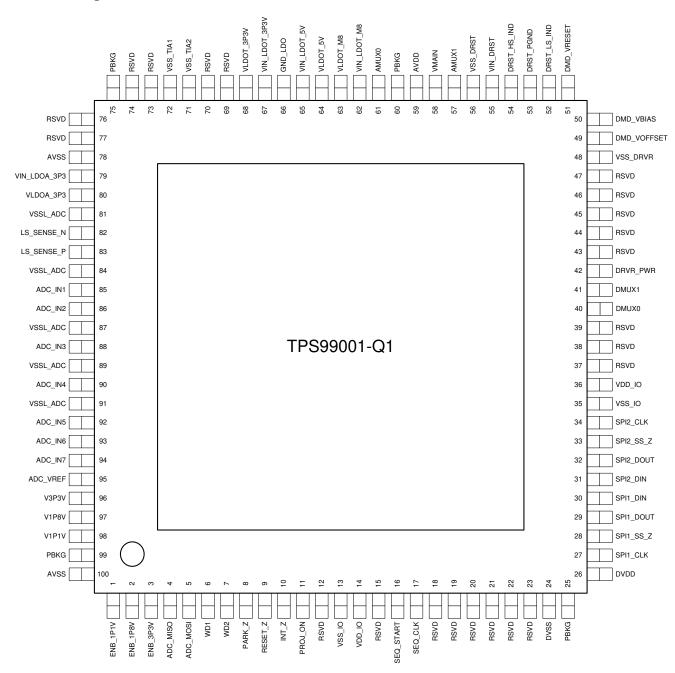

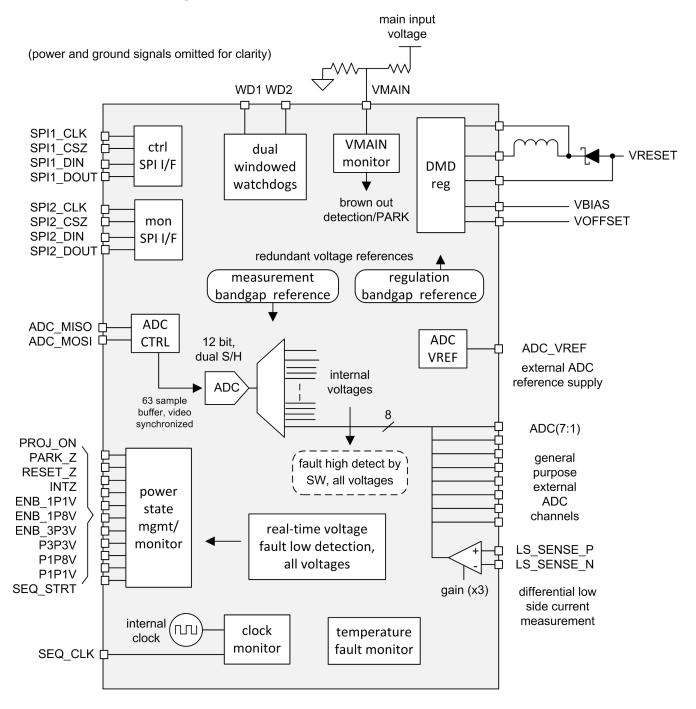

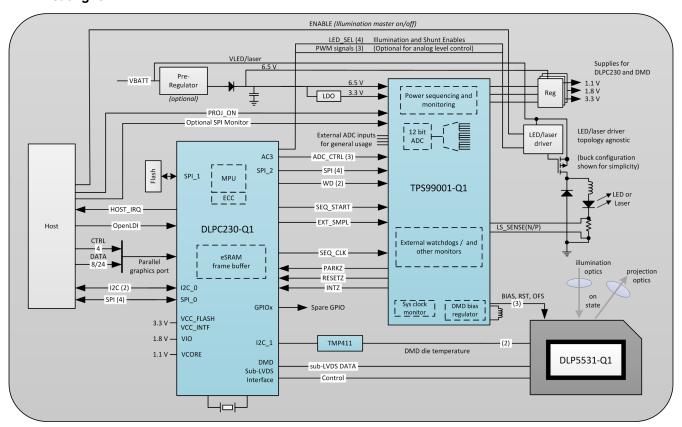

The TPS99001-Q1 system management controller is part of the DLP553x-Q1 and DLP462x-Q1 chipset, which also includes the DLPC23x-Q1 DMD display controller. An integrated DMD high-voltage regulator supplies DMD mirror reference voltages, meeting the required tight tolerances. The power supply sequencer and monitor provide robust coordination of power-up and power-down events for the entire chipset.

The TPS99001-Q1 controller integrates a 12-bit ADC as one of the core components of the control system. The ADC is capable of automatic sampling up to 63 events per video frame.

Advanced system status monitoring circuits provide real-time visibility into display sub-system operational condition, including two processor watchdog circuits, temperature monitors, comprehensive two die supply monitoring for overvoltage and undervoltage detection, checksum and password register protection with byte-level parity on SPI bus transactions, and other built-in test functions.

To aid in the design and manufacture of automotivequalified projectors based on DLP technology, there are several established optical module manufacturers and design houses that can be leveraged to support your design.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE      |  |  |

|-------------|------------------------|-------------------|--|--|

| TPS99001-Q1 | HTQFP (100)            | 14.00mm × 14.00mm |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

**Typical Standalone System**

# **Table of Contents**

|   | Features                                                        |      |

|---|-----------------------------------------------------------------|------|

|   | Applications                                                    |      |

|   | DescriptionPin Configuration and Functions                      |      |

|   | Specifications                                                  |      |

| _ | 5.1 Absolute Maximum Ratings                                    |      |

|   | 5.2 ESD Ratings                                                 |      |

|   | 5.3 Recommended Operating Conditions                            |      |

|   | 5.4 Thermal Information                                         | . 11 |

|   | 5.5 Electrical Characteristics—Analog to Digital                |      |

|   | Converter                                                       |      |

|   | 5.6 Electrical Characteristics—Voltage Regulators               | .13  |

|   | 5.7 Electrical Characteristics—Temperature and Voltage Monitors | 11   |

|   | 5.8 Electrical Characteristics—Current Consumption              |      |

|   | 5.9 Power-Up Timing Requirements                                |      |

|   | 5.10 Power-Down Timing Requirements                             |      |

|   | 5.11 Timing Requirements—Sequencer Clock                        |      |

|   | 5.12 Timing Requirements—Host and Diagnostic                    |      |

|   | Port SPI Interface                                              | 20   |

|   | 5.13 Timing Requirements—ADC Interface                          |      |

| _ | 5.14 Switching Characteristics                                  |      |

| 6 | Detailed Description                                            |      |

|   | 6.1 Overview                                                    | .21  |

| 6.2 Functional Block Diagram                          | .22  |

|-------------------------------------------------------|------|

| 6.3 Feature Description                               | .23  |

| 6.4 Device Functional Modes                           |      |

| 6.5 Register Maps                                     | .32  |

| 7 Application and Implementation                      |      |

| 7.1 Application Information                           |      |

| 7.2 Typical Applications                              |      |

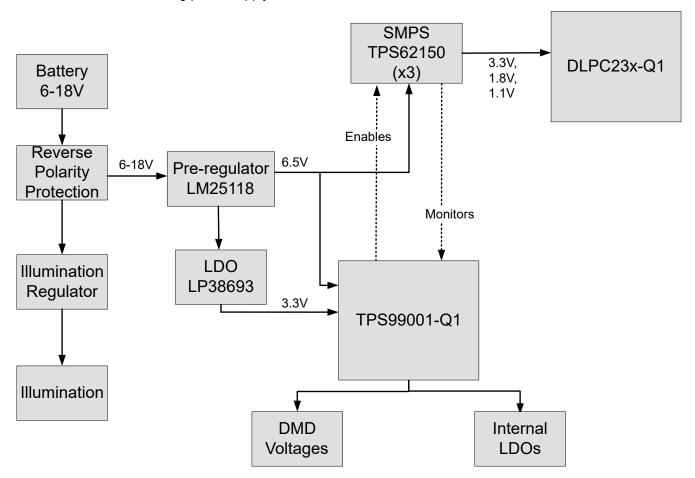

| 8 Power Supply Recommendations                        |      |

| 8.1 TPS99001-Q1 Power Supply Architecture             |      |

| 8.2 TPS99001-Q1 Power Outputs                         |      |

| 8.3 Power Supply Architecture                         |      |

| 9 Layout                                              |      |

| 9.1 Layout Guidelines                                 |      |

| 10 Device and Documentation Support                   |      |

| 10.1 Device Support                                   |      |

| 10.2 Receiving Notification of Documentation Updates. |      |

| 10.3 Support Resources                                |      |

| 10.4 Trademarks                                       |      |

| 10.5 Electrostatic Discharge Caution                  |      |

| 10.6 Glossary                                         |      |

| 11 Revision History                                   |      |

|                                                       | . 42 |

| 12 Mechanical, Packaging, and Orderable               | 42   |

| Information                                           | . 43 |

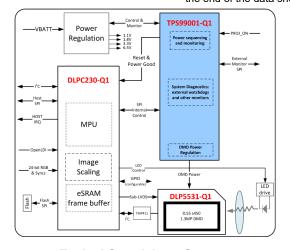

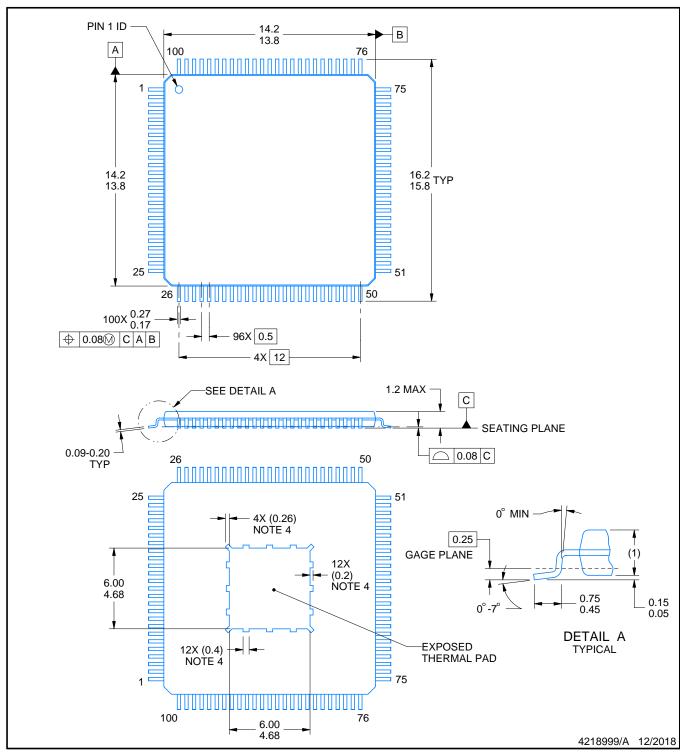

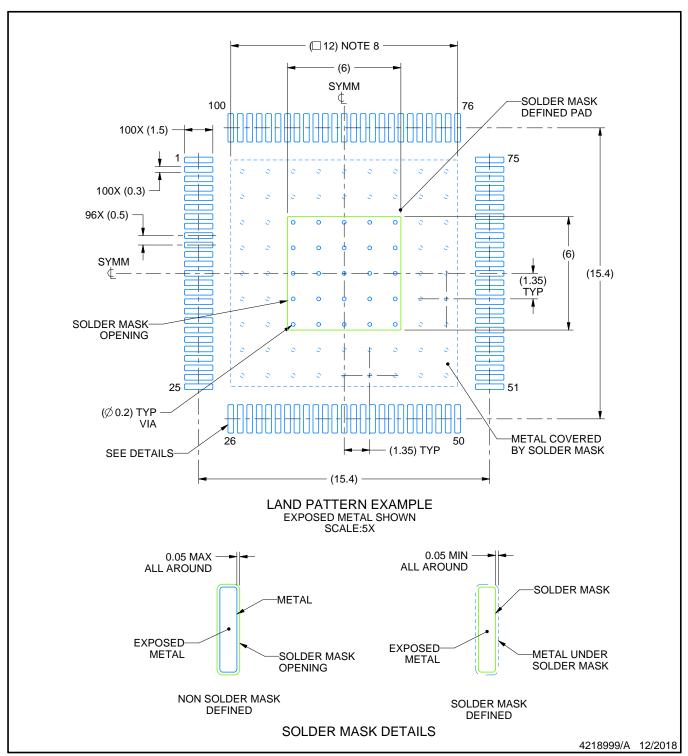

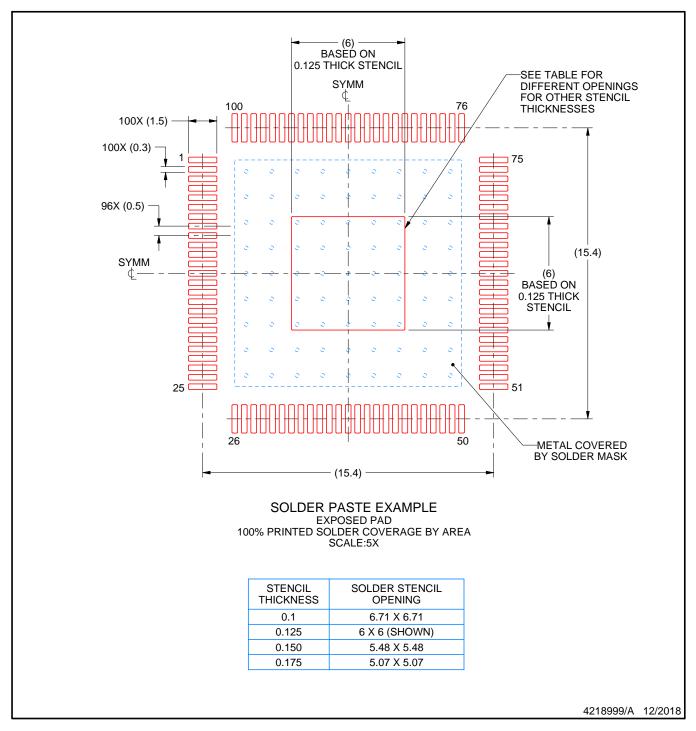

# 4 Pin Configuration and Functions

Figure 4-1. PZP Package 100-Pin HTQFP Top View

# Table 4-1. Pin Functions—Initialization, Clock, and Diagnostics

|     | PIN       | TVDE | DESCRIPTION                                                                                                                                             |  |  |

|-----|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME      | TYPE | DESCRIPTION                                                                                                                                             |  |  |

| 6   | WD1       | ı    | Watchdog interrupt channel 1                                                                                                                            |  |  |

| 7   | WD2       | I    | Watchdog interrupt channel 2                                                                                                                            |  |  |

| 8   | PARK_Z    | 0    | DMD mirror parking signal (active low)                                                                                                                  |  |  |

| 9   | RESET_Z   | 0    | Reset output to the DLPC23x-Q1. TPS99001-Q1 controlled.                                                                                                 |  |  |

| 10  | INT_Z     | 0    | Interrupt output signal to DLPC23x-Q1 (open drain). Recommended to pull up to the DLPC23x-Q1 3.3V rail controlled by the TPS99001-Q1's ENB_3P3V signal. |  |  |

| 11  | PROJ_ON   | I    | Input signal to enable/disable the IC and DLP projector                                                                                                 |  |  |

| 16  | SEQ_START | I    | PWM shadow latch control; indicates a start of sequence                                                                                                 |  |  |

| 17  | SEQ_CLK   | I    | Sequencer clock                                                                                                                                         |  |  |

| 40  | DMUX0     | 0    | Digital test point output                                                                                                                               |  |  |

| 41  | DMUX1     | 0    | Digital test point output                                                                                                                               |  |  |

| 57  | AMUX1     | 0    | Analog test mux output 1                                                                                                                                |  |  |

| 61  | AMUX0     | 0    | Analog test mux output 0                                                                                                                                |  |  |

## Table 4-2. Pin Functions—Power and Ground

|                    | PIN           | 7/05  | DECORPTION                                                                                                                                          |

|--------------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                | NAME          | TYPE  | DESCRIPTION                                                                                                                                         |

| 13, 35             | VSS_IO        | GND   | Ground connection for digital IO interface                                                                                                          |

| 14, 36             | VDD_IO        | POWER | 3.3V power input for IO rail supply                                                                                                                 |

| 24                 | DVSS          | GND   | Digital core ground return                                                                                                                          |

| 25, 60, 75, 99     | PBKG          | GND   | Substrate tie and ESD ground return                                                                                                                 |

| 26                 | DVDD          | POWER | 3.3V power input for digital core supply                                                                                                            |

| 42                 | DRVR_PWR      | POWER | 6V power input                                                                                                                                      |

| 48                 | VSS_DRVR      | GND   | Ground connection for driver power                                                                                                                  |

| 49                 | DMD_VOFFSET   | POWER | VOFFSET output rail. Connect a 1µF ceramic capacitor to ground                                                                                      |

| 50                 | DMD_VBIAS     | POWER | VBIAS output rail. Connect a 0.47µF ceramic capacitor to ground                                                                                     |

| 51                 | DMD_VRESET    | POWER | VRESET output rail. Connect a 1µF ceramic capacitor to ground. Connect to DRST_HS_IND through external diode. Connect anode of diode to DMD_VRESET. |

| 53                 | DRST_PGND     | GND   | Power ground for DMD power supply. Connect to ground plane                                                                                          |

| 55                 | VIN_DRST      | POWER | 6V input for DMD power supply                                                                                                                       |

| 56                 | VSS_DRST      | GND   | Ground supply for DMD power supply                                                                                                                  |

| 59                 | AVDD          | POWER | 3.3V power supply input for analog circuit                                                                                                          |

| 63                 | VLDOT_M8      | POWER | Unused. Leave open or unconnected.                                                                                                                  |

| 64                 | VLDOT_5V      | POWER | Filter cap interface for 5V LDO                                                                                                                     |

| 65                 | VIN_LDOT_5V   | POWER | 6V power input for 5V LDO                                                                                                                           |

| 66                 | GND_LDO       | GND   | Power ground return for LDO                                                                                                                         |

| 67                 | VIN_LDOT_3P3V | POWER | 6V power input for 3.3V LDO                                                                                                                         |

| 68                 | VLDOT_3P3V    | POWER | Filter cap interface for 3.3V LDO                                                                                                                   |

| 71                 | VSS_TIA2      | GND   | Ground                                                                                                                                              |

| 72                 | VSS_TIA1      | GND   | Ground                                                                                                                                              |

| 78, 100            | AVSS          | GND   | Analog ground                                                                                                                                       |

| 79                 | VIN_LDOA_3P3  | POWER | 6V power input for dedicated ADC interface 3.3V LDO supply                                                                                          |

| 80                 | VLDOA_3P3     | POWER | Dedicated ADC interface 3.3V LDO filter cap output                                                                                                  |

| 81, 84, 87, 89, 91 | VSSL_ADC      | GND   | External ADC channel bondwire and lead frame isolation ground                                                                                       |

| 95                 | ADC_VREF      | POWER | ADC reference voltage output                                                                                                                        |

# Table 4-3. Pin Functions—Power Supply Management

|     | PIN         | TVDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DESCRIPTION                                                                                                             |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | B_1P1V O External 1.1V buck enable. 3.3V output  B_1P8V O External 1.8V buck enable. 3.3V output  B_3P3V O External 3.3V buck enable. 3.3V output  C_LS_IND ANA Connection for the DMD power supply inductor (10μH). Connect a 330pF, 50 capacitor to ground. X7R recommended  C_HS_IND ANA Connection for the DMD power supply inductor (10μH)  MAIN I Main intermediate voltage monitor input. Use an external resistor divider to s input for brownout monitoring.  DOT_M8 O Unused. Leave open or unconnected.  External 3.3V buck voltage monitor input | DESCRIPTION                                                                                                             |

| 1   | ENB_1P1V    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External 1.1V buck enable. 3.3V output                                                                                  |

| 2   | ENB_1P8V    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External 1.8V buck enable. 3.3V output                                                                                  |

| 3   | ENB_3P3V    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External 3.3V buck enable. 3.3V output                                                                                  |

| 52  | DRST_LS_IND | ANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Connection for the DMD power supply inductor (10µH). Connect a 330pF, 50V capacitor to ground. X7R recommended          |

| 54  | DRST_HS_IND | ANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Connection for the DMD power supply inductor (10µH)                                                                     |

| 58  | VMAIN       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Main intermediate voltage monitor input. Use an external resistor divider to set voltage input for brownout monitoring. |

| 62  | VIN_LDOT_M8 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Unused. Leave open or unconnected.                                                                                      |

| 96  | V3P3V       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External 3.3V buck voltage monitor input                                                                                |

| 97  | V1P8V       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External 1.8V buck voltage monitor input                                                                                |

| 98  | V1P1V       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External 1.1V buck voltage monitor input                                                                                |

## Table 4-4. Pin Functions—Reserved Pins

|     | PIN      | TYPE | DESCRIPTION                  |

|-----|----------|------|------------------------------|

| NO. | NAME     | ITPE | DESCRIPTION                  |

| 12  | Reserved | 0    | Reserved. Leave unconnected. |

| 15  | Reserved | 0    | Reserved. Leave unconnected. |

| 18  | Reserved | I    | Reserved. Connect to ground. |

| 19  | Reserved | I    | Reserved. Connect to ground. |

| 20  | Reserved | I    | Reserved. Connect to ground. |

| 21  | Reserved | I    | Reserved. Connect to ground. |

| 22  | Reserved | I    | Reserved. Connect to ground. |

| 23  | Reserved | I    | Reserved. Connect to ground. |

| 37  | Reserved | I    | Reserved. Connect to ground  |

| 38  | Reserved | 0    | Reserved. Leave unconnected. |

| 39  | Reserved | 0    | Reserved. Leave unconnected. |

| 43  | Reserved | 0    | Reserved. Leave unconnected. |

| 44  | Reserved | 0    | Reserved. Leave unconnected. |

| 45  | Reserved | 0    | Reserved. Leave unconnected. |

| 46  | Reserved | 0    | Reserved. Leave unconnected. |

| 47  | Reserved | 0    | Reserved. Leave unconnected. |

| 69  | Reserved | 0    | Reserved. Leave unconnected. |

| 70  | Reserved | I    | Reserved. Leave unconnected. |

| 73  | Reserved | I    | Reserved. Leave unconnected. |

| 74  | Reserved | 0    | Reserved. Leave unconnected. |

| 76  | Reserved | ANA  | Reserved. Connect to ground. |

| 77  | Reserved | ANA  | Reserved. Connect to ground. |

## Table 4-5. Pin Functions—Serial Peripheral Interfaces

|     | PIN       | TYPE | DESCRIPTION                                                                                 |  |

|-----|-----------|------|---------------------------------------------------------------------------------------------|--|

| NO. | NAME      | ITPE | DESCRIPTION                                                                                 |  |

| 27  | SPI1_CLK  | I    | SPI control interface (DLPC23x-Q1 primary, TPS99001-Q1 secondary), clock input              |  |

| 28  | SPI1_SS_Z | I    | SPI control interface (DLPC23x-Q1 primary, TPS99001-Q1 secondary), chip select (active low) |  |

| 29  | SPI1_DOUT | 0    | I control interface (DLPC23x-Q1 primary, TPS99001-Q1 secondary), transmit data put          |  |

| 30  | SPI1_DIN  | I    | PI control interface (DLPC23x-Q1 primary, TPS99001-Q1 secondary), receive data out          |  |

| 31  | SPI2_DIN  | I    | SPI diagnostic port (secondary), receive data input. For read-only monitoring               |  |

| 32  | SPI2_DOUT | 0    | SPI diagnostic port (secondary), transmit data output. For read-only monitoring             |  |

| 33  | SPI2_SS_Z | I    | SPI diagnostic port (secondary), chip select (active low). For read-only monitoring         |  |

| 34  | SPI2_CLK  | I    | SPI diagnostic port (secondary), clock input. For read-only monitoring                      |  |

# Table 4-6. Pin Functions—Analog to Digital Converter

|     | PIN        | TYPE | DESCRIPTION                                                                    |

|-----|------------|------|--------------------------------------------------------------------------------|

| NO. | NAME       | ITPE | DESCRIPTION                                                                    |

| 4   | ADC_MISO   | 0    | ADC 2-wire interface - data output. DLPC23x-Q1 primary, TPS99001-Q1 secondary. |

| 5   | ADC_MOSI   | Į.   | ADC 2-wire interface - data input. DLPC23x-Q1 primary, TPS99001-Q1 secondary.  |

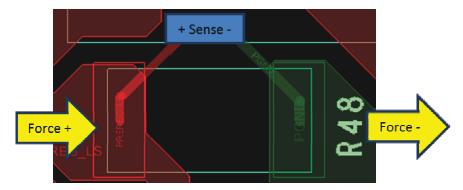

| 82  | LS_SENSE_N | I    | Low side current sense ADC negative input, see Table 6-1                       |

| 83  | LS_SENSE_P | I    | Low side current sense ADC positive input, see Table 6-1                       |

| 85  | ADC_IN1    | I    | External ADC channel 1, see Table 6-1                                          |

| 86  | ADC_IN2    | Į.   | External ADC channel 2, see Table 6-1                                          |

| 88  | ADC_IN3    | Į.   | External ADC channel 3, see Table 6-1                                          |

| 90  | ADC_IN4    | Į.   | External ADC channel 4, see Table 6-1                                          |

| 92  | ADC_IN5    | Į.   | External ADC channel 5, see Table 6-1                                          |

| 93  | ADC_IN6    | I    | External ADC channel 6, see Table 6-1                                          |

| 94  | ADC_IN7    | I    | External ADC channel 7, see Table 6-1                                          |

## **5 Specifications**

## **5.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

| ·          | , , , , , , , , , , , , , , , , , , , ,                                                                                                                   | MIN  | MAX | UNIT |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

|            | VDD_IO to VSS_IO                                                                                                                                          | -0.3 | 4   |      |

|            | DVDD to DVSS                                                                                                                                              | -0.3 | 4   |      |

|            | AVDD to DVSS                                                                                                                                              | -0.3 | 4   |      |

|            | All "VSS" to other "VSS" (grounds)                                                                                                                        | -0.1 | 0.1 |      |

|            | All digital input signals to ground (WD1, WD2, ADC_MOSI, PROJ_ON, SEQ_START, SEQ_CLK, SPI1_CLK, SPI1_DIN, SPI1_SS, SPI2_DIN, SPI2_CLK, SPI2_SS, EXT_SMPL) | -0.3 | 3.6 |      |

|            | DRVR_PWR to ground                                                                                                                                        | -0.3 | 7.5 |      |

| Input      | VIN_LDO_5V                                                                                                                                                | -0.3 | 7.5 |      |

| voltage    | V3P3V to ground                                                                                                                                           | -0.3 | 5   | V    |

|            | V1P8V to ground                                                                                                                                           | -0.3 | 5   |      |

|            | V1P1V to ground                                                                                                                                           | -0.3 | 5   |      |

|            | VIN_LDOA_3P3 to ground                                                                                                                                    | -0.3 | 7.5 |      |

|            | VIN_LDOT_3P3 to ground                                                                                                                                    | -0.3 | 7.5 |      |

|            | ADC_IN(7:1) to ground                                                                                                                                     | -0.3 | 3.6 |      |

|            | DRST_LS_IND to DRST_PGND                                                                                                                                  | -0.3 | 27  |      |

|            | VIN_DRST to ground                                                                                                                                        | -0.3 | 7.5 |      |

|            | VMAIN                                                                                                                                                     | -0.3 | 7.5 |      |

| Outputs    | INT_Z                                                                                                                                                     | -0.3 | 7.5 | V    |

| Operating  | junction temperature, T <sub>J</sub>                                                                                                                      | -40  | 130 | °C   |

| Storage te | mperature, T <sub>stg</sub>                                                                                                                               | -65  | 150 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                    |                            |                                          |              | VALUE | UNIT |

|--------------------|----------------------------|------------------------------------------|--------------|-------|------|

|                    |                            | Human-body model (HBM), per AEC Q100-002 | <b>D</b> (1) | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged-device model (CDM), per AEC      | All pins     | ±500  | V    |

|                    |                            | Q100-011                                 | Corner pins  | ±750  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

Submit Document Feedback

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                                              | MIN | NOM | MAX | UNIT |

|----------------|----------------------------------------------|-----|-----|-----|------|

| TEMPERATURE    |                                              |     |     | '   |      |

| T <sub>A</sub> | Operating ambient temperature <sup>(1)</sup> | -40 |     | 105 | °C   |

| T <sub>J</sub> | Operating junction temperature               | -40 |     | 125 | °C   |

| VOLTAGE        |                                              |     |     |     |      |

| VDD_IO         | IO 3.3V voltage supply                       | 3   | 3.3 | 3.6 | V    |

| DVDD           | Digital 3.3V supply                          | 3   | 3.3 | 3.6 | V    |

| AVDD           | Analog 3.3V supply                           | 3   | 3.3 | 3.6 | V    |

| ADC            | ADC(7:1) inputs                              | 0.1 |     | 1.6 | V    |

| VIN_DRST       | DMD reset regulator input                    | 5.5 | 6   | 7   | V    |

| VIN_LDOT_5V    | Power supply input to 5V LDO                 | 5.5 | 6   | 7   | V    |

| VIN_LDOA_3P3V  | Power supply input to 3.3V ADC LDO           | 5.5 | 6   | 7   | V    |

| VIN_LDOT_3P3V  | Power supply input to 3.3V LDO               | 5.5 | 6   | 7   | V    |

| DRVR_PWR       | Gate driver power supply                     | 3   | 6   | 7   | V    |

<sup>(1) -40°</sup>C to 105°C ambient, free air convection, AEC Q100 grade 2.

### **5.4 Thermal Information**

|                        |                                              | TPS99001-Q1 |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup> (2)            | PZP (HTQFP) | UNIT |

|                        |                                              | 100 PINS    |      |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 6.9         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 8.3         | °C/W |

| Ψ <sub>JT</sub>        | Junction-to-top characterization parameter   | 0.1         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 8.2         | °C/W |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 0.4         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

<sup>(2)</sup> Operating ambient temperature is dependent on system thermal design. Operating junction temperature may not exceed its specified range across ambient temperature conditions.

# 5.5 Electrical Characteristics—Analog to Digital Converter

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                          | TEST CONDITIONS                          | MIN   | TYP   | MAX   | UNIT |

|---------------------------|------------------------------------|------------------------------------------|-------|-------|-------|------|

| 12-BIT ADC <sup>(1)</sup> |                                    |                                          |       |       |       |      |

| V <sub>INPUT</sub>        | Input range <sup>(2)</sup>         |                                          | 0.1   |       | 1.6   | V    |

| INL                       | Integral non-linearity             | Over valid input range VINPUT            | -4    |       | 4     | LSB  |

| DNL                       | Differential non-linearity         |                                          | -2.5  |       | 2.5   | LSB  |

| ENOB                      | Effective number Of bits           |                                          | 10    | 12    |       | bits |

| t <sub>SAMPLE</sub>       | S/H sampling period                |                                          | 0.4   | 5.2   | 12.8  | μs   |

| t <sub>DELAY</sub>        | S/H delay before conversion starts |                                          | 0.4   |       | 2.8   | μs   |

| t <sub>SHOLD</sub>        | S/H holding period                 |                                          |       | 102.4 | 245   | μs   |

| t <sub>CONV</sub>         | Conversion period                  |                                          |       | 102.4 |       | μs   |

| V <sub>REF</sub>          | Measurement reference              | ADC reference voltage is doubled to 1.6V | 0.784 | 0.8   | 0.816 | V    |

| V                         | Offset                             |                                          | -20   |       | 20    | LSB  |

| V <sub>OFFS</sub>         | Gain error                         | "ADC_IN(7:1) inputs                      | 2     |       | 2     | %FSR |

<sup>(1)</sup> ADC specifications refer to ADC core behavior, presume ideal clocks and IC input power conditions, unless otherwise noted.

Submit Document Feedback

<sup>(2)</sup> Results in invalid ADC codes below 256

## 5.6 Electrical Characteristics—Voltage Regulators

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                         | TEST CONDITIONS           | MIN    | TYP  | MAX                 | UNIT |

|------------------------|-----------------------------------|---------------------------|--------|------|---------------------|------|

| VOFFSET REGU           | JLATOR                            |                           |        |      |                     |      |

| V <sub>OUT</sub>       | Output voltage                    | Across load conditions    | 8.25   | 8.5  | 8.75                | V    |

| I <sub>OUT</sub>       | Output current <sup>(2)</sup>     |                           | 0.1(4) |      | 16.3                | mA   |

| V <sub>PGTHRESHR</sub> | Powergood threshold, VOUT rising  |                           |        | 86%  |                     |      |

| V <sub>PGTHRESHF</sub> | Powergood threshold, VOUT falling |                           |        | 66%  |                     |      |

| C <sub>OUT</sub>       | Output capacitor <sup>(3)</sup>   |                           |        | 1    |                     | μF   |

| T <sub>DISC</sub>      | Discharge time                    | C <sub>OUT</sub> = 1µF    |        |      | 260                 | μs   |

| VBIAS REGULA           | TOR                               |                           |        |      |                     |      |

| V <sub>OUT</sub>       | Output voltage                    |                           | 15.5   | 16   | 16.5                | V    |

| I <sub>OUT</sub>       | Output current <sup>(2)</sup>     |                           | 0.1(4) |      | 1.5                 | mA   |

| V <sub>PGTHRESHR</sub> | Powergood threshold, VOUT rising  |                           |        | 86%  |                     |      |

| V <sub>PGTHRESHF</sub> | Powergood threshold, VOUT falling |                           |        | 66%  |                     |      |

| C <sub>OUT</sub>       | Output capacitor <sup>(3)</sup>   |                           |        | 0.47 |                     | μF   |

| T <sub>DISC</sub>      | Discharge time                    | C <sub>OUT</sub> = 0.47µF |        |      | 260                 | μs   |

| VRESET REGUL           | _ATOR                             |                           |        |      |                     |      |

| V <sub>OUT</sub>       | Output voltage                    |                           | -10.5  | -10  | -9.5                | V    |

| I <sub>OUT</sub>       | Output current <sup>(1)</sup> (2) |                           | -17.6  |      | -0.1 <sup>(4)</sup> | mA   |

| V <sub>PGTHRESHR</sub> | Powergood threshold               |                           |        | 80%  |                     |      |

| C <sub>OUT</sub>       | Output capacitor <sup>(3)</sup>   |                           |        | 1    |                     | μF   |

| T <sub>DISC</sub>      | Discharge time                    | C <sub>OUT</sub> = 1µF    |        |      | 260                 | μs   |

- (1) VRESET current supplies both DMD and negative 8V LDO.

- (2) VOFFSET, VBIAS, and VRESET are designed to supply the DMD and negative 8V LDO only, and should not be connected to additional loads.

- (3) The capacitance value of some ceramic capacitor types can diminish drastically depending on the applied DC voltage and temperature. TI recommends X7R dielectric capacitors to minimize capacitance loss over voltage bias and temperatures. Using a higher voltage rated part and/or a larger package size also helps minimize the capacitance reduction at the applied DC voltage. Refer to the DLP5531Q1EVM for suggested components.

- (4) Pull down resistors required to meet minimum current requirement.

# 5.7 Electrical Characteristics—Temperature and Voltage Monitors

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                   | TEST CONDITIONS                                                          | MIN    | TYP  | MAX      | UNIT |

|-------------------------|-----------------------------|--------------------------------------------------------------------------|--------|------|----------|------|

| TEMPERATURE             | MONITOR                     |                                                                          |        |      |          |      |

| TEMP <sub>WARN</sub>    | Thermal warning threshold   | Junction temperature                                                     |        | 135  |          | °C   |

| TEMP <sub>EMRG</sub>    | Thermal emergency threshold | Junction temperature                                                     |        | 150  |          | °C   |

| 1.1-V SUPPLY N          | IONITOR                     |                                                                          |        |      | <u> </u> |      |

| V <sub>TRIPN</sub>      | Negative trip threshold     | Negative going only                                                      | 0.95   | 0.98 | 1.01     | V    |

| V <sub>TRIPHYST</sub>   | Hysteresis                  | Positive going threshold,<br>amount higher than negative trip<br>voltage |        | 2%   |          |      |

| t <sub>GLITCH</sub>     | Glitch suppression          | Size of glitch ignored (no reset) with 2% overdrive                      | 20     |      | 1000     | μs   |

| 1.8-V SUPPLY N          | IONITOR                     |                                                                          |        |      |          |      |

| V <sub>TRIPN</sub>      | Negative trip threshold     | Negative going only                                                      | 1.552  | 1.6  | 1.648    | V    |

| V <sub>TRIPHYST</sub>   | Hysteresis                  | Positive going threshold,<br>amount higher than negative trip<br>voltage |        | 2%   |          |      |

| t <sub>GLITCH</sub>     | Glitch suppression          | Size of glitch ignored (no reset) with 2% overdrive                      | 20     |      | 1000     | μs   |

| 3.3-V SUPPLY N          | IONITOR                     |                                                                          |        |      | <u>'</u> |      |

| V <sub>TRIPN</sub>      | Negative trip threshold     | Negative going only                                                      | 2.852  | 2.93 | 3.03     | V    |

| V <sub>TRIPHYST</sub>   | Hysteresis                  | Positive going threshold,<br>amount higher than negative trip<br>voltage |        | 2%   |          |      |

| t <sub>GLITCH</sub>     | Glitch suppression          | Size of glitch ignored (no reset) with 2% overdrive                      | 20     |      | 1000     | μs   |

| VMAIN SYSTEM            | I INPUT SUPPLY MONITOR      |                                                                          |        |      | '        |      |

| V <sub>MAINTHRSH</sub>  | VMAIN threshold             | External resistor divider used to translate VMAIN                        | 1.2125 | 1.25 | 1.2875   | V    |

| t <sub>MAINGLITCH</sub> | VMAIN glitch suppression    | At 2% overdrive                                                          | 20     |      | 1000     | μs   |

Submit Document Feedback

## 5.8 Electrical Characteristics—Current Consumption

| PARAMETER                                       | TEST CONDITIONS                        | MIN             | TYP <sup>(1)</sup> | MAX <sup>(2)</sup> | UNIT |  |  |  |

|-------------------------------------------------|----------------------------------------|-----------------|--------------------|--------------------|------|--|--|--|

| SUM OF 3.3V SUPPLY PINS: DVDD, VDD_IO, AND AVDD |                                        |                 |                    |                    |      |  |  |  |

| System off                                      | PROJ_ON low                            |                 | 1.5                | 2                  | mA   |  |  |  |

| System on                                       | Display ON state                       |                 | 3.5                | 4                  | mA   |  |  |  |

| SUM OF 6V SUPPLY PINS: DRV                      | R_PWR, VIN_DRST, VIN_LDOT_5V, VIN_LDOT | _3P3V, AND VIN_ | LDOA_3P3V          |                    |      |  |  |  |

| System off                                      | PROJ_ON low                            |                 | 1                  | 2                  | mA   |  |  |  |

| System on <sup>(3)</sup>                        | Display ON state                       |                 | 98                 | 119                | mA   |  |  |  |

- (1) Typical measurements performed at 25°C and nominal voltage

- (2) Measurements taken at -40°C, 25°C, and 105°C. 3.3V inputs measured at 3V, 3.3V, and 3.6V. 6V inputs measured at 5.5V, 6V, and 7V. The maximum current draw of all these conditions is shown.

- (3) This number represents the current at the input to the TPS99001-Q1 when the DMD voltage rails output the maximum current as listed in the respective sections of this data sheet. This number is the combination of the measured current when the DMD voltage regulator is unloaded (3mA typical, 56mA max) and the estimated current draw on the 6V supply when the DMD voltage regulator outputs the maximum current (63mA). The estimated current draw is calculated by the equation  $I_{6V} = [(16 / 6) \times I_{VBIAS} + (8.5 / 6) \times I_{VOFFSET} + (-10 / 6) \times I_{VRESET}] / \eta$  where  $\eta = 0.9$ . In order to calculate the power dissipation of the TPS99001-Q1 in this condition, multiply the current from the unloaded condition by the input voltage and add the current from the DMD voltage regulator multiplied by the input voltage multiplied by  $(1 \eta)$ .

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

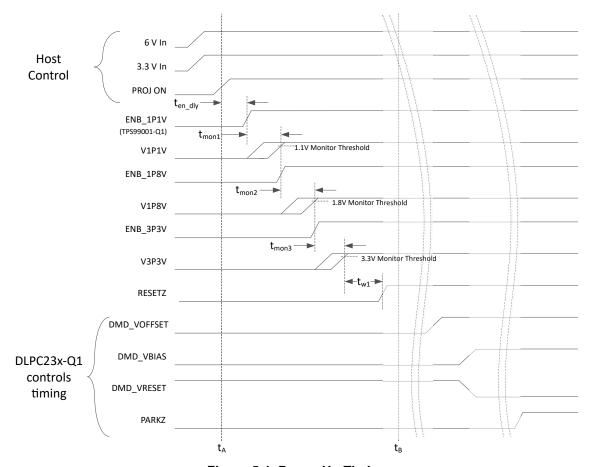

## 5.9 Power-Up Timing Requirements

|                           |                                                                                                                                                          |                                                                      | TYP | UNIT |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----|------|

| t <sub>en_dly</sub>       | PROJ_ON to 1.1V enable. This includes PROJ_ON $t_{\rm glitch}$ time.                                                                                     | Rising edge of PROJ_ON to rising edge of 1.1V enable                 | 11  | ms   |

| t <sub>mon1</sub> (1) (2) | Maximum time for 1.1V rail to reach voltage threshold after enable has been asserted. This delay length will occur even if 1.1V meets threshold earlier. | Rising edge of ENB_1P1V to internal 1.1V monitor test <sup>(3)</sup> | 10  | ms   |

| t <sub>mon2</sub> (1) (2) | Maximum time for 1.8V rail to reach voltage threshold after enable has been asserted. This delay length will occur even if 1.8V meets threshold earlier. | Rising edge of ENB_1P8V to internal 1.8V monitor test <sup>(3)</sup> | 10  | ms   |

| t <sub>mon3</sub> (1) (2) | Maximum time for 3.3V rail to reach voltage threshold after enable has been asserted. This delay length will occur even if 3.3V meets threshold earlier. | Rising edge of ENB_3P3V to internal 3.3V monitor test <sup>(3)</sup> | 10  | ms   |

| t <sub>w1</sub> (4)       | RESETZ delay after voltage testing completion.                                                                                                           | Completion of 3.3V monitor test to RESETZ rising edge                | 10  | ms   |

- (1) V1P1V, V1P8V, and V3P3V rails may be enabled prior to the TPS99001-Q1 assertion of their respective enable signal if required for system power design. If necessary, ENB\_1P1V may be connected to the 1.1V, 1.8V, and 3.3V external supply enables.

- (2) If any voltage threshold is not met within the specified time, the TPS99001-Q1 will not deassert RESETZ. The power-up procedure must be fully restarted in this situation.

- (3) Each TPS monitor *test* is performed approximately 10 ms from the voltage rail's respective voltage enable. The voltage rail may come to its threshold value any time before this. This means there should be approximately 10 ms between each enable. The time for the respective 1.1V, 1.8V, and 3.3V to come up will differ by design and parts chosen, but they must all be valid before the monitor test.

- (4) t<sub>w1</sub> starts after the 3.3V rail passes its internal monitor tests (~10 ms). This time does not start as soon as the 3.3V comes to its threshold value. This time starts after the internal TPS monitor check for 3.3V passes. After the test passes, there will be a 10 ms delay before RESETZ may be de-asserted. This means there will be approximately 20 ms delay from the time the 3.3V enable is valid to the time RESETZ is de-asserted.

Figure 5-1. Power Up Timing

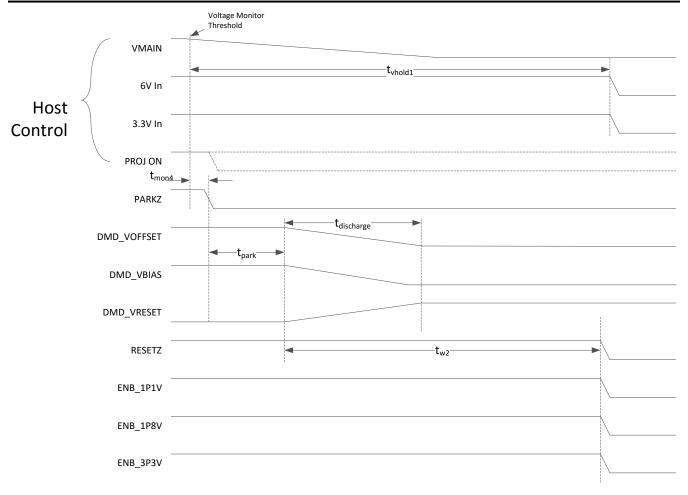

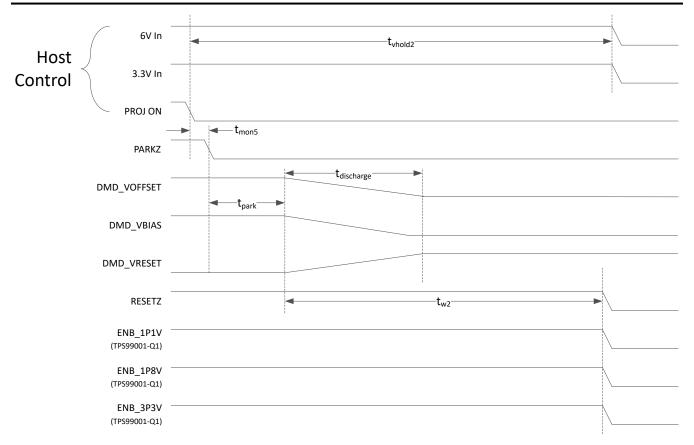

## 5.10 Power-Down Timing Requirements

## See (1)

|                               |                                                                                                                               |                                                                                                                                                                                       | MIN  | MAX | UNIT |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

| t <sub>vhold1</sub>           | Host voltage hold time after VMAIN minimum threshold reached. $t_{mon4}(max) + t_{park}(max) + t_{w2}(max)$                   | VMAIN threshold to 6V and 3.3V power loss <sup>(2)</sup> (3)                                                                                                                          | 900  |     | μs   |

| t <sub>vhold2</sub>           | Host voltage hold time after PROJ_ON deasserted.<br>t <sub>mon5</sub> (max) + t <sub>park</sub> (max) + t <sub>w2</sub> (max) | VMAIN threshold to 6V and 3.3V power loss. <sup>(2) (3)</sup>                                                                                                                         | 1.78 |     | ms   |

| t <sub>mon4</sub>             | VMAIN monitoring time                                                                                                         | Minimum voltage trip threshold to PARKZ falling edge                                                                                                                                  | 52   | 120 | μs   |

| t <sub>mon5</sub>             | PROJ_ON deassertion reaction time                                                                                             | Falling edge of PROJ_ON to PARKZ falling edge                                                                                                                                         |      | 1   | ms   |

| t <sub>park</sub>             | DMD Park time                                                                                                                 | PARKZ falling edge to start DMD_VOFFSET discharge                                                                                                                                     |      | 280 | μs   |

| t <sub>discharge</sub><br>(4) | DMD voltage rail discharge time                                                                                               | $\begin{aligned} &\text{VOFFSET C}_{\text{out}} = 1 \mu \text{F} \\ &\text{VRESET C}_{\text{out}} = 1 \mu \text{F} \\ &\text{VBIAS C}_{\text{out}} = 0.47 \mu \text{F} \end{aligned}$ |      | 260 | μs   |

| t <sub>w2</sub>               | DMD voltage disables to RESETZ deassertion                                                                                    | Start of DMD voltage rail discharge to RESETZ falling edge                                                                                                                            |      | 500 | μs   |

- (1) There are two methods for initiating the power-down sequence:

- a. VMAIN voltage decreases below its minimum threshold. This is typical if the TPS99001-Q1 is expected to initiate the power-down sequence when the main power is removed from the system. Note that the 6V and 3.3V input rails must remain within the operating range for a specified period of time after the power-down sequence begins.

- b. PROJ\_ON low. This allows a host controller to initiate power down through a digital input to the TPS99001-Q1.

- 2) 6V input rails include DRVR\_PWR, VIN\_DRST, VIN\_LDOT\_5V, VIN\_LDOA\_3P3V, VIN\_LDOT3P3V.

- (3) 3.3V input rails include VDD IO, DVDD, AVDD.

- (4) The DMD specifies a maximum absolute voltage difference between VBIAS and VOFFSET. To remain below this maximum voltage difference, VBIAS must discharge faster than VOFFSET. This is accomplished by using a smaller C<sub>out</sub> capacitance for VBIAS to allow it to discharge quicker than VOFFSET.

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

Figure 5-2. Power Down Timing—VMAIN Trigger

Figure 5-3. Power Down Timing—PROJ\_ON Trigger

# 5.11 Timing Requirements—Sequencer Clock

|                       |                                                    | MIN | NOM M | ٩X | UNIT  |

|-----------------------|----------------------------------------------------|-----|-------|----|-------|

| $f_{\sf SEQ\_CLK}$    | SEQ_CLK Frequency                                  |     | 30.00 |    | MHz   |

| t <sub>JPP</sub>      | SEQ_CLK Jitter (peak to peak)                      | -3% | ;     | 3% |       |

| $f_{SS}$              | SEQ_CLK allowable spread spectrum                  | -2% | (     | )% |       |

| $f_{	extsf{SSMOD}}$   | SEQ_CLK Spread Spectrum Modulation Frequency       | 25  | 1     | 00 | kHz   |

| $f_{	extsf{SSSTEPS}}$ | SEQ_CLK Spread Spectrum Modulation Frequency Steps |     | 50    |    | steps |

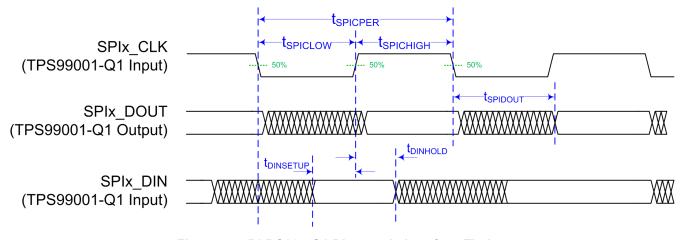

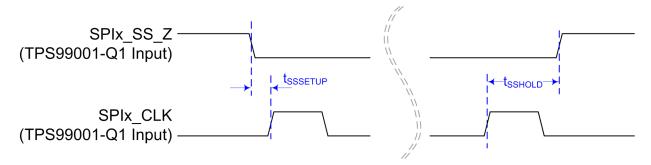

# 5.12 Timing Requirements—Host and Diagnostic Port SPI Interface

|                       |                                   | MIN | NOM | MAX | UNIT |

|-----------------------|-----------------------------------|-----|-----|-----|------|

| t <sub>SPICPER</sub>  | SPI CLK Cycle Time                | 31  | 33  |     | ns   |

| t <sub>SPICHIGH</sub> | SPI CLK High Time                 | 10  |     |     | ns   |

| t <sub>SPICLOW</sub>  | SPI CLK Low Time                  | 10  |     |     | ns   |

| t <sub>SPIDOUT</sub>  | CLK Falling to DOUT               | 0   |     | 15  | ns   |

| t <sub>SSSETUP</sub>  | SPI SS_Z to CLK Rising Setup Time | 5   |     |     | ns   |

| t <sub>SSHOLD</sub>   | SPI CLK Rising to SS_Z Hold Time  | 5   |     |     | ns   |

| t <sub>DINSETUP</sub> | SPI DIN to CLK Rising Setup Time  | 5   |     |     | ns   |

| t <sub>DINHOLD</sub>  | SPI CLK Rising to DIN Hold Time   | 5   |     |     | ns   |

Figure 5-4. DLPC23x-Q1 Diagnostic Interface Timing

Figure 5-5. Chip Select Setup and Hold Timing

## 5.13 Timing Requirements—ADC Interface

|                          |                                  | MIN | NOM MAX | UNIT |

|--------------------------|----------------------------------|-----|---------|------|

| t <sub>ADCDINSETUP</sub> | ADC DIN to CLK Rising Setup Time | 5   |         | ns   |

| t <sub>ADCDINHOLD</sub>  | ADC CLK Rising to DIN Hold Time  | 5   |         | ns   |

| t <sub>ADCDOUT</sub>     | CLK Rising to DOUT               | 0   | 15      | ns   |

## 5.14 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER |                               | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-----------|-------------------------------|-----------------|------|-----|------|------|

| INTERNAL  | CLOCK                         |                 |      |     |      |      |

| fosc      | Internal Oscillator Frequency |                 | 1.76 | 2   | 2.24 | MHz  |

## **6 Detailed Description**

#### 6.1 Overview

The TPS99001-Q1 is an integral component of the DLP553x-Q1 and DLP462x-Q1 chipset, which also includes the DLPC23x-Q1 DMD display controller. The TPS99001-Q1 provides a high-voltage, high-precision, three-rail regulator to cost-effectively create DMD mirror control voltages (16V, 8.5V, -10V). A complete system power monitor and DMD mirror parking solution is included to increase system robustness and reduce cost. In addition, the TPS99001-Q1 includes numerous system monitoring and diagnostic features, such as configurable ADCs and watchdogs.

An integrated 12-bit ADC provides useful information about the operating condition of the system. Several external ADC channels are included for general usage (LED temperature measurement, and so on). One of the external ADC channels includes a differential input amplifier and is dedicated to LED current measurement. The DLPC23x-Q1 and TPS99001-Q1 ADC control blocks support up to 63 samples per video frame, with precise hardware alignment of samples to the DMD sequence timeline.

Two SPI buses are included. The first bus is intended for command and control, and the second is a read-only bus for optional redundant system condition monitoring. The SPI ports include support for byte-level parity checking.

Two windowed watchdog circuits are included to provide validation of DLPC23x-Q1 microprocessor operation and monitoring of DMD sequencer activity. The TPS99001-Q1 also includes on-die temperature threshold monitoring and a monitor circuit to validate the external clock ratio (of the SEQ\_CLK) against an internal oscillator.

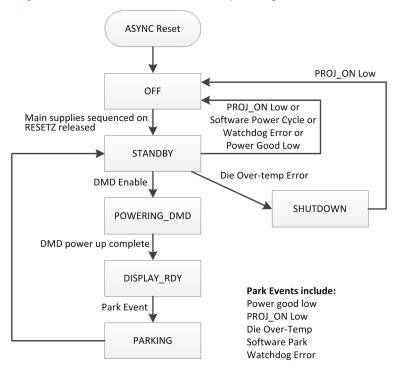

## 6.2 Functional Block Diagram

## **6.3 Feature Description**

### 6.3.1 Analog to Digital Converter

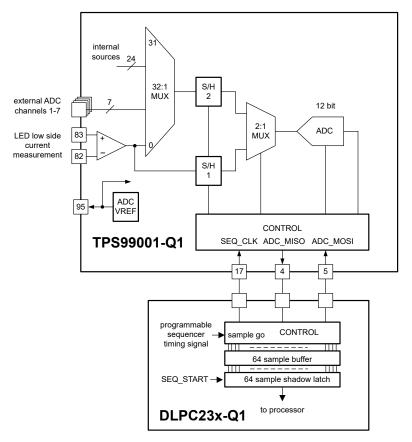

The TPS99001-Q1 includes a 12-bit analog to digital converter block with a 32:1 input mux and dual sample-and-hold circuits. It also includes a custom high speed serial control interface which when used in tandem with the DLPC23x-Q1 provides up to 63 DMD sequence-aligned samples per frame, with hardware-based sample timing and shadow-latched results. The hardware sample timing and shadow latch relieves the DLPC23x-Q1 processor from ADC timing tasks, freeing up processor resources for other uses.

Figure 6-1 illustrates the structure of the ADC controller blocks.

Figure 6-1. ADC Subsystem Block Diagram

The ADC block contains a dedicated channel reserved for differential low-side LED current measurements. Two sample-and-hold circuits are included to support paired LED current/voltage measurements. An additional seven external ADC channels are supported. The remaining 24 multiplexer inputs enable measurement of internal TPS99001-Q1 operating parameters.

## Note

When performing paired samples, they are sampled simultaneously, but converted sequentially, so the conversion time doubles.

The DLPC23x-Q1 contains a custom ADC control block that supports up to 63 ADC samples per frame. The samples are aligned with DMD sequencer activity, configurable through system configuration tools. This alignment makes measurement of specific light pulses (LED current and voltage) within a sequence possible, with precise repeatability from frame to frame. Up to 63 samples per frame are supported. The 63 sample buffer includes a shadow latch that updates each frame. This latched output is held constant for a complete frame time, allowing time for the DLPC23x-Q1 to collect and process the information.

A reference voltage output is also included in the ADC block. This provides a low current voltage reference which matches the reference used by the ADC for conversion. This external reference can be used to bias thermistor voltage dividers, providing greater accuracy than would be possible using a mix of external and internal references. Regardless of whether the reference voltage is used, a  $0.1\mu F$  capacitor should be connected from this pin to ground.

#### Note

Current supply is limited. Loads which exceed the specified current maximum rating on ADC\_VREF output may result in unpredictable ADC behavior.

Submit Document Feedback

#### 6.3.1.1 Analog to Digital Converter Input Table

Table 6-1. Analog to Digital Converter Input Table

|                    | Table 0-1. Arialog to Digital Converter input Table |                      |                    |         |         |         |      |  |  |  |

|--------------------|-----------------------------------------------------|----------------------|--------------------|---------|---------|---------|------|--|--|--|

| PAF                | RAMETER                                             | INTERNAL OR EXTERNAL | TEST CONDITIONS(1) | MIN     | TYP     | MAX     | UNIT |  |  |  |

| Channel 0, Gain    | Low side sense amp                                  | External             | Gain set to 24x    | 22.56   | 24      | 25.44   | V/V  |  |  |  |

| Channel 0, Gain    | Low side sense amp                                  | External             | Gain set to 12x    | 11.28   | 12      | 12.72   | V/V  |  |  |  |

| Channel 0, Gain    | Low side sense amp                                  | External             | Gain set to 9x     | 8.46    | 9       | 9.54    | V/V  |  |  |  |

| Channel 1, Gain    | ADC_IN1_PAD<br>(LED_ANODE)                          | External             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

| Channel 2, Gain    | ADC_IN2_PAD (VLED)                                  | External             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

| Channel 3, Gain    | ADC_IN3_PAD                                         | External             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

| Channel 4, Gain    | ADC_IN4_PAD                                         | External             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

| Channel 5, Gain    | ADC_IN5_PAD<br>(R_LED_THERM)                        | External             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

| Channel 6, Gain    | ADC_IN6_PAD<br>(G_LED_THERM)                        | External             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

| Channel 7, Gain    | ADC_IN7_PAD<br>(B_LED_THERM)                        | External             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

| Channel 8, Gain    | VBIAS                                               | Internal             |                    | 0.0596  | 0.0621  | 0.0646  | V/V  |  |  |  |

| Channel 9, Gain    | VOFFSET                                             | Internal             |                    | 0.1112  | 0.117   | 0.1218  | V/V  |  |  |  |

| Channel 10, Gain   | VRESET                                              | Internal             |                    | -0.1978 | -0.190  | -0.1822 | V/V  |  |  |  |

| Channel 10, Offset | VRESET                                              | Internal             |                    | -1.217  | -1.1935 | -1.169  | V    |  |  |  |

| Channel 11, Gain   | VMAIN                                               | Internal             |                    | 0.52546 | 0.559   | 0.59254 | V/V  |  |  |  |

| Channel 12, Gain   | DVDD                                                | Internal             |                    | 0.31302 | 0.333   | 0.35298 | V/V  |  |  |  |

| Channel 13, Gain   | V1.1                                                | Internal             |                    | 0.65706 | 0.699   | 0.74094 | V/V  |  |  |  |

| Channel 14, Gain   | V1.8                                                | Internal             |                    | 0.40326 | 0.429   | 0.45474 | V/V  |  |  |  |

| Channel 15, Gain   | V3.3                                                | Internal             |                    | 0.2209  | 0.235   | 0.2491  | V/V  |  |  |  |

| Channel 17, Gain   | ext ADC VREF                                        | Internal             |                    | 0.49    | 0.5     | 0.51    | V/V  |  |  |  |

| Channel 18, Gain   | Driver Power                                        | Internal             |                    | 0.20398 | 0.217   | 0.23002 | V/V  |  |  |  |

| Channel 19, Gain   | Die Temp1                                           | Internal             |                    | 0.490   | 0.500   | 0.510   | V/V  |  |  |  |

| Channel 20, Gain   | Die Temp2                                           | Internal             |                    | 0.490   | 0.500   | 0.510   | V/V  |  |  |  |

| Channel 28, Gain   | Channel not used                                    | Internal             |                    |         |         |         |      |  |  |  |

| Channel 29, Gain   | Main Bandgap, 0.5V                                  | Internal             |                    | 0.980   | 1.000   | 1.020   | V/V  |  |  |  |

|                    |                                                     |                      |                    |         |         |         |      |  |  |  |

<sup>(1)</sup> The conversionformula is (X + Offset) × Gain. X is the input voltage. Offset is 0V unless specified above.

### 6.3.2 Power Sequencing and Monitoring

The TPS99001-Q1 is specifically designed to perform correct power-up and power-down sequencing to ensure long term reliable operation of the DMD. The high voltage DMD mirror supplies require special power sequencing order, and restrictions on voltage differences between the power rails (VRESET, VBIAS, and VOFFSET) throughout power up, power down, and normal operation. The TPS99001-Q1 handles these requirements for the system designer.

#### 6.3.2.1 Power Monitoring

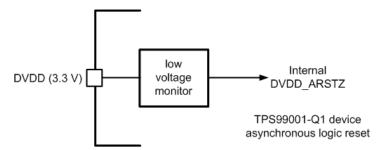

Main asynchronous digital logic reset (DVDD\_RSTZ) – Monitor of the main power of the 3.3V power supply input to the TPS99001-Q1. This monitor output is used as an asynchronous reset for all of the digital logic inside TPS99001-Q1.

Figure 6-2. Internal DVDD Monitor

The PROJ\_ON pin is the main on/off switch for the DLP subsystem. 1 is ON, 0 is OFF. Once DVDD\_ARSTZ is released, TPS99001-Q1 will begin sampling the PROJ\_ON pin. If it is low, the system stays in the OFF state. If it goes high, TPS99001-Q1 begins to progress through the power-on process.

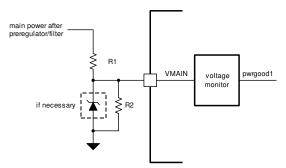

The TPS99001-Q1 includes a VMAIN *brown out* monitor function. A voltage monitor observes the voltage on the VMAIN input pin, as shown in Figure 6-3. The Zener may be necessary for overvoltage protection of the pin, in case the voltage being monitored has the potential to go high, such as a battery input.

Either PROJ\_ON or VMAIN may be used to turn the system on and off, and doing so will remove power to the DLPC23x-Q1. For fast control of turning the display on and off without removing power to the DLPC23x-Q1, change the operating mode of the DLPC23x-Q1 embedded software between 'Standby' and 'Display'.

Figure 6-3. VMAIN Brown Out Monitor

This monitor is used to provide the DLP subsystem with an early warning that power to the unit is going away. The system will park the DMD mirrors and proceed to a ready-for-power-off state if the VMAIN input voltage falls below a fixed threshold. External resistors should be used to divide the input power rail. Once a VMAIN brownout occurs, the main power rails to the TPS99001-Q1 must remain within their operating ranges until the TPS99001-Q1 power-down is complete.

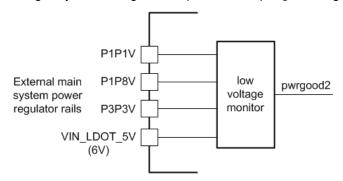

The main power rails to the chipset (6V, 3.3V, 1.8V, and 1.1V) are monitored with real-time power monitors as well. Each of these monitors is logically 'OR'ed together to produce the *pwrgood2* signal in Figure 6-4.

Figure 6-4. Real-Time Power Rail Monitors

Product Folder Links: TPS99001-Q1

Additionally, all power within the TPS99001-Q1 can be monitored by the ADC function. DLPC23x-Q1 software configures the ADC block to collect all voltage information in the system each frame. Any gross out of specification issues are captured and reported as system errors in the DLPC23x-Q1 system status.

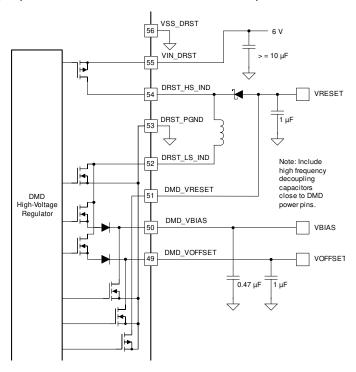

### 6.3.3 DMD Mirror Voltage Regulator

The DMD mirror voltage regulator generates three high-voltage supply rails: DMD\_VRESET, DMD\_VBIAS, and DMD\_VOFFSET. The DMD regulator uses a switching regulator where the inductor is time-shared between all three supplies. The inductor is charged up to a certain current level and then discharged into one of the three supplies. In cases where a supply does not need additional charge, the time slot normally allocated to that supply is skipped and the supplies requiring more charge receive all of the charging time.

For proper operation, specific bulk capacitance values are required for each supply rail. Refer to *Electrical Characteristics—Temperature and Voltage Monitors* for recommended values for the capacitors. The regulator contains active power down/discharge circuits. To meet timing requirements, total capacitance (actual capacitance, not the nominal) must not exceed these levels by substantial amounts, as defined in *Electrical Characteristics—Temperature and Voltage Monitors*. Power-down timing should be verified in each specific system design. Too low of a total capacitance will result in excessive ripple on the supply rails which may impact DMD mirror dynamic behavior. Care should be taken to use capacitors that maintain the recommended minimum capacitance over the expected operating device temperature range. Large-size packages are required here that do not lose so much capacitance at high voltages.

Although the average current drawn by the DMD on these supplies is small (10s of mA worst case), the peak currents can be several amps over 10s of nano-seconds. To supply this peak current, the use of small-value, high-frequency decoupling capacitors should be included as close as practical to the DMD power input pins.

Figure 6-5. DMD Voltage Regulator Circuit

#### 6.3.4 Low Dropout Regulators

The TPS99001-Q1 includes three low drop out regulators, dedicated to specific internal functions:

- A 5V output regulator for internal analog circuits (VIN LDOT 5V input, VLDOT 5V output)

- A 3.3V output regulator for internal analog (VIN LDOT 3P3V input, VLDOT 3P3V output)

- A 3.3V output regulator dedicated to the ADC block (VIN LDOA 3P3 input, VLDOA 3P3 output)

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

The positive output LDO regulators are all designed to operate from the same nominal 6V input as is needed by the DMD mirror voltage regulator, VIN\_DRST. However, care must be taken to isolate the sensitive analog circuit power supply inputs from switching noise, through dedicated sub-planes and supply filtering techniques.

### 6.3.5 System Monitoring Features

## 6.3.5.1 Windowed Watchdog Circuits

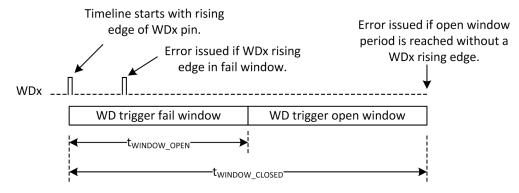

The TPS99001-Q1 contains two windowed watchdog circuits that can be used to detect malfunctions within the DLPC23x-Q1.

Figure 6-6. Windowed Watchdog Function

The DLPC23x-Q1 software uses both watchdog circuits. Watchdog #1 (WD1) monitors the internal microprocessor of the DLPC23x-Q1 through a wire connection to a dedicated GPIO line from DLPC23x-Q1. Watchdog #2 (WD2) is used to monitor the DLPC23x-Q1 sequencer operation (through monitoring of the SEQ STRT pin, wired to WD2 input).

When this function is enabled, two registers control the timing of the opening and closing of a watchdog trigger window. Process is initiated by a rising edge on the respective WDx pin. If another rising edge occurs before the WD trigger window opens, a watchdog error is issued. If the end of the open window period is reached without receiving a rising edge on WDx, an error is issued. The process restarts any time a WDx rising edge is received. The two watchdogs are independent.

#### 6.3.5.2 Die Temperature Monitors

The TPS99001-Q1 contains two on-chip die temperature monitors, for reduncy purposes, to monitor the internal temperature of the TPS99001-Q1. Each monitor has an output that indicates whether the die temperature has exceeded one of two thresholds. One monitors a warning threshold, and the other monitors an over-temperature error threshold. If the warning threshold is exceeded, a processor interrupt may be generated. If the over-temperature error threshold is exceeded during operation, the TPS99001-Q1 will initiate an emergency shutdown procedure and then wait for a toggle of the PROJ\_ON pin to initiate a system restart while operating in a low power state. The system does not proceed through the power-on initialization steps unless the on-die temperature is below the warning threshold. The status of these temperature monitor output bits is available over the SPI buses as long as DVDD and VDD. IO power supplies are up and stable.

### 6.3.5.3 External Clock Ratio Monitor

The TPS99001-Q1 operates from two primary clock sources: an internal low frequency oscillator (2 MHz, used for system initialization and other maintenance purposes), and an external high speed (30 MHz) clock, SEQ\_CLK, used for most timing critical applications, such as the ADC. The TPS99001-Q1 includes a function that reports the ratio of this internal vs. external clock. This ratio is available over the SPI bus. The DLPC23x-Q1 can check this ratio and compare to expected value. If the ratio is incorrect, there is a possibility the DLPC23x-Q1 oscillator may have locked to an incorrect harmonic, or some other fault condition has occurred.

Product Folder Links: TPS99001-Q1

#### 6.3.6 Communication Ports

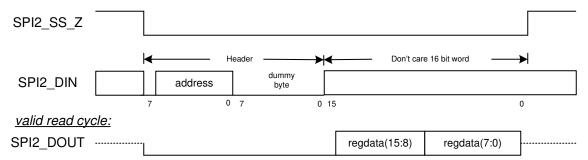

#### 6.3.6.1 Serial Peripheral Interface (SPI)

The TPS99001-Q1 provides two four-wire SPI ports that support transfers up to 30MHz clock rates. The primary port (SPI1) supports register reads and writes, and serves as the primary set up and control interface for the device. The DLPC23x-Q1 is the primary of SPI1 to control the TPS99001-Q1 during system operation. A secondary read-only four wire SPI port (SPI2) is available to provide status information to an optional second microcontroller in the system.