**TPS65631** SLVSBK1E - SEPTEMBER 2012 - REVISED MAY 2014

# **TPS65631 Dual-Output AMOLED Display Power Supply**

#### **Features**

- 2.9-V to 4.5-V Input Voltage Range

- Fixed 4.6-V Positive Output Voltage

- 0.5% V<sub>POS</sub> Accuracy from 25°C to 85°C

- Separate V<sub>POS</sub> Output Sense Pin

- Negative Output Voltage Digitally Programmable from -1.4 V to -4.4 V (-4 V Default)

- Output Currents up to 250 mA Supported

- **Excellent Line Transient Regulation**

- **Short-Circuit Protection**

- Thermal Shutdown

- Available in 3.00-mm × 3.00-mm, 12-Pin QFN Package

### 2 Applications

**AMOLED Displays**

### 3 Description

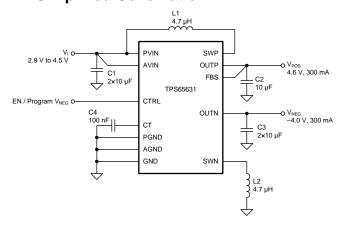

The TPS65631 is designed to drive AMOLED (Active Matrix Organic Light Emitting Diode) displays requiring positive and negative supply rails. The device integrates a boost converter for V<sub>POS</sub> and an inverting buck boost converter for V<sub>NEG</sub> and is suitable for battery-operated products. The digital control pin (CTRL) allows programming the negative output voltage in digital steps. The TPS65631 uses a novel technology enabling excellent line transient performance.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |  |

|-------------|----------|-------------------|--|

| TPS65631    | QFN (12) | 3.00 mm × 3.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet

# Simplified Schematic

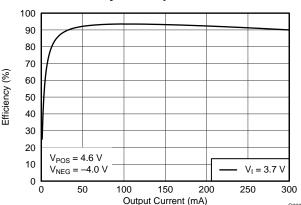

### **Efficiency vs Output Current**

# **Table of Contents**

| 1 | Features 1                           | 8.2 Functional Block Diagram                        | . 8 |

|---|--------------------------------------|-----------------------------------------------------|-----|

| 2 | Applications 1                       | 8.3 Feature Description                             | . 8 |

| 3 | Description 1                        | 8.4 Device Functional Modes                         | 12  |

| 4 | Simplified Schematic 1               | 9 Applications and Implementation                   | 12  |

| 5 | Revision History2                    | 9.1 Application Information                         | 12  |

| 6 | Pin Configuration and Functions      | 9.2 Typical Application                             | 12  |

| 7 | Specifications4                      | 10 Power Supply Recommendations                     | 16  |

| • | 7.1 Absolute Maximum Ratings         | 11 Layout 1                                         | 17  |

|   | 7.2 Handling Ratings                 | 11.1 Layout Guidelines                              | 17  |

|   | 7.3 Recommended Operating Conditions | 11.2 Layout Example                                 | 17  |

|   | 7.4 Thermal Information              | 12 Device and Documentation Support 1               | 18  |

|   | 7.5 Electrical Characteristics 5     | 12.1 Device Support                                 | 18  |

|   | 7.6 Timing Requirements 6            | 12.2 Trademarks                                     | 18  |

|   | 7.7 Typical Characteristics          | 12.3 Electrostatic Discharge Caution                | 18  |

| 8 | Detailed Description 8               | 12.4 Glossary                                       | 18  |

| • | 8.1 Overview                         | 13 Mechanical, Packaging, and Orderable Information | 18  |

# 5 Revision History

| DATE REVISION |  | NOTES                                                  |  |  |

|---------------|--|--------------------------------------------------------|--|--|

| May 2014 E    |  | No legacy rev history for rev E – first public release |  |  |

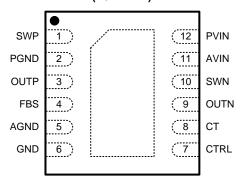

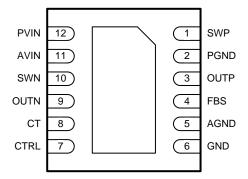

# 6 Pin Configuration and Functions

### DPD PACKAGE (TOP VIEW)

# DPD PACKAGE (BOTTOM VIEW)

### **Pin Functions**

| NAME                   | NO. | I/O | DESCRIPTION                                                                                                                                                                                                    |  |

|------------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AGND                   | 5   | _   | Analog ground.                                                                                                                                                                                                 |  |

| AVIN                   | 11  | _   | Input supply voltage for internal analog circuits (both converters).                                                                                                                                           |  |

| СТ                     | 8   | I/O | Timing capacitor pin. Connect a capacitor between this pin and ground to control the time it takes for the output of the inverting buck-boost converter to ramp from one value of $V_{\text{NEG}}$ to another. |  |

| CTRL                   | 7   | I   | Control pin. Combined device enable and inverting buck-boost converter output voltage programming pin.                                                                                                         |  |

| FBS                    | 4   | I   | Feedback sense pin of the boost converter output voltage.                                                                                                                                                      |  |

| GND                    | 6   | _   | Ground. (Note: it is possible to leave this pin floating without affecting device performance.)                                                                                                                |  |

| PGND                   | 2   | _   | Power ground of the boost converter.                                                                                                                                                                           |  |

| PVIN                   | 12  | _   | Input supply voltage pin for the inverting buck-boost converter.                                                                                                                                               |  |

| SWN                    | 10  | 0   | Switch pin of the inverting buck-boost converter.                                                                                                                                                              |  |

| SWP                    | 1   | 0   | Switch pin of the boost converter.                                                                                                                                                                             |  |

| OUTN                   | 9   | 0   | Rectifier pin of the inverting buck-boost converter.                                                                                                                                                           |  |

| OUTP                   | 3   | 0   | Rectifier pin of the boost converter.                                                                                                                                                                          |  |

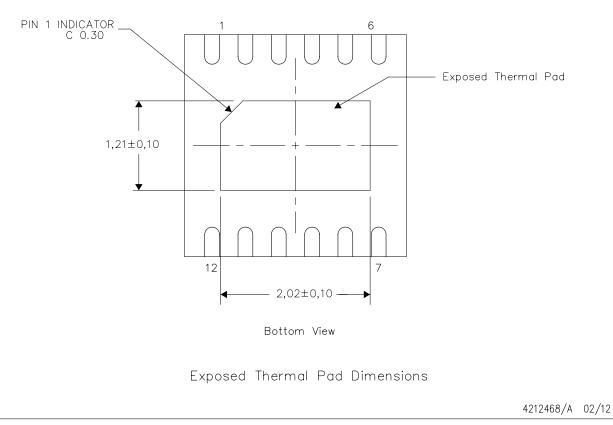

| Exposed Thermal<br>Pad | 13  | _   | Connect this pad to AGND and PGND.                                                                                                                                                                             |  |

## 7 Specifications

# 7.1 Absolute Maximum Ratings (1)

over operating free-air temperature range (unless otherwise noted) (1)

|                                                      |                            | MIN  | MAX | UNIT |

|------------------------------------------------------|----------------------------|------|-----|------|

| Input voltage (2)                                    | SWP, OUTP, FBS, PVIN, AVIN | -0.3 | 6   | V    |

|                                                      | OUTN                       | -0.3 | -6  | V    |

|                                                      | SWN                        | -6   | 6   | V    |

|                                                      | CTRL                       | -0.3 | 5.5 | V    |

|                                                      | СТ                         | -0.3 | 3.6 | V    |

| Operating junction temperature range, T <sub>J</sub> |                            | -40  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) With respect to GND pin.

### 7.2 Handling Ratings

|                  |                         |                                                                               | MIN  | MAX | UNIT |

|------------------|-------------------------|-------------------------------------------------------------------------------|------|-----|------|

| T <sub>STG</sub> | Storage temperature rar | nge                                                                           | -65  | 150 | °C   |

|                  |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | -2   | 2   | kV   |

| V <sub>ESD</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -500 | 500 | V    |

|                  |                         | Machine model (MM) ESD stress voltage                                         | -200 | 200 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                | PARAMETER                      |                  | MIN  | NOM | MAX  | UNIT |

|----------------|--------------------------------|------------------|------|-----|------|------|

| $V_{I}$        | Input supply voltage range     |                  | 2.9  | 3.7 | 4.5  | V    |

| \/             | Output voltage range           | V <sub>POS</sub> |      | 4.6 |      | V    |

| Vo             |                                | $V_{NEG}$        | -4.4 | -4  | -1.4 |      |

|                | Output surrent reason          | I <sub>POS</sub> |      |     | 300  |      |

| IO             | Output current range           | I <sub>NEG</sub> |      |     | 300  | mA   |

| T <sub>A</sub> | Operating ambient temperature  |                  | -40  | 25  | 85   | °C   |

| $T_{J}$        | Operating junction temperature |                  | -40  | 85  | 125  | °C   |

### 7.4 Thermal Information

|                    | THERMAL METRIC <sup>(1)</sup>                | PD      | LINUT |

|--------------------|----------------------------------------------|---------|-------|

|                    | I HERMAL METRIC**                            | 12 PINS | UNIT  |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 51.5    |       |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 47.1    |       |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 25.0    | °C/W  |

| $\Psi_{JT}$        | Junction-to-top characterization parameter   | 0.5     | *C/VV |

| ΨЈВ                | Junction-to-board characterization parameter | 25.2    |       |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | 4.4     |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process..

### 7.5 Electrical Characteristics

$V_I = 3.7 \text{ V}, V_{(CTRL)} = 3.7 \text{ V}, V_{POS} = 4.6 \text{ V}, V_{NEG} = -4.0 \text{ V}, T_J = -40^{\circ}\text{C}$  to 125°C, typical values are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|                     | PARAMETER                                        | TEST CONDITIONS                                     | MIN   | TYP   | MAX  | UNIT  |

|---------------------|--------------------------------------------------|-----------------------------------------------------|-------|-------|------|-------|

| SUPPLY              |                                                  |                                                     |       |       |      |       |

| l <sub>l</sub>      | Shutdown current into AVIN and PVIN              | CTRL pin connected to ground.                       |       | 0.1   |      | μΑ    |

| V <sub>UVLO</sub>   | Undervoltage lockout threshold                   | V <sub>I</sub> rising.                              |       |       | 2.4  | V     |

| · UVLO              | onacronago iconour un concia                     | V <sub>I</sub> falling.                             |       |       | 2.1  | ·     |

| BOOST               | CONVERTER                                        |                                                     |       |       |      |       |

|                     | Output voltage                                   |                                                     |       | 4.6   |      | V     |

| $V_{O}$             | Output voltage tolerance                         | 25°C ≤ T <sub>A</sub> ≤ 85°C, no load               | -0.5% |       | 0.5% |       |

|                     | Output voltage tolerance                         | -40°C ≤ T <sub>A</sub> < 85°C, no load              | -0.8% |       | 0.8% |       |

| _                   | Switch (low-side) on-resistance                  | I <sub>(SWP)</sub> = 200 mA                         |       | 200   |      | mΩ    |

| r <sub>DS(ON)</sub> | Rectifier (high-side) on-resistance              | I <sub>(SWP)</sub> = 200 mA                         |       | 350   |      | 11122 |

|                     | Switching frequency                              | I <sub>O</sub> = 200 mA                             |       | 1.7   |      | MHz   |

|                     | Switch current limit                             | Inductor valley current                             | 0.8   | 1     |      | Α     |

|                     | Short-circuit threshold voltage in operation     | V <sub>O</sub> falling                              |       | 4.1   |      | V     |

|                     | Short-circuit detection time during operation    |                                                     |       | 3     |      | ms    |

|                     | Output sense threshold voltage using OUTP        | V <sub>(OUTP)</sub> - V <sub>(FBS)</sub> increasing |       | 300   |      | mV    |

|                     | Output sense threshold voltage using FBS         | V <sub>(OUTP)</sub> - V <sub>(FBS)</sub> decreasing |       | 200   |      | mV    |

|                     | Input resistance of FBS                          | Between FBS pin and ground                          |       | 4     |      | МΩ    |

|                     | Discharge resistance                             | CTRL pin connected to ground, I <sub>O</sub> = 1 mA |       | 30    |      | Ω     |

|                     | Line regulation                                  | I <sub>O</sub> = 200 mA                             |       | 0.002 |      | %/V   |

|                     | Load regulation                                  |                                                     |       | 0.01  |      | %/A   |

| INVERTI             | NG BUCK-BOOST CONVERTER                          |                                                     | •     |       |      |       |

|                     | Output voltage default                           |                                                     |       | -4.0  |      |       |

| $V_{O}$             | Output voltage range                             |                                                     | -4.4  |       | -1.4 | V     |

|                     | Output voltage tolerance                         |                                                     | -0.05 |       | 0.05 |       |

|                     | Switch (high-side) on-resistance                 | I <sub>(SWN)</sub> = 200 mA                         |       | 200   |      |       |

| r <sub>DS(ON)</sub> | Rectifier (low-side) on-resistance               | I <sub>(SWN)</sub> = 200 mA                         |       | 300   |      | mΩ    |

|                     | Switching frequency                              | $I_O = 10 \text{ mA}$                               |       | 1.7   |      | MHz   |

|                     | Switch current limit                             | V <sub>I</sub> = 2.9 V                              | 1.5   | 2.2   |      | Α     |

|                     | Short-circuit threshold voltage during operation | Voltage drop from nominal V <sub>O</sub>            |       | 500   |      |       |

|                     | Short-circuit threshold voltage during start-up  |                                                     | 180   | 200   | 230  | mV    |

| t <sub>SCP</sub>    | Short-circuit detection time during start-up     |                                                     |       | 10    |      | ms    |

|                     | Short-circuit detection time during operation    |                                                     |       | 3     |      | ms    |

|                     | Discharge resistance                             | CTRL pin connected to ground, $I_O = 1 \text{ mA}$  |       | 150   |      | Ω     |

|                     | Line regulation                                  | I <sub>O</sub> = 200 mA                             |       | 0.006 |      | %/V   |

|                     | Load regulation                                  |                                                     |       | 0.31  |      | %/A   |

| CTRL                |                                                  |                                                     |       |       |      |       |

|                     | High-level threshold voltage                     |                                                     |       |       | 1.2  | V     |

|                     | Low-level threshold voltage                      |                                                     | 0.4   |       |      | V     |

Copyright © 2012–2014, Texas Instruments Incorporated

Submit Documentation Feedback

# **Electrical Characteristics (continued)**

$V_I = 3.7$  V,  $V_{(CTRL)} = 3.7$  V,  $V_{POS} = 4.6$  V,  $V_{NEG} = -4.0$  V,  $T_J = -40^{\circ}$ C to 125°C, typical values are at  $T_A = 25^{\circ}$ C (unless otherwise noted)

|                    | PARAMETER                    | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |

|--------------------|------------------------------|-----------------|-----|-----|-----|------|--|

|                    | Pull-down resistance         |                 | 150 | 400 | 860 | kΩ   |  |

| OTHER              | OTHER                        |                 |     |     |     |      |  |

| R <sub>(CT)</sub>  | CT pin output resistance     |                 | 150 | 300 | 500 | kΩ   |  |

| t <sub>INIT</sub>  | Initialization time          |                 |     | 300 | 400 | μs   |  |

| t <sub>OFF</sub>   | Shut-down time               |                 | 30  |     | 80  | μs   |  |

| t <sub>STORE</sub> | Data storage time            |                 | 30  |     | 80  | μs   |  |

| T <sub>SD</sub>    | Thermal shutdown temperature |                 |     | 145 |     | °C   |  |

# 7.6 Timing Requirements

|                   |                           | MIN | TYP | MAX | UNIT |

|-------------------|---------------------------|-----|-----|-----|------|

| CTRL Int          | terface                   |     |     |     |      |

| t <sub>HIGH</sub> | High-level pulse duration | 2   | 10  | 25  | μs   |

| $t_{LOW}$         | Low-level pulse duration  | 2   | 10  | 25  | μs   |

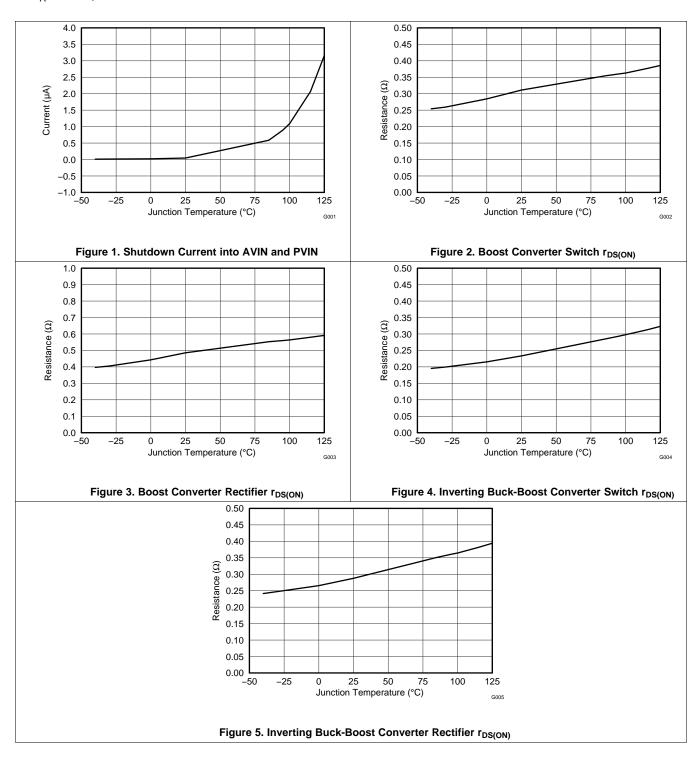

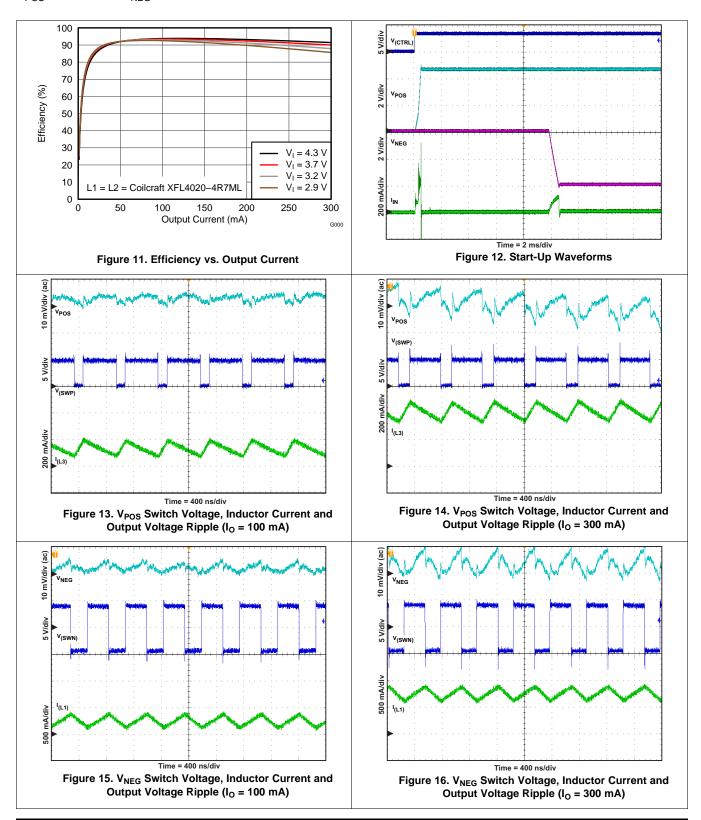

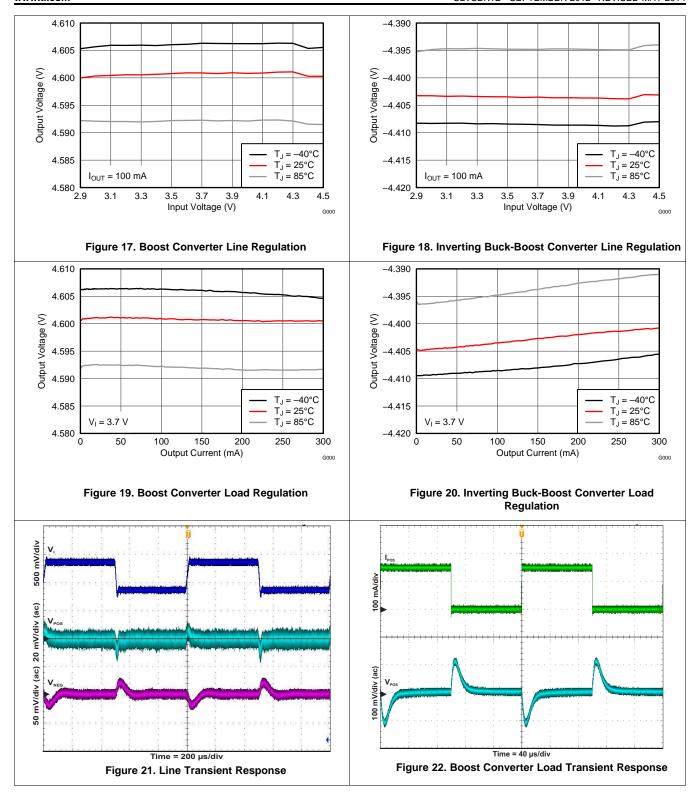

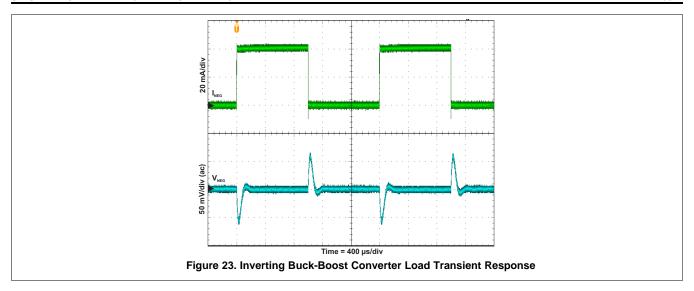

### 7.7 Typical Characteristics

At  $T_A = 25$ °C, unless otherwise noted.

### 8 Detailed Description

#### 8.1 Overview

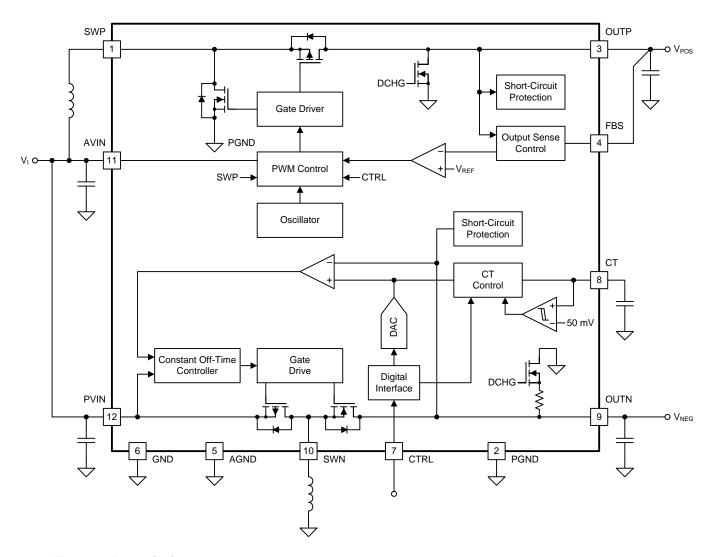

The TPS65631 consists of a boost converter and an inverting buck boost converter. The  $V_{POS}$  output is fixed at 4.6 V and  $V_{NEG}$  output is programmable via a digital interface in the range of -1.4 V  $\sim$  -4.4 V, the default is -4 V. The transition time of  $V_{NEG}$  output is adjustable by the CT pin capacitor.

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Boost Converter

The boost converter uses a fixed-frequency current-mode topology, and its output voltage (V<sub>POS</sub>) is fixed at 4.6 V

For the highest output voltage accuracy, connect the output sense pin (FBS) directly to the positive pin of the output capacitor. If not used, the FBS pin can be left floating or connected to ground. If the FBS pin is not used, the boost converter senses its output voltage using the OUTP pin.

### **Feature Description (continued)**

### 8.3.2 Inverting Buck-Boost Converter

The inverting buck-boost converter uses a constant-off-time peak-current mode topology. The converter's default output voltage ( $V_{NEG}$ ) is -4 V, but it can be programmed to any voltage in the range -1.4 V to -4.4 V (see *Programming*  $V_{NEG}$ ).

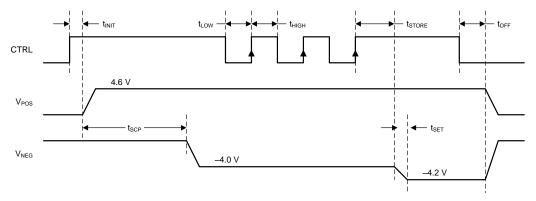

### 8.3.2.1 Programming $V_{NEG}$

The output voltage of the inverting buck-boost converter ( $V_{NEG}$ ) can be programmed using the CTRL pin. If output voltage programming is not required, the CTRL pin can be used as a standard enable pin (see *Enable (CTRL)*).

Figure 6. Programming V<sub>NEG</sub> Using the CTRL Pin

When the CTRL pin is pulled high, the inverting buck-boost converter starts up with its default voltage of -4V. The device now counts the rising edges applied to the CTRL pin and sets the output voltage ( $V_{NEG}$ ) according to Table 1. For the timing diagram shown in Figure 6,  $V_{NEG}$  is programmed to -4.2 V, since three rising edges are detected.

The CTRL interface is designed to work with pulses whose duration is between 2  $\mu$ s and 25  $\mu$ s. Pulses shorter than 2  $\mu$ s or longer than 25  $\mu$ s are not ensured to be recognized.

| Number of Rising Edges | V <sub>NEG</sub> | Number of Rising Edges | V <sub>NEG</sub> |

|------------------------|------------------|------------------------|------------------|

| 0 / no pulses          | -4 V             | 16                     |                  |

|                        |                  |                        |                  |

| 1                      | –4.4 V           | 17                     | –2.8 V           |

| 2                      | –4.3 V           | 18                     | –2.7 V           |

| 3                      | –4.2 V           | 19                     | –2.6 V           |

| 4                      | -4.1 V           | 20                     | –2.5 V           |

| 5                      | -4.0 V           | 21                     | –2.4 V           |

| 6                      | -3.9 V           | 22                     | –2.3 V           |

| 7                      | −3.8 V           | 23                     | –2.2 V           |

| 8                      | −3.7 V           | 24                     | –2.1 V           |

| 9                      | -3.6 V           | 25                     | –2.0 V           |

| 10                     | −3.5 V           | 26                     | -1.9 V           |

| 11                     | −3.4 V           | 27                     | -1.8 V           |

| 12                     | −3.3 V           | 28                     | –1.7 V           |

| 13                     | -3.2 V           | 29                     | -1.6 V           |

| 14                     | -3.1 V           | 30                     | –1.5 V           |

| 15                     | −3.0 V           | 31                     | -1.4 V           |

**Table 1. Programming Table for V<sub>NEG</sub>**

Copyright © 2012–2014, Texas Instruments Incorporated

Submit Docume

Product Folder Links: TPS65631

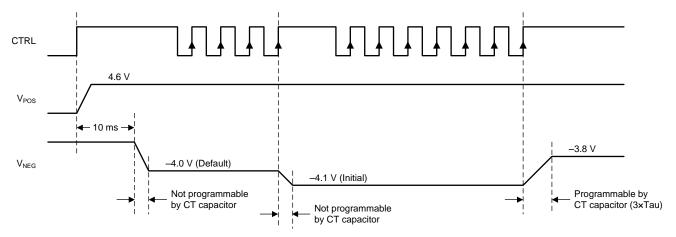

### 8.3.2.2 Controlling the V<sub>NEG</sub> Transition Time

The transition time ( $t_{set}$ ) is the time required to move  $V_{NEG}$  from one voltage level to the next. Users can control the transition time by connecting a capacitor between the CT pin and ground. When the CT pin is left open or is connected to ground, the transition time is as short as possible. When a capacitor is connected to the CT pin, the transition time is determined by the time constant ( $\tau$ ) of the external capacitor ( $C_{(CT)}$ ) and the internal resistance of the CT pin ( $R_{(CT)}$ ). The output voltage  $V_{NEG}$  reaches 70% of its programmed value after 1 $\tau$ .

An example is given below for the case when using 100 nF for C<sub>(CT)</sub>.

$$\tau \approx t_{set(70\%)} = R_{(CT)} \times C_{(CT)} = 300 \text{ k}\Omega \times 100 \text{ nF} = 30 \text{ ms}$$

(1)

The output voltage V<sub>NEG</sub> reaches its programmed value after approximately 3T.

The external capacitor connected to the CT pin has no effect on the first programming of  $V_{NEG}$ , when the inverting buck-boost converter ramps its output to the default voltage as fast as possible. Figure 7 shows the detail of programming of the  $V_{NEG}$  transition time with the CT pin during start-up.

Figure 7. Programming the Transition Time of V<sub>NEG</sub>

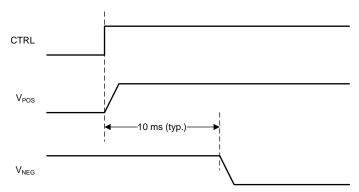

#### 8.3.3 Soft-Start and Start-Up Sequence

The TPS65631 features a soft-start function to limit inrush current. When the device is enabled by a high-level signal applied to the CTRL pin, the boost converter starts switching with a reduced switch current limit. Ten milliseconds after the CTRL pin goes high, the inverting buck-boost converter starts with a default value of –4 V. A typical start-up sequence is shown in Figure 8.

Figure 8. Typical Start-Up Sequence

#### 8.3.4 Enable (CTRL)

The CTRL pin serves two functions. One is to enable and disable the device, and the other is to program the output voltage ( $V_{NEG}$ ) of the inverting buck-boost converter (see *Programming V\_{NEG}*). If the digital interface is not required, the CTRL pin can be used as a standard enable pin for the device, which will come up with its default value on  $V_{NEG}$  of -4 V. When CTRL is pulled high, the device is enabled. The device is shut down with CTRL low.

#### 8.3.5 Undervoltage Lockout

The TPS65631 features an undervoltage lockout function that disables the device when the input supply voltage is too low for normal operation.

#### 8.3.6 Short Circuit Protection

The TPS65631 is protected against short-circuits of  $V_{POS}$  and  $V_{NEG}$  to ground and to each other.

#### 8.3.6.1 Short-Circuits During Normal Operation

During normal operation an error condition is detected if  $V_{POS}$  falls below 4.1 V for more than 3 ms or  $V_{NEG}$  is pulled above the programmed nominal output by 500 mV for longer than 3 ms. In either case the device enters shutdown mode: the converters are disabled and their outputs are disconnected from the input. To resume normal operation either cycle the input supply voltage or toggle the CTRL pin low and then high again.

#### 8.3.6.2 Short-Circuits During Start-Up

During start up an error condition is detected if:

- V<sub>POS</sub> is not in regulation 10 ms after a high-level is applied to the CTRL pin.

- V<sub>NEG</sub> is higher than threshold level 10 ms after a high-level is applied to the CTRL pin.

- V<sub>NEG</sub> is not in regulation 20 ms after a high-level is applied to the CTRL pin.

To resume normal operation either cycle the input supply voltage or toggle the CTRL pin low and then high again.

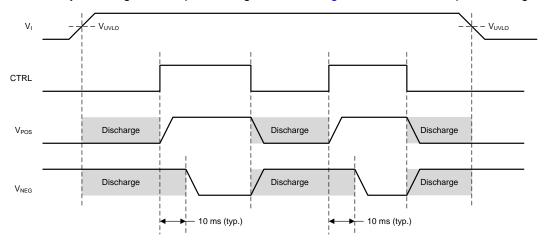

#### 8.3.7 Output Discharge During Shutdown

The TPS65631 actively discharges its outputs during shutdown. Figure 9 shows the output discharge control.

Figure 9. Active Discharge of V<sub>POS</sub> and V<sub>NEG</sub> During Shutdown

#### 8.3.8 Thermal Shutdown

The TPS65631 enters thermal shutdown mode if its junction temperature exceeds 145°C (typical). During thermal shutdown mode none of the device functions are available. To resume normal operation, either cycle the input supply voltage or toggle the CTRL pin low and then high again.

#### 8.4 Device Functional Modes

#### 8.4.1 Operation with $V_1 < 2.9 \text{ V}$

The recommended minimum input supply voltage for full performance is 2.9 V. The device continues to operate with input supply voltages below 2.9 V; however, full performance is not guaranteed. The device does not operate with input supply voltages below the UVLO threshold.

#### 8.4.2 Operation with $V_1 \approx V_{POS}$ (Diode Mode)

The TPS65631 features a "diode" mode that enables it to regulate its output voltage even when the input supply voltage is close to  $V_{POS}$  (that is, too high for normal boost operation). When operating in diode mode the converter's high-side switch stops switching and its body diode is used as the rectifier. Boost converter efficiency is reduced when operating in diode mode. At low output currents ( $\approx$ 2 mA and below), the boost converter automatically transitions from pulse-width modulation to pulse-skip mode. This ensures that  $V_{POS}$  stays in regulation but increases the output voltage ripple on  $V_{POS}$ .

#### 8.4.3 Operation with CTRL

When a low-level signal is applied to the CTRL pin the device is disabled and switching is inhibited. When the input supply voltage is above the UVLO threshold and a high-level signal is applied to the CTRL pin the device is enabled and its start-up sequence begins.

### 9 Applications and Implementation

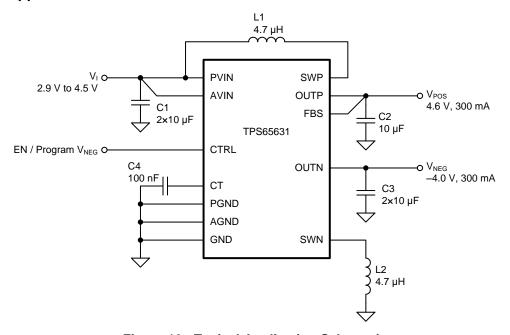

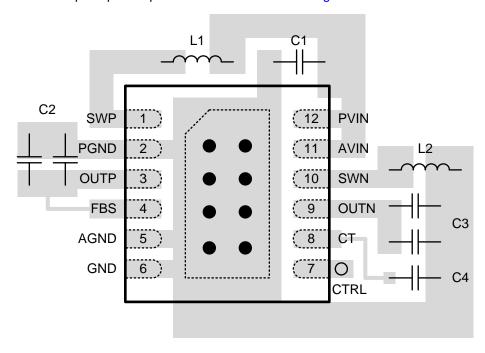

#### 9.1 Application Information

Figure 10 shows a typical application circuit suitable for supplying AMOLED displays in smartphone applications. The circuit is designed to operate from a single-cell Li-Ion battery and generates a positive output voltage  $V_{POS}$  of 4.6 V and a negative output voltage of -4 V. Both outputs are capable of supplying up to 300 mA of output current.

### 9.2 Typical Application

Figure 10. Typical Application Schematic

### **Typical Application (continued)**

### 9.2.1 Design Requirements

For this design example, use the following input parameters.

**Table 2. Design Parameters**

| DESIGN PARAMETER    | EXAMPLE                          |

|---------------------|----------------------------------|

| Input voltage range | 2.9 V to 4.5 V                   |

| Output voltage      | $V_{POS} = 4.6V, V_{NEG} = -4 V$ |

| Switching frequency | 1.7 MHz                          |

### 9.2.2 Detailed Design Procedure

In order to maximize performance, the TPS65631 has been optimized for use with a relatively narrow range of component values, and customers are strongly recommended to use the application circuit shown in Figure 10 with the components listed in Table 3 and Table 4.

#### 9.2.2.1 Inductor Selection

The boost converter and inverting buck-boost converter have been optimized for use with 4.7  $\mu$ H inductors, and it is recommended that this value be used in all applications. Customers using other values of inductor are strongly recommended to characterize circuit performance on a case-by-case basis.

**Table 3. Inductor Selection**

| PARAMETER | VALUE  | MANUFACTURER       | PART NUMBER     |  |  |  |

|-----------|--------|--------------------|-----------------|--|--|--|

|           |        | Coilmaster         | MMPP252012-4R7N |  |  |  |

| L1, L2    | 4.7    | Toko 1239AS-H-4R7M |                 |  |  |  |

|           | 4.7 μH | ABCO               | LPP252012-4R7N  |  |  |  |

|           |        | Coilcraft          | XFL4020-4R7ML   |  |  |  |

#### 9.2.2.2 Capacitor Selection

The recommended capacitor values are shown in Table 4. Applications using less than the recommended capacitance (e.g. to save PCB area) may experience increased voltage ripple. In general, the lower the output power, the lower the necessary capacitance.

**Table 4. Capacitor Selection**

| PARAMETER | VALUE     | MANUFACTURER | PART NUMBER       |

|-----------|-----------|--------------|-------------------|

| C1        | 2 × 10 μF | Murata       | GRM21BR71A106KE51 |

| C2        | 10 μF     | Murata       | GRM21BR71A106KE51 |

| C3        | 2 × 10 μF | Murata       | GRM21BR71A106KE51 |

| C4        | 100 nF    | Murata       | GRM21BR71E104KA01 |

#### 9.2.2.3 Stability

Applications using component values that differ significantly from those recommended in Table 3 and Table 4 should be checked for stability over the full range of operating conditions.

#### 9.2.3 Application Curves

The performance shown in the following graphs was obtained using the circuit shown in Figure 10 and the external components shown in Table 3 and Table 4. The output voltage settings for these measurements were  $V_{POS} = 4.6 \text{ V}$  and  $V_{NFG} = -4 \text{ V}$ .

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

Copyright © 2012–2014, Texas Instruments Incorporated

Submit Documentation Feedback

# 10 Power Supply Recommendations

The TPS65631 is designed to operate from an input voltage supply range between 2.9 V and 4.5 V. If the input supply is located more than a few centimeters from the TPS65631 additional bulk capacitance may be required. The  $2\times10~\mu\text{F}$  shown in the schematics in this data sheet are a typical choice for this function.

Submit Documentation Feedback

### 11 Layout

### 11.1 Layout Guidelines

No PCB layout is perfect, and compromises are always necessary. However, following the basic principles listed below (in order of importance) should go a long way to achieving good performance:

- Route switching currents on the top layer using short, wide traces. Do not route these signals through vias, which have relatively high parasitic inductance and resistance.

- Place C1 as close as possible to pin 12.

- Place C2 as close as possible to pin 3.

- Place C3 as close as possible to pin 9.

- Place L1 as close as possible to pin 1.

- Place L2 as close as possible to pin 10.

- Use the thermal pad to join GND, AGND and PGND.

- Connect the FBS pin directly to the positive pin of C2, that is, keep this connection separate from the connection between OUTP and C2.

- Use a copper pour on layer 2 as a thermal spreader and connect the thermal pad to it using a number of thermal vias.

Figure 24 illustrates how a PCB layout following the above principles may be realized in practice.

### 11.2 Layout Example

Figure 24 shows the above principles implemented for the circuit of Figure 10.

- O Via to signal layer on internal or bottom layer.

- Thermal via to copper pour on internal or bottom layer.

Figure 24. PCB Layout Example

### 12 Device and Documentation Support

### 12.1 Device Support

#### 12.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 12.2 Trademarks

All trademarks are the property of their respective owners.

#### 12.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 12.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms and definitions.

### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com

31-Oct-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TPS65631DPDR          | Active | Production    | WSON (DPD)   12 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | SDS              |

| TPS65631DPDR.A        | Active | Production    | WSON (DPD)   12 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | SDS              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No. RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

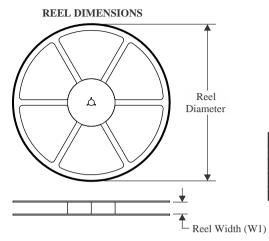

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 20-Apr-2023

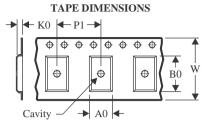

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

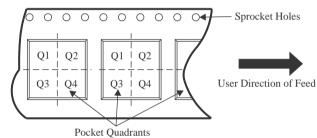

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS65631DPDR | WSON            | DPD                | 12 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

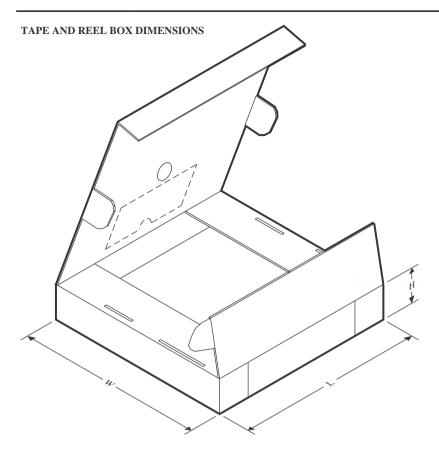

**PACKAGE MATERIALS INFORMATION**

www.ti.com 20-Apr-2023

### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS65631DPDR | WSON         | DPD             | 12   | 3000 | 346.0       | 346.0      | 33.0        |

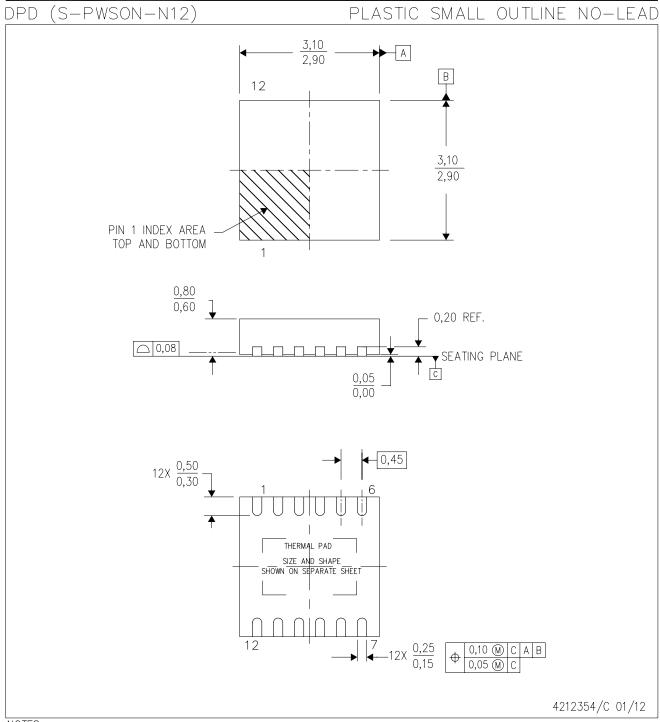

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Small Outline No-Lead (SON) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance, if present.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions, if present

# DPD (S-PUSON-N12)

PLASTIC SMALL OUTLINE NO-LEAD

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025