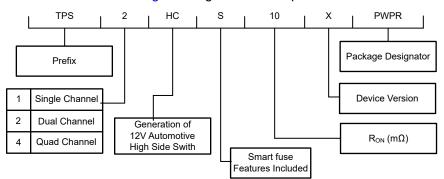

# TPS2HCS08-Q1 8.9mΩ, Automotive Dual-Channel, SPI Controlled High-Side Switch With Integrated I2T Wire Protection and Low Power Mode

#### 1 Features

- AEC-Q100 qualified for automotive applications

- Temperature grade 1: –40°C to 125°C

- Device HBM ESD classification level 2

- Device CDM ESD classification level C5

- Withstands 36V load dump

- Dual-channel SPI controlled smart high-side switch with integrated nFETs.

- Integrated wire-harness protection without MCU involvement and a SPI programmable fuse curve

- Protection against persistent overload condition

- Improve system level reliability through SPI programmable adjustable overcurrent protection

- SPI configurable capacitive charging mode to drive a wide range of capacitive input ECUs load current needs.

- Low guiescent current, low power ON-state to supply always-ON loads with automatic wake on load current increase with wake signal to MCU

- Robust integrated output protection:

- Integrated thermal protection

- Protection against short-to-ground

- Protection against reverse battery events including automatic switch on of FET with reverse supply voltage

- Automatic shut off on loss of battery and around

- Integrated output clamp to demagnetize inductive loads

- Digital sense output via SPI can be configured to measure:

- Load current accurately with integrated ADC

- Output or supply voltage, FET temperature

- Provides full fault diagnostics through SPI interface and indication through FLT pin

- Detection of open load and short-to-battery

## 2 Applications

- Automotive zone ECU

- Power distribution modules

- Body control modules

### 3 Description

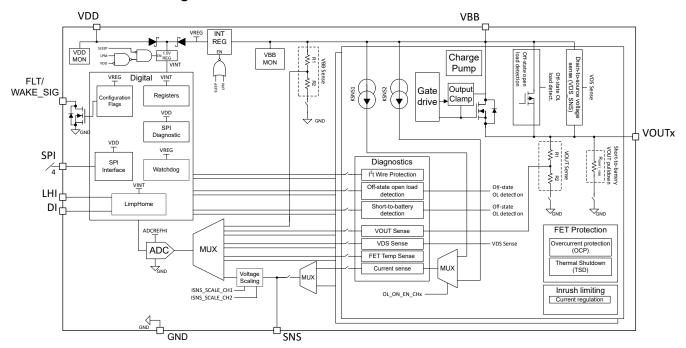

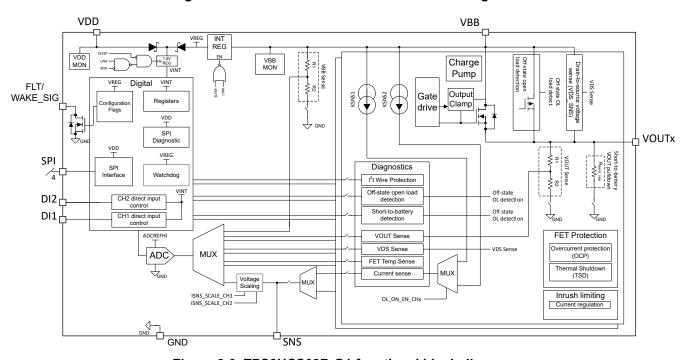

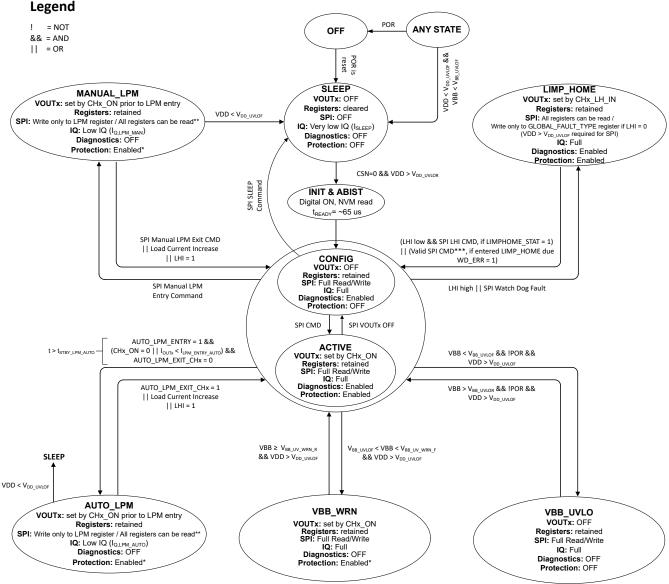

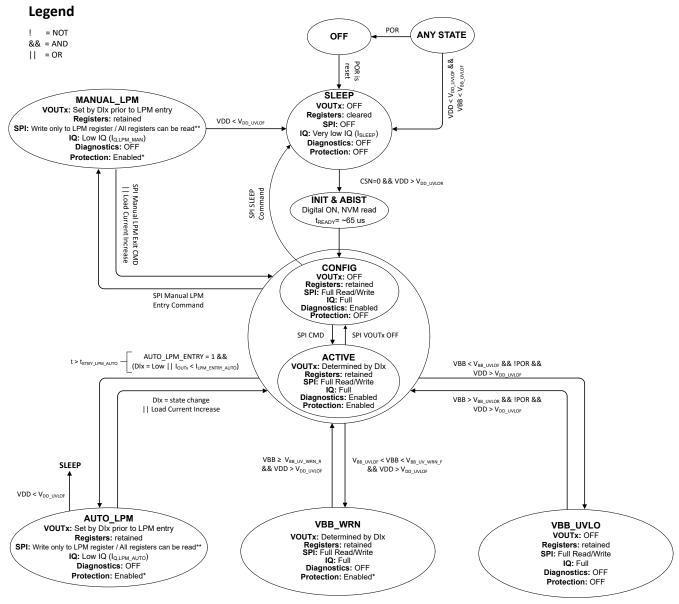

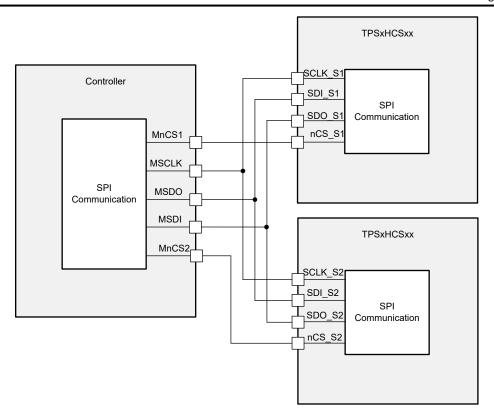

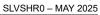

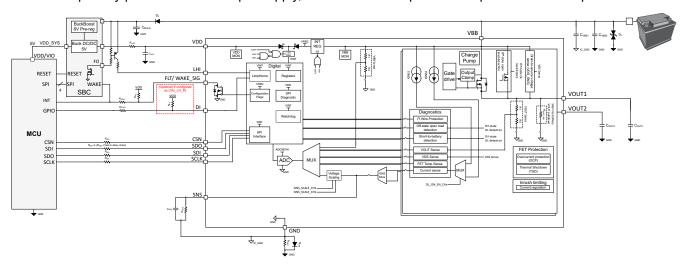

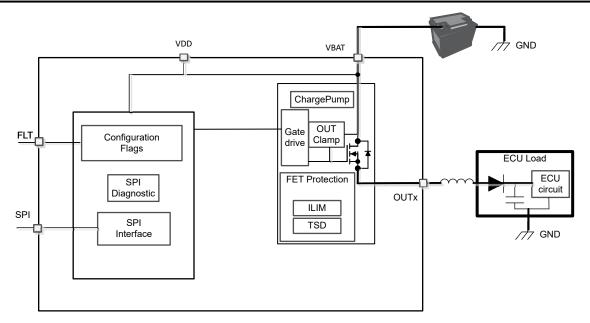

The TPS2HCS08-Q1 device is a dual channel, smart high-side switch controlled through a serial peripheral interface (SPI) and is intended for power distribution and actuator drive applications. The device integrates robust protection to ensure output wire and load protection against short circuit or overload conditions. The device features overcurrent protection configurable via SPI with sufficient flexibility to support loads that require large inrush currents and provide improved protection. The device also integrates a programmable fuse profile (current versus time) that turns off the switch under persistent overload condition. The two features together allow optimization of the wire harness for any load profile with full protection.

The device supports a SPI-configurable capacitive charging mode for ECU loads in power distribution switch applications. The device also includes two low power mode (LPM) states, an auto entry mode or a manual entry mode, that enables the device to provide current to the load ECU while only consuming about 10-20µA of current.

The TPS2HCS08-Q1 device also provides a high accuracy digital current sense over SPI that allows for improved load diagnostics. By reporting load current and the channel output voltage and output FET temperature to a system MCU, the device enables diagnosis of switch and load failures.

The TPS2HCS08-Q1 is available in a HTSSOP package which allows for reduced PCB footprint.

**Package Information**

| PART NUMBER  | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|--------------|------------------------|-----------------------------|

| TPS2HCS08-Q1 | PWP (HTSSOP, 16)       | 5mm x 6.4mm                 |

- For all available packages, see Section 12.

- The package size (length × width) is a nominal value and includes pins, where applicable.

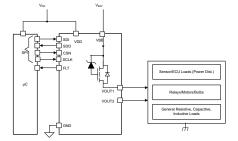

**Simplified Schematic**

## **Table of Contents**

| 1 Features1                           | 8.2 Functional Block Diagram21                           |

|---------------------------------------|----------------------------------------------------------|

| 2 Applications1                       | 8.3 Device Functional Modes21                            |

| 3 Description1                        | 8.4 Feature Description43                                |

| 4 Device Comparison Table3            | 8.5 Parallel Mode Operation62                            |

| 5 Pin Configuration and Functions4    | 8.6 TPS2HCS08 Registers65                                |

| 5.1 A Version Package4                | 9 Application and Implementation107                      |

| 5.2 Pinout - Version A4               |                                                          |

| 5.3 Version B Package5                |                                                          |

| 5.4 Pinout - Version B5               | 9.3 Power Supply Recommendations110                      |

| 6 Specifications6                     | 9.4 Layout111                                            |

| 6.1 Absolute Maximum Ratings6         | 10 Device and Documentation Support113                   |

| 6.2 ESD Ratings6                      | 10.1 Documentation Support113                            |

| 6.3 Recommended Operating Conditions6 | 10.2 Receiving Notification of Documentation Updates 113 |

| 6.4 Thermal Information7              | 10.3 Support Resources                                   |

| 6.5 Electrical Characteristics7       | 10.4 Trademarks113                                       |

| 6.6 SPI Timing Requirements13         | 10.5 Electrostatic Discharge Caution113                  |

| 6.7 Switching Characteristics13       | 10.6 Glossary113                                         |

| 6.8 Typical Characteristics15         | 11 Revision History113                                   |

| 7 Parameter Measurement Information19 | 12 Mechanical, Packaging, and Orderable                  |

| 8 Detailed Description20              | Information113                                           |

| 8.1 Overview20                        |                                                          |

# **4 Device Comparison Table**

# **Table 4-1. Device Options**

| Device<br>Version | Part Number   | Output Control in ACTIVE State | I2T Range Based on<br>R <sub>SNS</sub> = 700Ω | Overcurrent<br>Protection (I <sub>OCP</sub> )<br>Range | Limp Home<br>State |

|-------------------|---------------|--------------------------------|-----------------------------------------------|--------------------------------------------------------|--------------------|

| Α                 | TPS2HCS08A-Q1 | Set through SPI                | 8.8A <sup>2</sup> s to 350A <sup>2</sup> s    | 10A to 55A                                             | Yes                |

| В                 | TPS2HCS08B-Q1 | Set through DIx pins only      | 0.0A S to 330A S                              | 10A to 33A                                             | No                 |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

# **5 Pin Configuration and Functions**

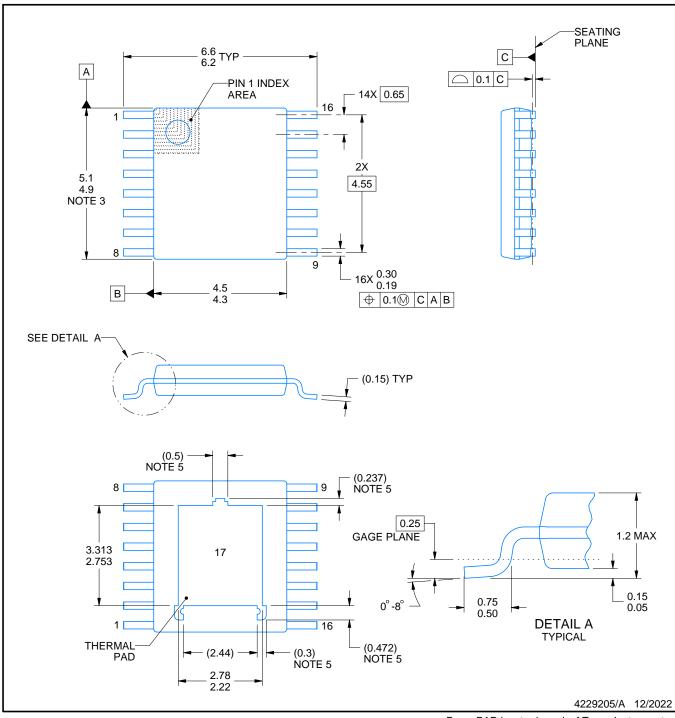

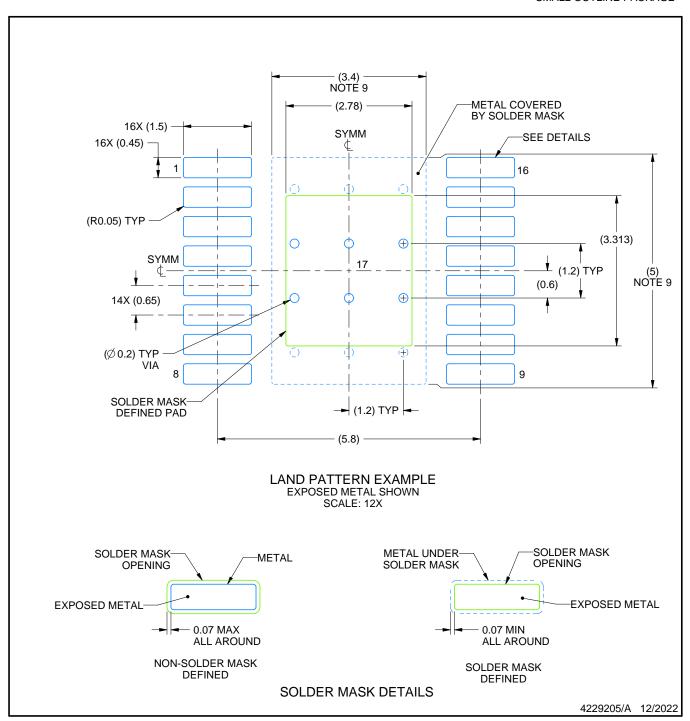

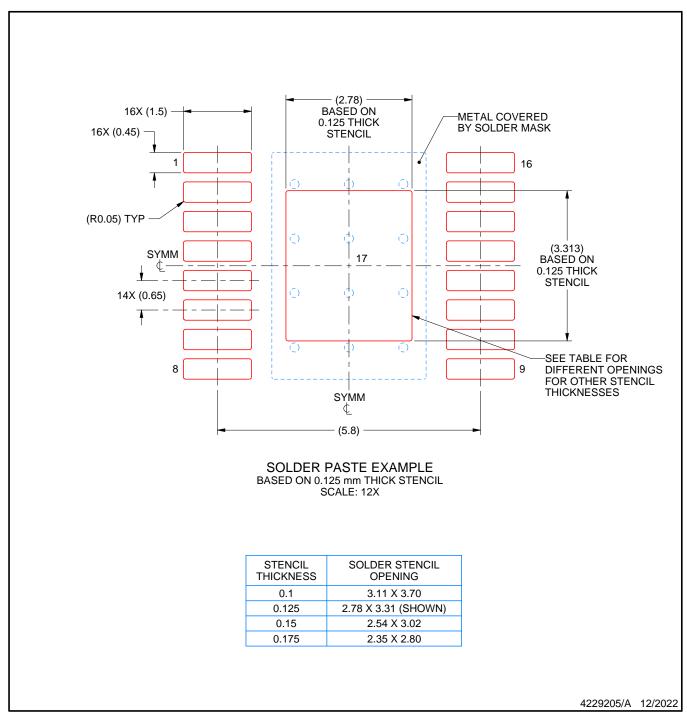

## 5.1 A Version Package

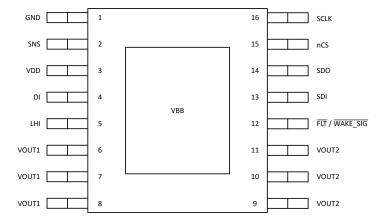

Figure 5-1. TPS2HCS08A-Q1 PWP Package,16-Pin HTSSOP (Top View)

### 5.2 Pinout - Version A

| Pin Number  | Pin Name          | Туре  | Description                                                                                                                                                                                                                     |

|-------------|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | GND               | GND   | Device ground                                                                                                                                                                                                                   |

| 2           | SNS               | 0     | SNS current output – use a parallel RC network to the GND pin of the IC.                                                                                                                                                        |

| 3           | VDD               | Power | Logic Supply Input – closely decouple to GND pin of the IC with a ceramic capacitor.                                                                                                                                            |

| 4           | DI                | I     | Sets the output behavior in the LIMP HOME mode, if configured as such. The pin needs to be connected to MCU or other HI/LO source through a 10K resistor tor protection and enabling the reverse polarity FET turn-on function. |

| 5           | LHI               | Į     | External input (active High) to enable LIMP HOME mode.                                                                                                                                                                          |

| 6,7,8       | VOUT1             | 0     | Output of channel 1                                                                                                                                                                                                             |

| 9,10,11     | VOUT2             | 0     | Output of channel 2                                                                                                                                                                                                             |

| 12          | FLT /<br>WAKE_SIG | 0     | Fault output – on any (one or more) channel - open drain, pull up with a 4.7K resistor to VDD pin. Also functions as a wake signal to the MCU upon load current demand in key-off mode.                                         |

| 13          | SDI               | I     | SPI device (secondary) data input                                                                                                                                                                                               |

| 14          | SDO               | 0     | SPI Data Output from the device. Internally pulled up to VDD.                                                                                                                                                                   |

| 15          | CSN               | I     | Chip select. Internally pulled up to VDD                                                                                                                                                                                        |

| 16          | SCLK              | I     | SPI Clock input                                                                                                                                                                                                                 |

| Thermal Pad | VBB               | Power | Power Supply                                                                                                                                                                                                                    |

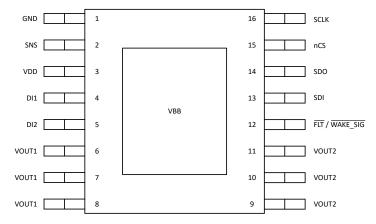

# 5.3 Version B Package

Figure 5-2. PWP Package, 16-Pin HTSSOP (Top View) - TPS2HCS08B-Q1

## 5.4 Pinout - Version B

| Pin Number  | Pin Name          | Туре  | Description                                                                                                                                                                                   |

|-------------|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | GND               | GND   | Device ground                                                                                                                                                                                 |

| 2           | SNS               | 0     | SNS current output – use a resistor to GND.                                                                                                                                                   |

| 3           | VDD               | Power | Logic Supply Input – closely decouple to GND pin of the IC with a ceramic 1uF capacitor.                                                                                                      |

| 4           | DI1               | I     | Enables channel 1 output to turn ON. The pin needs to be connected to MCU or other HI/LO source through a 10K resistor tor protection and enabling the reverse polarity FET turn-on function. |

| 5           | DI2               | I     | Enables channel 2 output to turn ON                                                                                                                                                           |

| 6,7,8       | VOUT1             | 0     | Output of channel 1                                                                                                                                                                           |

| 9,10,11     | VOUT2             | 0     | Output of channel 2                                                                                                                                                                           |

| 12          | FLT /<br>WAKE_SIG | 0     | Fault output – on any (one or more) channel - open drain, pull up with a 4.7K resistor to VDD pin. Also functions as a wake signal to the MCU upon load current demand in key-off mode.       |

| 13          | SDI               | I     | SPI device (secondary) data input                                                                                                                                                             |

| 14          | SDO               | 0     | SPI Data Output from the device. Internally pulled up to VDD.                                                                                                                                 |

| 15          | CSN               | I     | Chip select. Internally pulled up to VDD                                                                                                                                                      |

| 16          | SCLK              | I     | SPI Clock input                                                                                                                                                                               |

| Thermal Pad | VBB               | Power | Power Supply                                                                                                                                                                                  |

## **6 Specifications**

## 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                        |                                                                                                                        | MIN  | MAX                  | UNIT |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|----------------------|------|

| Maximum continuous supply voltage, V <sub>VBB</sub>    |                                                                                                                        |      | 28                   | V    |

| Load dump voltage                                      | ISO16750-2:2010(E)                                                                                                     |      | 36                   | V    |

| Maximum transient voltage on VBB pin, (example during  | g ISO 7637 pulse 2a transient) V <sub>BBt</sub>                                                                        |      | 54                   | V    |

| Short circuit supply voltage capability                | $I_{OCP}$ = 55A, $L_{OUT}$ = 5 $\mu$ H, $t_{SHORT}$ = 300ms, $T_A$ = 125°C                                             |      | 24                   | V    |

| Short circuit supply voltage capability, parallel mode | PARALLEL_12 = 1, I <sub>OCP</sub> = 40A, L <sub>OUT</sub> = 5μH,<br>t <sub>SHORT</sub> = 300ms, T <sub>A</sub> = 125°C |      | 24                   | V    |

| VOUT voltage                                           |                                                                                                                        | -30  | V <sub>VS</sub> +0.3 | V    |

| Reverse polarity voltage, continuous on VBB pin        |                                                                                                                        | -18  |                      | V    |

| Low voltage supply pin voltage, V <sub>DD</sub>        |                                                                                                                        | -0.3 | 7                    | V    |

| Digital input pin voltages, V <sub>DIG</sub>           | SDI, SDO, SCLK, CS                                                                                                     | -0.3 | 7                    | V    |

| Sense pin voltage, V <sub>SNS</sub>                    |                                                                                                                        | -0.3 | 7                    | V    |

| FLT pin voltage, V <sub>FLT</sub>                      |                                                                                                                        | -0.3 | 7                    | V    |

| Limp home activation pin voltage, V <sub>LHI</sub>     |                                                                                                                        |      | V <sub>BB</sub>      | V    |

| Limp home direct input pin voltages, V <sub>DI</sub>   |                                                                                                                        | -0.3 | 7                    | V    |

| Reverse ground current, I <sub>GND</sub>               | V <sub>BB</sub> < 0 V                                                                                                  |      | -50                  | mA   |

| Maximum junction temperature, T <sub>J</sub>           | •                                                                                                                      |      | 150                  | °C   |

| Storage temperature, T <sub>stg</sub>                  |                                                                                                                        | -65  | 150                  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                    |                                        |                                                                                     |                                  | VALUE | UNIT |

|--------------------|----------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|-------|------|

|                    |                                        | Human-body model (HBM), per AEC<br>Q100-002 Classification Level H2                 | All pins including VBB and VOUTx | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge <sup>(1)</sup> | Human-body model (HBM), per AEC<br>Q100-002 Classification Level H3A <sup>(2)</sup> | VBB and VOUTx                    | ±4000 | V    |

|                    |                                        | Charged-device model (CDM), per AEC Q100-011 Classification Level C5                | All pins                         | ±750  |      |

- (1) AEC-Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specifications.

- (2) ESD strikes are with reference from the pin mentioned to GND

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                     |                               |                                                                                          | MIN  | MAX | UNIT |

|---------------------|-------------------------------|------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>BB_NOM</sub> | Nominal supply voltage        | minal supply voltage                                                                     |      | 18  | V    |

| V <sub>BB_EXT</sub> | Extended supply voltage       | See the conditions in section 9.2, power supply recommendations, operating voltage range | 3    | 28  | V    |

| $V_{DD}$            | Low voltage supply voltage    | ow voltage supply voltage                                                                |      | 5.5 | V    |

| $V_{DIG}$           | All digital input pin voltage | All digital input pin voltage                                                            |      | 5.5 | V    |

| V <sub>FLT</sub>    | FLT pin voltage               |                                                                                          | -0.3 | 5.5 | V    |

over operating free-air temperature range (unless otherwise noted)

|                 |                                        | MIN  | MAX      | UNIT |

|-----------------|----------------------------------------|------|----------|------|

| $V_{LHI}$       | Limp home activation pin voltage, LHI  |      | $V_{BB}$ | V    |

| V <sub>DI</sub> | Limp home direct pin input voltage, DI | -0.3 | 5.5      | V    |

| T <sub>A</sub>  | Operating free-air temperature         | -40  | 125      | °C   |

## **6.4 Thermal Information**

|                       |                                              | TPS2HCS08-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup> (2)            | PWP          | UNIT |

|                       |                                              | 16 PINS      |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 32.1         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.8         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 8.4          | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 2.0          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 8.4          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.2          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the <a href="https://www.ti.com/lit/an/spra953c/spra953c.pdf">https://www.ti.com/lit/an/spra953c/spra953c.pdf</a> application report.

### 6.5 Electrical Characteristics

$V_{BB}$  = 6V to 18V,  $V_{DD}$  = 3.0V to 5.5V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

|                          | PARAMETER                                      | TEST COI                                                           | NDITIONS                                                                                           | MIN  | TYP | MAX  | UNIT |

|--------------------------|------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|-----|------|------|

| INPUT VOLTA              | GE AND CURRENT                                 |                                                                    |                                                                                                    |      |     |      |      |

|                          |                                                | I <sub>OUT</sub> = 10mA VBB > 28V                                  | T <sub>J</sub> = 25°C to 150°C                                                                     | 35   | 40  | 45   | V    |

| $V_{Clamp}$              | VDS clamp voltage                              | I <sub>OUT</sub> = 10mA 12V < VBB < 28V                            | $T_{J} = -40^{\circ}\text{C to } 150^{\circ}\text{C}$                                              | 30   | 34  | 38   | V    |

|                          |                                                | I <sub>OUT</sub> = 10mA VBB = 3V                                   | $T_{\rm J}$ = -40°C to 150°C                                                                       | 27.5 | ,   | 36.5 | V    |

| V <sub>BB_UVLOR</sub>    | V <sub>BB</sub> undervoltage lockout rising    | Magazired with respect to the                                      | CND pip of the device                                                                              | 3.0  | 3.5 | 4.0  | V    |

| V <sub>BB_UVLOF</sub>    | V <sub>BB</sub> undervoltage lockout falling   | - weasured with respect to the                                     | sured with respect to the GND pin of the device.  sured with respect to the GND pin of the device. | 2.6  | 2.8 | 3.0  | V    |

| V <sub>BB_UV_WRN_R</sub> | VBB voltage UV_WRN rising threshold            | Na                                                                 | easured with respect to the GND pin of the device.                                                 |      | 4.9 |      | ٧    |

| V <sub>BB_UV_WRN_F</sub> | VBB voltage UV_WRN falling threshold threshold | - Measured with respect to the                                     |                                                                                                    | 4.5  |     | ٧    |      |

| V <sub>VDD_UVLOR</sub>   | V <sub>VDD</sub> undervoltage lockout rising   | NA                                                                 | easured with respect to the GND pin of the device                                                  |      |     | 2.2  | ٧    |

| V <sub>VDD_UVLOF</sub>   | V <sub>VDD</sub> undervoltage lockout falling  | - Measured with respect to the                                     | e GND pin of the device                                                                            | 1.86 |     | 2.07 | V    |

|                          | Sleep current (total device                    | V <sub>BB</sub> ≤ 18V, device in SLEEP                             | •                                                                                                  |      |     | 0.5  | μA   |

| I <sub>SLEEP,VBB</sub>   | leakage including all MOSFET channels)         | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$              | 2.2                                                                                                | μΑ   |     |      |      |

| 1                        | Class summent from VDD win                     | V <sub>VDD</sub> ≤ 5.5V, device in                                 | T <sub>J</sub> = 25°C                                                                              |      |     | 0.3  | μA   |

| I <sub>SLEEP,VDD</sub>   | Sleep current from VDD pin                     | SLEEP mode, V <sub>OUT</sub> = 0V                                  | T <sub>J</sub> = 85°C                                                                              |      |     | 0.5  | μΑ   |

| I <sub>OUT(OFF)</sub>    | Output leakage current (per channel)           | V <sub>OUT</sub> = 0V, Channel<br>disabled,<br>ACTIVE/CONFIG state | T <sub>J</sub> = -40 to 125°C                                                                      |      | 1   | 14   | μΑ   |

<sup>(2)</sup> The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

$V_{BB}$  = 6V to 18V,  $V_{DD}$  = 3.0V to 5.5V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

|                      | PARAMETER                                                                                            | TEST CO                                             | NDITIONS                 | MIN TYP | MAX                      | UNIT |

|----------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------|---------|--------------------------|------|

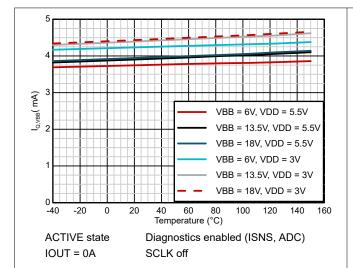

|                      |                                                                                                      | ACTIVE state, SCLK off                              |                          | 1.4     | 1.6                      | mA   |

| $I_{Q,VDD}$          | VDD quiescent current                                                                                | ACTIVE state, SCLK ON                               | V <sub>DD</sub> = 5.5V   |         | 2.2                      | mA   |

|                      |                                                                                                      | All channels enabled, I <sub>OUTx</sub>             | V <sub>DD</sub> = 5.5V   | 3.8     | 4.3                      | mA   |

| $I_{Q,VBB}$          | V <sub>BB</sub> quiescent current                                                                    | = 0A, SCLK off, Diagnostics disabled                | V <sub>DD</sub> = 3.0V   | 4.25    | 5.2                      | mA   |

| ·Q,VBB               | A BB datescent can out                                                                               | All channels enabled, I <sub>OUTx</sub>             | V <sub>DD</sub> = 5.5V   | 3.9     | 4.5                      | mA   |

|                      |                                                                                                      | = 0A, SCLK off, Diagnostics enabled (ISNS, ADC)     | V <sub>DD</sub> = 0V     | 4.4     | 1.6<br>2.2<br>4.3<br>5.2 | mA   |

|                      | Continuous load current, per                                                                         | All channels enabled, T <sub>AMB</sub>              | = 85°C                   | 8       |                          | Α    |

| I <sub>L,CONT</sub>  | channel                                                                                              | One channel enabled, T <sub>AMB</sub>               | = 85°C                   | 13      |                          | Α    |

| RON CHARA            | ACTERISTICS                                                                                          |                                                     |                          |         |                          | •    |

| Р                    | On registance                                                                                        | 6V ≤ V <sub>BB</sub> ≤ 28V, I <sub>OUTx</sub> = 1A, | T <sub>J</sub> = 25°C    | 8.9     |                          | mΩ   |

| R <sub>ON</sub>      | On-resistance                                                                                        | OL_ON_EN_CH1 = 0                                    | T <sub>J</sub> = 150°C   |         | 17.8                     | mΩ   |

|                      | On-resistance, OL_ON                                                                                 | 6V ≤ V <sub>BB</sub> ≤                              | T <sub>J</sub> = 25°C    | 27      |                          | mΩ   |

| R <sub>ON_OL</sub>   | mode                                                                                                 | 28V, I <sub>OUTx</sub> = 0.3A,<br>OL_ON_EN_CHx = 1  | T <sub>J</sub> = 150°C   |         | 54                       | mΩ   |

| Р                    | On-resistance during                                                                                 | -18V ≤ V <sub>BB</sub> ≤ -7V,                       | T <sub>J</sub> = 25°C    | 9.5     |                          | mΩ   |

| $R_{ON(REV)}$        | reverse polarity                                                                                     | Version A & B                                       | T <sub>J</sub> = 150°C   |         | 20                       | mΩ   |

| ΔR <sub>ON</sub>     | Percentage difference in on-resistance between channels (R <sub>ON,CHx</sub> - R <sub>ON,CHy</sub> ) | V <sub>BB</sub> ≥ 6V, T <sub>J</sub> = 25°C         |                          | 0.5     | 7                        | %    |

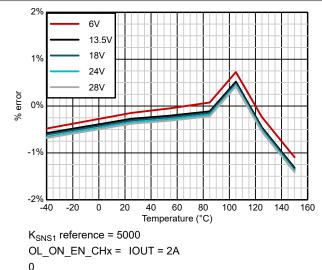

| CURRENT S            | SENSE CHARACTERISTICS                                                                                |                                                     |                          |         |                          |      |

| K <sub>SNS1</sub>    | Current sense ratio                                                                                  | I <sub>OUT</sub> = 1.0A, OL_ON_EN_C                 | 1x = 0                   | 5000    |                          |      |

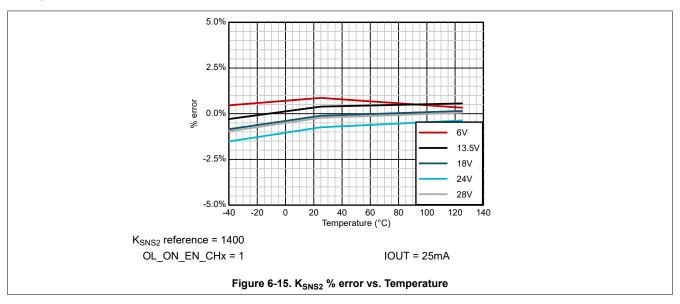

| K <sub>SNS2</sub>    | Current sense ratio                                                                                  | I <sub>OUT</sub> = 50mA, OL_ON_EN_C                 | CHx = 1                  | 1400    |                          |      |

| I <sub>SNS_SAT</sub> | Saturated sense current                                                                              | VBB > 6V, RSNS = 374Ω<br>OL_ON_EN_CHx =0            | I <sub>OUT</sub> = > 30A | 6       |                          | mA   |

|                      |                                                                                                      | RSNS = 374Ω,                                        | 1 - 204                  | 5000    |                          |      |

| K <sub>SNS2</sub>    |                                                                                                      | OL_ON_EN_CHx = 0                                    | I <sub>OUT</sub> = 20A   | -3      | 3                        | %    |

|                      |                                                                                                      |                                                     | 1 - 400                  | 5000    |                          |      |

|                      |                                                                                                      |                                                     | I <sub>OUT</sub> = 10A   | -4      | 4                        | %    |

|                      |                                                                                                      |                                                     | I <sub>OUT</sub> = 5A    | 5000    |                          |      |

|                      |                                                                                                      |                                                     | IOUT - 3A                | -5      | 5                        | %    |

|                      |                                                                                                      |                                                     | I - 2.5A                 | 5000    |                          |      |

| IZ.                  | K <sub>SNS1</sub> ratio I <sub>OUT</sub> / I <sub>SNS1</sub>                                         |                                                     | I <sub>OUT</sub> = 2.5A  | -5      | 5                        | %    |

| K <sub>SNS1</sub>    | across I <sub>OUT</sub>                                                                              | RSNS = 698Ω                                         | 4 A                      | 5000    |                          |      |

|                      |                                                                                                      | OL_ON_EN_CHx = 0                                    | I <sub>OUT</sub> = 1A    | -5      | 5                        | %    |

|                      |                                                                                                      |                                                     | I - 500 A                | 5000    |                          |      |

|                      |                                                                                                      |                                                     | I <sub>OUT</sub> = 500mA | -7      | 7                        | %    |

|                      |                                                                                                      |                                                     | 050 A                    | 5000    |                          |      |

|                      |                                                                                                      |                                                     | I <sub>OUT</sub> = 250mA | -10     | 10                       | %    |

|                      |                                                                                                      |                                                     | 100                      | 5000    |                          |      |

|                      |                                                                                                      |                                                     | I <sub>OUT</sub> = 100mA | -18     | 18                       | %    |

Submit Document Feedback

Product Folder Links: TPS2HCS08-Q1

$V_{BB}$  = 6V to 18V,  $V_{DD}$  = 3.0V to 5.5V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

| PARAMETER                |                                                              | TEST CONDITIONS                                                          |                          | MIN   | TYP  | MAX  | UNIT |

|--------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|-------|------|------|------|

|                          |                                                              |                                                                          | 050 4                    |       | 1400 |      |      |

|                          |                                                              |                                                                          | I <sub>OUT</sub> = 250mA | -10   | ,    | 10   | %    |

|                          |                                                              |                                                                          | 1. 4004                  |       | 1400 |      |      |

|                          |                                                              |                                                                          | I <sub>OUT</sub> = 100mA | -10   |      | 10   | %    |

| 17                       | K <sub>SNS2</sub> ratio I <sub>OUT</sub> /                   | RSNS = 698Ω                                                              | I 50 A                   |       | 1400 |      |      |

| K <sub>SNS2</sub>        | I <sub>SNS2</sub> across I <sub>OUT</sub>                    | OL_ON_EN_CHx = 1                                                         | I <sub>OUT</sub> = 50mA  | -12   |      | 12   | %    |

|                          |                                                              |                                                                          | J. 05A                   | ,     | 1400 |      |      |

|                          |                                                              |                                                                          | I <sub>OUT</sub> = 25mA  | -20   | ,    | 20   | %    |

|                          |                                                              |                                                                          | 1 40 - 4                 |       | 1400 |      |      |

|                          |                                                              |                                                                          | I <sub>OUT</sub> = 10mA  | 40    |      | 40   | %    |

| I <sub>ENTRY_OL_ON</sub> | I <sub>OUT</sub> current to enter OL_ON                      | mode (OL_ON_EN_CHx = 1)                                                  | mode (OL_ON_EN_CHx = 1)  |       | ,    |      | Α    |

| I <sub>EXIT_OL_ON</sub>  | I <sub>OUT</sub> current to exit OL_ON m                     | node (OL_ON_EN_CHx = 1)                                                  |                          | ,     | ,    | 1.7  | Α    |

| ADC CHARAC               | TERISTICS                                                    |                                                                          |                          |       | ,    |      |      |

| V <sub>ADCREFHI</sub>    | ADC reference voltage                                        |                                                                          |                          | 2.76  | 2.81 | 2.9  | V    |

| Isample                  | Current sense sampling time                                  | Including mux timing and AD                                              | C conversion time        | 50    |      |      | μs   |

| I <sub>ADC</sub>         | ADC current consumption                                      |                                                                          |                          |       |      | 0.5  | mA   |

| SNS CHARAC               | TERISTICS                                                    |                                                                          |                          |       |      |      |      |

|                          | ISNS ADC accuracy                                            |                                                                          | SNS pin voltage = 2.7V   | -3    |      | 3    | %    |

|                          |                                                              | OL_ON_EN_CHx =1, ISNS_SCALE_CHx = 1  OL_ON_EN_CHx =1, ISNS_SCALE_CHx = 8 | SNS pin voltage = 1.4V   | -3.25 |      | 3.25 | %    |

|                          |                                                              |                                                                          | SNS pin voltage = 0.7V   | -4    |      | 4    | %    |

| ISNS <sub>ADC,ACC</sub>  |                                                              |                                                                          | SNS pin voltage = 0.1V   | -15   |      | 15   | %    |

|                          |                                                              |                                                                          | SNS pin voltage = 0.04V  | -10.5 |      | 10.5 | %    |

|                          |                                                              |                                                                          | SNS pin voltage = 0.01V  | -37.5 |      | 37.5 | %    |

| ADC <sub>TSNS</sub>      | T <sub>SNS</sub> ADC output code                             | T <sub>J</sub> = 25°C                                                    | Includes buffer gain     |       | 474  |      |      |

| TSNS <sub>ACC</sub>      | T <sub>SNS</sub> measurement accuracy                        |                                                                          |                          | -17   |      | 17   | °C   |

| ADC <sub>VSNS</sub>      | ADC code of output voltage measurement                       | VOUTx = 13.5V, referenced to device GND                                  | Includes buffer gain     |       | 459  |      |      |

| VSNS <sub>ACC</sub>      | VOUT SNS<br>(VSNS) measurement<br>accuracy                   |                                                                          |                          | -5    |      | 5    | %    |

| ADC <sub>VBBSNS</sub>    | ADC code of VBB voltage measurement                          | VBB = 13.5V, referenced to device GND                                    | Includes buffer gain     |       | 452  |      |      |

| VBBSNS <sub>ACC</sub>    | VBB SNS<br>(VBBSNS) measurement<br>accuracy                  |                                                                          |                          | -5    |      | 5    | %    |

| OVERCURREN               | NT PROTECTION CHARACTE                                       | RISTICS                                                                  |                          |       |      |      |      |

| I <sub>OCP_RANGE</sub>   | Overcurrent protection threshold, immediate shutdown - range | di/dt = 2A/μs                                                            |                          | 10    |      | 55   | А    |

$V_{BB}$  = 6V to 18V,  $V_{DD}$  = 3.0V to 5.5V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

| PARAMETER                            |                                                                                        | TEST CONDITIONS                                                                                                                            |                                                                                                            | MIN  | TYP    | MAX   | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|--------|-------|------|

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0x0                                                                                       |      | 10     |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0x1                                                                                       |      | 12.5   |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0x2                                                                                       |      | 15     |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0x3                                                                                       |      | 17.5   |       | Α    |

|                                      | Overcurrent protection                                                                 |                                                                                                                                            | ILIMIT_SET_CHx = 0x4                                                                                       |      | 20     |       | Α    |

| I <sub>OCP</sub>                     | threshold, immediate                                                                   | di/dt = 2A/µs                                                                                                                              | ILIMIT_SET_CHx = 0x5                                                                                       |      | 22.5   |       | Α    |

|                                      | shutdown                                                                               | $T_J = -40^{\circ}\text{C to } 150^{\circ}\text{C}$                                                                                        | ILIMIT_SET_CHx = 0x6                                                                                       |      | 25     |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0x7                                                                                       |      | 32.5   |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0x8                                                                                       |      | 40     |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0x9                                                                                       |      | 47.5   |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | ILIMIT_SET_CHx = 0xA                                                                                       |      | 55     |       | Α    |

| I <sub>OCP_</sub> RANGE,PARA<br>LLEL | Overcurrent protection<br>threshold, immediate<br>shutdown - range in parallel<br>mode | di/dt = 2A/μs<br>PARALLEL_12 = 1                                                                                                           |                                                                                                            | 10   |        | 40    | А    |

| I <sub>OCP_RETRY_FLBK</sub>          | Overcurrent protection foldback threshold, immediate shutdown mode                     | Only applicable for CAP_CHRG_CHx = 00 and I <sub>OCP</sub> > 47.5A, n <sub>RETRY</sub> > 7, di/dt = 2A/µs, T <sub>J</sub> = -40°C to 150°C |                                                                                                            |      | 47.5   |       | А    |

| t <sub>OCP_DETECT</sub>              | Immediate shutdown detection time                                                      | T <sub>J</sub> = -40°C to 150°C                                                                                                            | From $I_{OUT} = I_{OCP}$ to $I_{OCP}$ detection $R_{OUT} = 150\%$ of $I_{OCP}$ , $L_{IN} = L_{OUT} = 0$ nH | 0.3  |        | 1.5   | us   |

| t <sub>OCP_TOFF</sub>                | Immediate shutdown turn off time                                                       | T <sub>J</sub> = -40°C to 150°C                                                                                                            | From $I_{OCP}$ detection to 10% of $V_{OUTx}$ $R_{OUT}$ = 150% of $I_{OCP}$ , $L_{IN}$ = $L_{OUT}$ = 0nH   |      |        | 7.5   | us   |

| I <sub>OCP_TEMP_COMP</sub>           | I <sub>OCP</sub> high temperature compensation                                         | T <sub>J</sub> ≥ 85°C, I <sub>OCP</sub> ≥ 47.5A                                                                                            |                                                                                                            |      | -0.375 |       | %/°C |

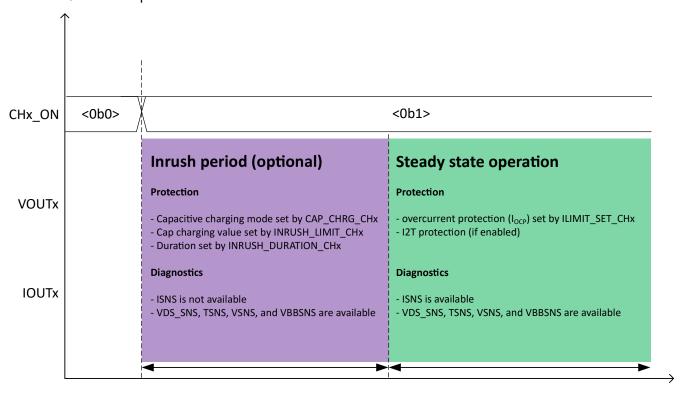

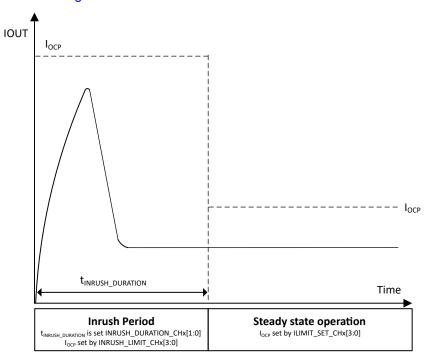

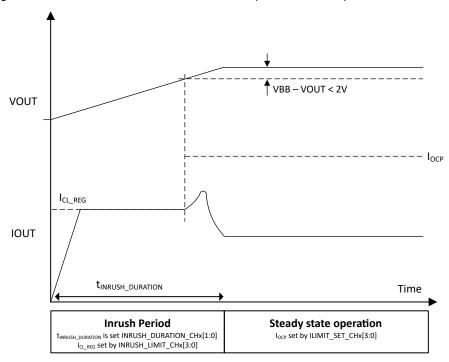

| CAP CHRG CUF                         | RRENT LIMITATION                                                                       |                                                                                                                                            |                                                                                                            |      |        |       |      |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 0                                                                                       | 0.81 | 1.67   | 2.485 | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 1                                                                                       |      | 2      |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 2                                                                                       |      | 2.4    |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 3                                                                                       |      | 2.8    |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 4                                                                                       | 1.7  | 3.3    | 5     | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 5                                                                                       |      | 3.6    |       | Α    |

| I <sub>CL_Reg</sub>                  | Current regulation mode                                                                | $T_J = -40^{\circ}\text{C to } 150^{\circ}\text{C}$<br>dI/dt < 0.01A/ms                                                                    | INRUSH_LIMIT_CHx = 6                                                                                       |      | 4.2    |       | Α    |

|                                      | current in inrush period                                                               | di/dt < 0.01A/ms                                                                                                                           | INRUSH_LIMIT_CHx = 7                                                                                       |      | 5.5    |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 8                                                                                       |      | 6.8    |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = 9                                                                                       |      | 8.1    |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = A                                                                                       |      | 9.5    |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = B                                                                                       |      | 11     |       | Α    |

|                                      |                                                                                        |                                                                                                                                            | INRUSH_LIMIT_CHx = C                                                                                       |      | 12     |       | Α    |

| CAPACITIVE CH                        | HARGING                                                                                | <u> </u>                                                                                                                                   |                                                                                                            |      |        |       |      |

| t <sub>INRUSH_RANGE</sub>            | Inrush duration settings range                                                         | INRUSH_DURATION_CH                                                                                                                         | x range                                                                                                    | 0    |        | 100   | ms   |

| FAULT CHARAC                         |                                                                                        |                                                                                                                                            |                                                                                                            |      |        |       |      |

$V_{BB}$  = 6V to 18V,  $V_{DD}$  = 3.0V to 5.5V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

| PARAMETER                   |                                                                              | TEST CONDITIONS                                                                                                                   |                                                       | MIN   | TYP  | MAX  | UNIT |

|-----------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------|------|------|------|

|                             |                                                                              |                                                                                                                                   | OL_PULLUP_STR=00                                      | 20.1  | 26.5 | 100  | μA   |

|                             | Off state open-load (OL) detection internal pull-up current                  | Switch disabled,                                                                                                                  | OL_PULLUP_STR=01                                      | 48.1  | 60   | 126  | μA   |

| I <sub>OL_OFF</sub>         |                                                                              | OL_OFF_EN_CHx = enabled                                                                                                           | OL_PULLUP_STR=10                                      | 103.2 | 127  | 208  | μA   |

|                             | ourione                                                                      | Chabled                                                                                                                           | OL PULLUP STR=11                                      | 213   | 260  | 348  | μA   |

| R <sub>SHRT_VBB</sub>       | Off state short to VBB detection pulldown resistance                         | Channel disabled, off-state senabled                                                                                              | hort_VBB diagnostics                                  | 5.5   | 6.8  | 8    | kΩ   |

| V <sub>OL_OFF_TH</sub>      | Off state Open-load (OL) detection voltage                                   | Channel Disabled, off-state of enabled, V <sub>OUTx</sub>                                                                         | open load diagnostics                                 | 1.9   | 2.5  | 2.95 | V    |

| T <sub>ABS</sub>            | Thermal shutdown                                                             |                                                                                                                                   |                                                       | 155   | 180  | 205  | °C   |

| T <sub>OTW</sub>            | Thermal shutdown warning                                                     |                                                                                                                                   |                                                       | 130   | 150  | 170  | °C   |

| T <sub>REL</sub>            | Relative thermal shutdown temperature                                        |                                                                                                                                   |                                                       |       | 60   |      | °C   |

| T <sub>HYS</sub>            | Thermal shutdown hysteresis                                                  |                                                                                                                                   |                                                       | 20    | 25   | 30   | °C   |

| n <sub>RETRY, INT</sub>     | Number of retry cycles before I <sub>OCP</sub> = I <sub>OCP</sub> RETRY FLBK | Only applicable for CAP_CH 47.5A                                                                                                  | RG_CHx = 00 and I <sub>OCP</sub> >                    |       | 7    |      |      |

| t <sub>RETRY</sub>          | Retry time                                                                   | Time from fault shutdown until switch re-enable (thermal shutdown or overcurrent). PWM will wait until next cycle to come back on |                                                       |       | 2    |      | ms   |

| t <sub>WAKE_SIG</sub>       | WAKE_SIG / FLT pin indication for LPM exit                                   |                                                                                                                                   |                                                       |       | 100  |      | μs   |

| TIMING CHARA                | CTERISTICS                                                                   |                                                                                                                                   |                                                       |       |      |      |      |

| OSC <sub>ACC</sub>          | Oscillator accuracy                                                          |                                                                                                                                   |                                                       | -10   |      | 10   | %    |

| PWM <sub>FREQ</sub>         | PWM Frequency                                                                | PWM_EN = 1                                                                                                                        | PWM_FREQ_CHx = 101                                    | 372   | 425  | 478  | Hz   |

| LOW POWER M                 | ODE CHARACTERISTICS                                                          | 1                                                                                                                                 |                                                       |       |      |      |      |

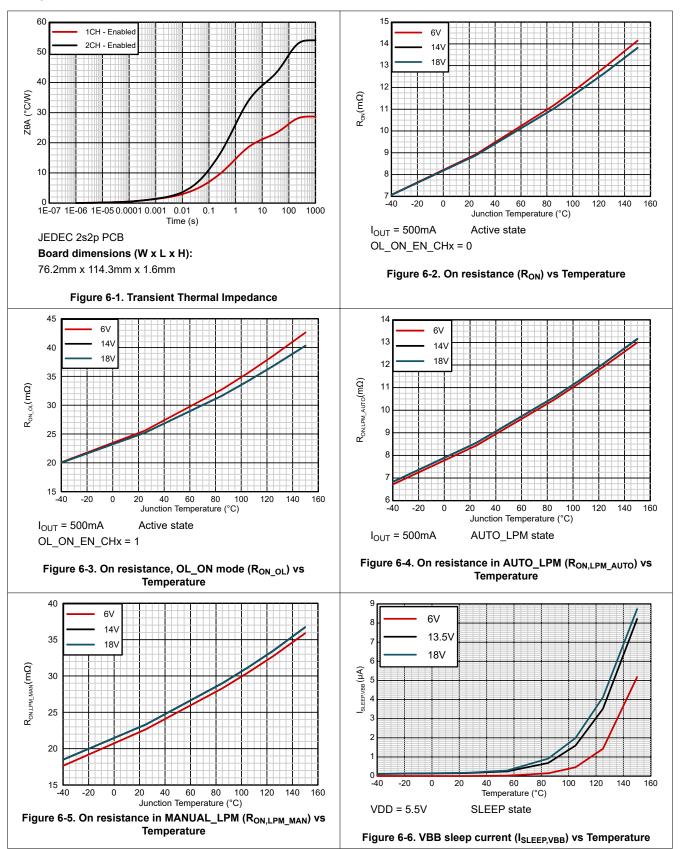

| R <sub>ON,LPM_AUTO</sub>    | R <sub>ON</sub> in AUTO_LPM mode                                             |                                                                                                                                   | $T_{J} = -40^{\circ}\text{C to } 105^{\circ}\text{C}$ |       | 9    | 18   | mΩ   |

| R <sub>ON,LPM_MAN</sub>     | R <sub>ON</sub> in MANUAL_LPM mode                                           |                                                                                                                                   | T <sub>J</sub> = -40°C to 105°C                       |       | 28   | 58   | mΩ   |

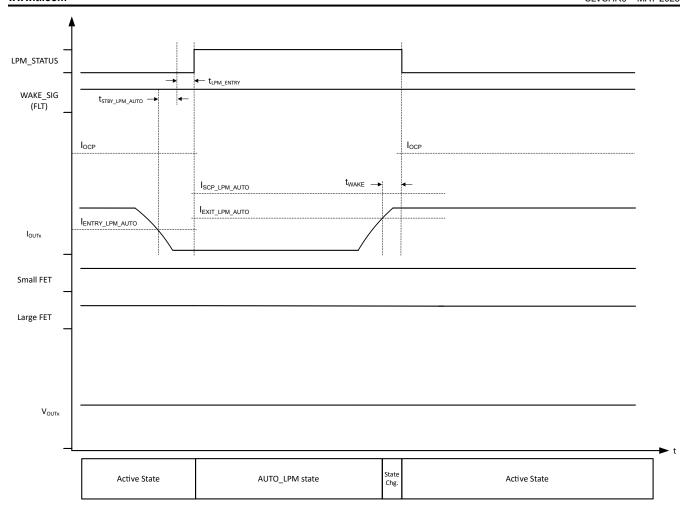

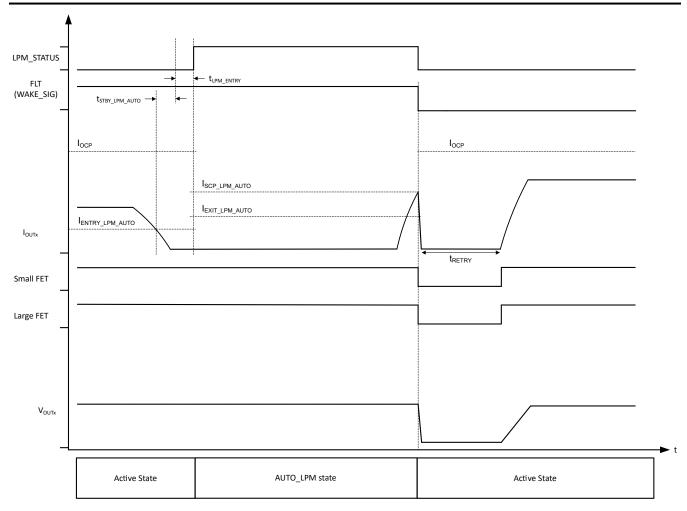

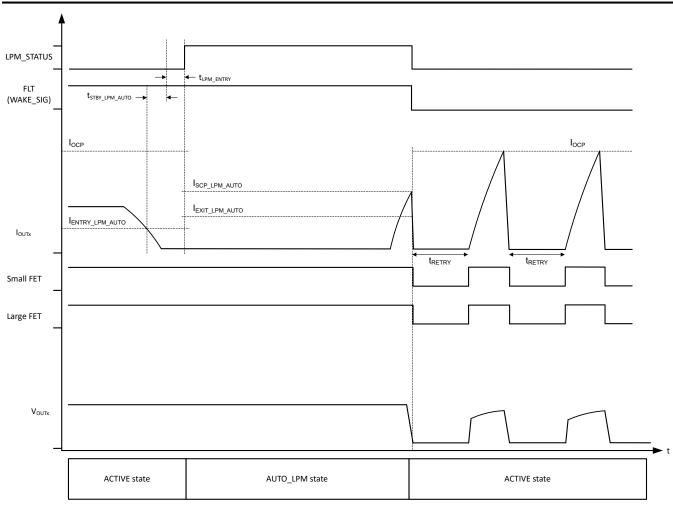

| I <sub>ENTRY_LPM_AUTO</sub> | I <sub>OUT</sub> current to enter<br>AUTO_LPM state                          |                                                                                                                                   | T <sub>J</sub> = -40°C to 105°C                       |       | 0.95 |      | Α    |

| I <sub>EXIT_LPM_AUTO</sub>  | I <sub>OUT</sub> current to exit<br>AUTO_LPM state                           |                                                                                                                                   | T <sub>J</sub> = -40°C to 105°C                       |       | 1.05 |      | Α    |

| I <sub>SCP_LPM_AUTO</sub>   | Short-circuit detection threshold for AUTO_LPM state                         |                                                                                                                                   | T <sub>J</sub> = -40°C to 105°C                       |       | 13.7 |      | Α    |

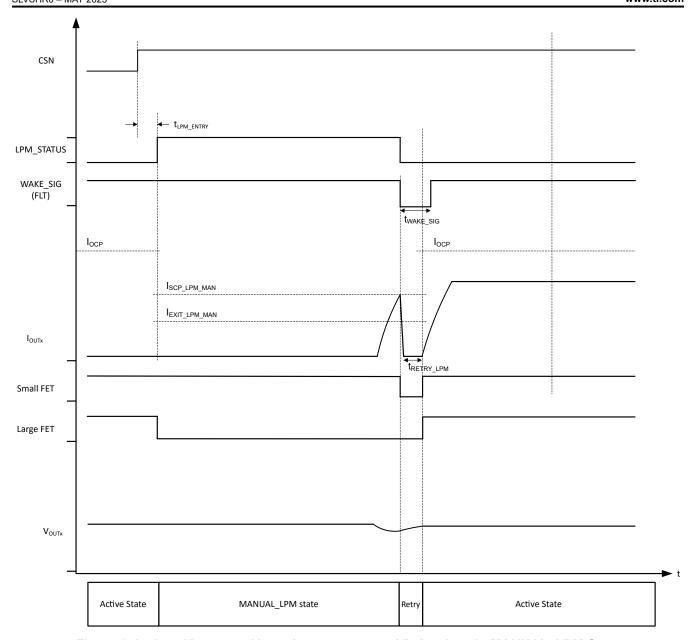

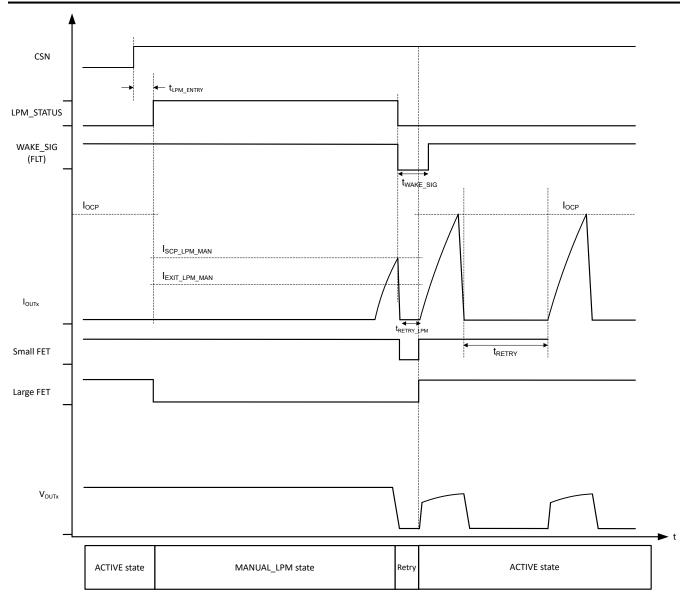

|                             |                                                                              |                                                                                                                                   | MAN_LPM_EXIT_CURR_<br>CHx = 00                        | 365   | 530  | 690  | mA   |

|                             | IOUTx threshold for                                                          | Current ramp at 1mA/µs T <sub>J</sub>                                                                                             | MAN_LPM_EXIT_CURR_<br>CHx = 01                        | 500   | 700  | 915  | mA   |

| <sup>I</sup> EXIT_LPM_MAN   | MANUAL_LPM exit                                                              | = -40°C to 85°C                                                                                                                   | MAN_LPM_EXIT_CURR_<br>CHx = 10                        | 114   | 165  | 236  | mA   |

|                             |                                                                              |                                                                                                                                   | MAN_LPM_EXIT_CURR_<br>CHx = 11                        | 240   | 350  | 460  | mA   |

| I <sub>SCP_LPM_MAN</sub>    | Load current when the channel detects a short circuit                        | di/dt = 5mA/µs                                                                                                                    | LPM exit test mode                                    |       | 4.0  |      | А    |

| t <sub>RETRY_LPM</sub>      | Retry time in LPM state                                                      |                                                                                                                                   |                                                       |       | 5    |      | μs   |

| t <sub>STBY_LPM_AUTO</sub>  | standby time before enter AUTO_LPM state                                     | I <sub>OUTx</sub> ≤ I <sub>ENTRY_LPM_AUTO</sub>                                                                                   |                                                       |       | 20   |      | ms   |

$V_{BB}$  = 6V to 18V,  $V_{DD}$  = 3.0V to 5.5V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

| PARAMETER                    |                                                              | TEST CONDITIONS                                                                   |                        | MIN                       | TYP  | MAX                       | UNIT  |

|------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|---------------------------|------|---------------------------|-------|

| t <sub>LPM_ENTRY</sub>       | Time to enter LPM state                                      |                                                                                   |                        |                           | 200  |                           | μs    |

| t <sub>WAKE</sub>            | I <sub>EXIT_LPM_MAN</sub> detection time                     |                                                                                   |                        |                           | 5    |                           | μs    |

| t <sub>SLEW</sub>            | Time to slew on the main FET after I <sub>EXIT_LPM_MAN</sub> |                                                                                   |                        |                           | 200  |                           | μs    |

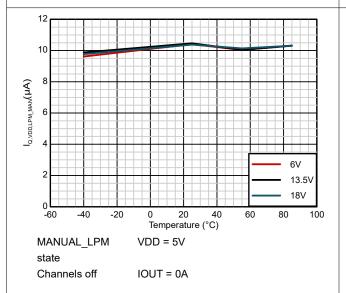

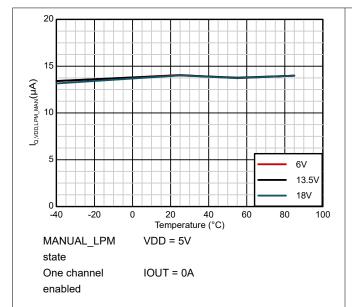

|                              |                                                              |                                                                                   | both channels OFF      |                           | 9    | 18                        | μA    |

| I <sub>Q,VDD,LPM_MAN</sub>   | VDD quiescent current in MANUAL LPM                          | $V_{DD} = 5.0V, I_{OUTx} = 0A,$<br>$T_{J} = -40^{\circ}C \text{ to } 85^{\circ}C$ | one channel ON         |                           | 12.3 | 21.6                      | μA    |

|                              |                                                              | .5 .6 6 66 6                                                                      | both channels ON       |                           | 15.6 | 23                        | μA    |

|                              |                                                              |                                                                                   | both channels OFF      |                           | 9    | 18                        | μA    |

| I <sub>Q,VDD,LPM_</sub> AUTO | VDD quiescent current in AUTO LPM                            | $V_{DD} = 5.0V$ , $I_{OUTx} = 0A$ ,<br>$T_{.1} = -40$ °C to 85°C                  | one channel ON         |                           | 12.3 | 21.6                      | μA    |

|                              | NOTO_ET W                                                    | 11 40 0 10 00 0                                                                   | both channels ON       |                           | 15.6 | 23                        | μΑ    |

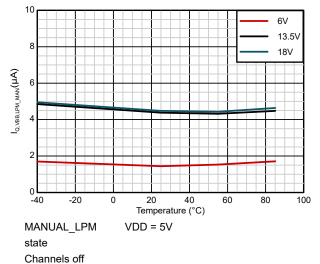

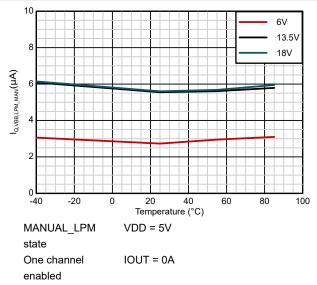

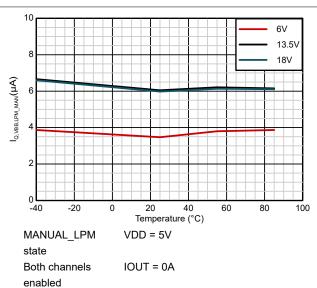

|                              |                                                              |                                                                                   | both channels OFF      |                           | 3.72 | 7                         | μA    |

| I <sub>Q,VBB,LPM_MAN</sub>   | VBB quiescent current in MANUAL_LPM                          | $V_{DD} = 5.0V, I_{OUTx} = 0A,$<br>$T_{J} = -40^{\circ}C \text{ to } 85^{\circ}C$ | one channel ON         |                           | 5.1  | 9.1                       | μA    |

|                              | W/WO/LE_EFW                                                  | 17 40 0 10 00 0                                                                   | both channels ON       |                           | 6.42 | 9.5                       | μA    |

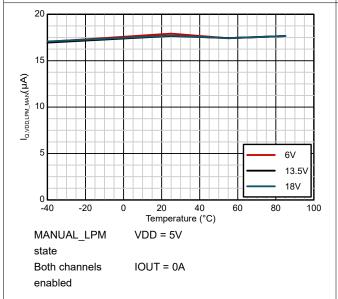

|                              |                                                              |                                                                                   | both channels OFF      |                           | 10.4 | 15.5                      | μA    |

| I <sub>Q,VBB,LPM_AUTO</sub>  | VBB quiescent current in AUTO_LPM                            | $V_{DD} = 5.0V$ , $I_{OUTx} = 0A$ ,<br>$T_{J} = -40$ °C to 85°C                   | one channel ON         |                           | 11   | 15.8                      | μA    |

|                              | AOTO_LI WI                                                   | 11 = -40 0 10 03 0                                                                | both channels ON       |                           | 11.6 | 16.1                      | μA    |

| DIGITAL INPUT                | PIN CHARACTERISTICS                                          |                                                                                   |                        |                           |      |                           |       |

| V <sub>IH, SPI</sub>         | Input voltage high-level (SCLK, SDI, CSN)                    | 3.0V ≤ VDD ≤ 5.5V                                                                 |                        | 0.7 ×<br>V <sub>VDD</sub> |      |                           | V     |

| V <sub>IL, SPI</sub>         | Input voltage low-level (SCLK, SDI, CSN)                     | 3.0V ≤ VDD ≤ 5.5V                                                                 |                        |                           | ,    | 0.3 ×<br>V <sub>VDD</sub> | V     |

| R <sub>PD,SCLK</sub>         | SCLK Internal pulldown resistor                              |                                                                                   |                        | 1.90                      | 2    | 2.16                      | МΩ    |

| I <sub>IH, SCLK</sub>        | Input current high-level                                     | SCLK V <sub>DI</sub> = 5V                                                         | V <sub>SCLK</sub> = 5V |                           | 2.5  |                           | μA    |

| R <sub>PD,SDI</sub>          | SDI Internal pulldown resistor                               |                                                                                   |                        | 1.90                      | 2    | 2.16                      | МΩ    |

| I <sub>IH, SDI</sub>         | Input current high-level                                     | SDI                                                                               | V <sub>SDI</sub> = 5V  |                           | 2.5  |                           | μA    |

| R <sub>PU,CSN</sub>          | CSN Internal pullup resistor                                 |                                                                                   |                        | 85                        | 90   | 96                        | kΩ    |

| V <sub>IH,DI</sub>           | input voltage high-level                                     |                                                                                   |                        | 1.65                      |      |                           | V     |

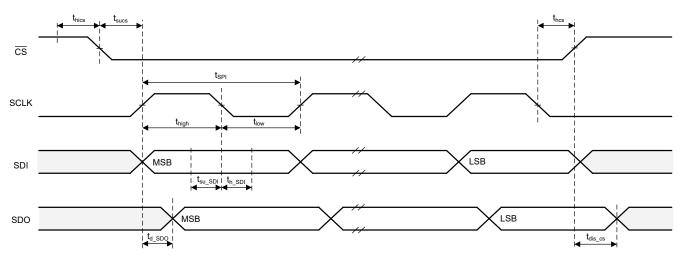

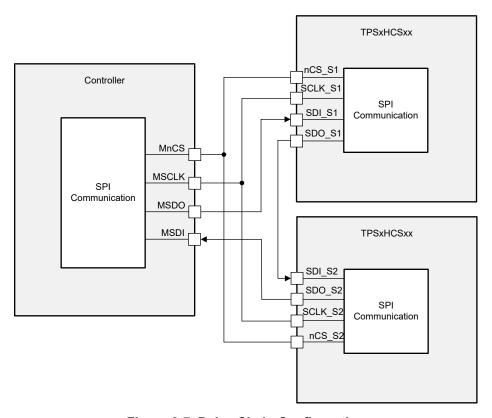

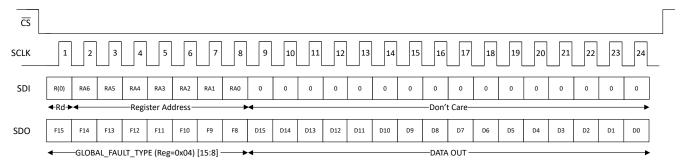

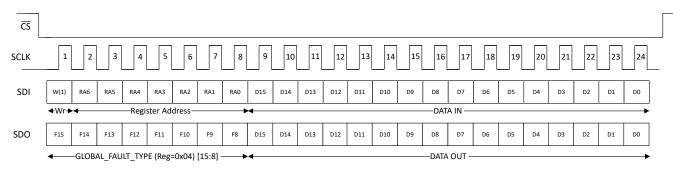

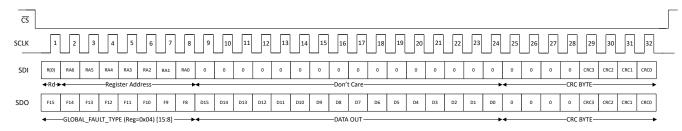

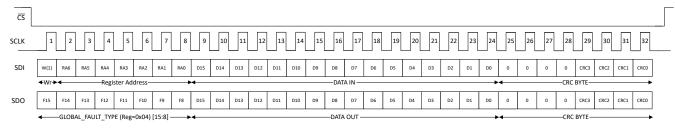

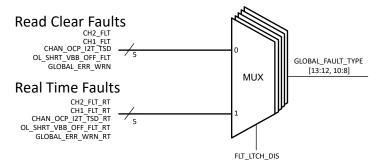

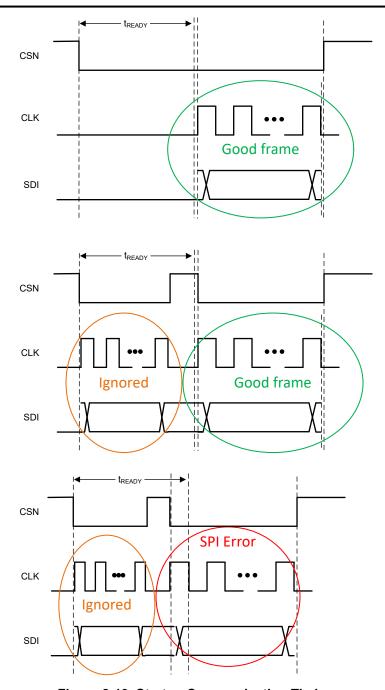

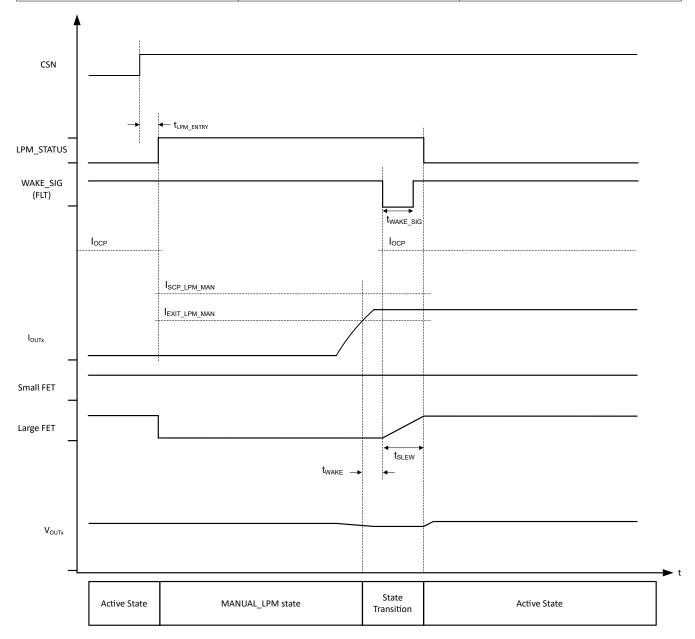

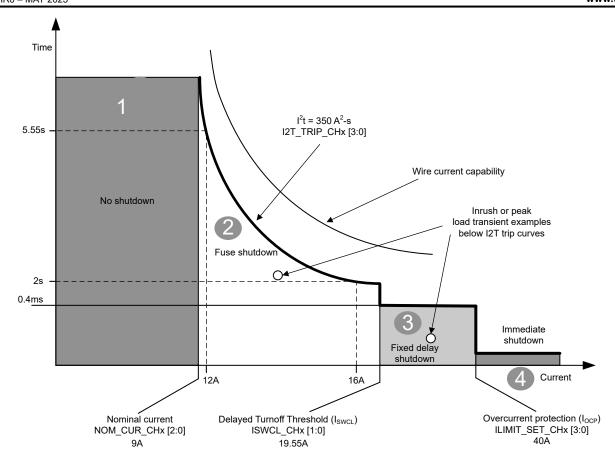

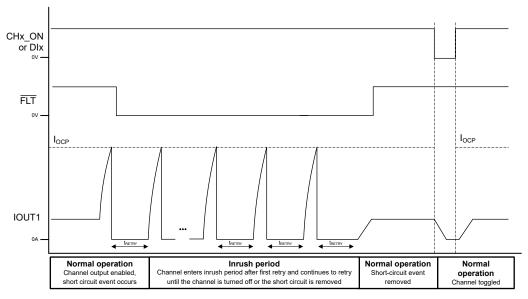

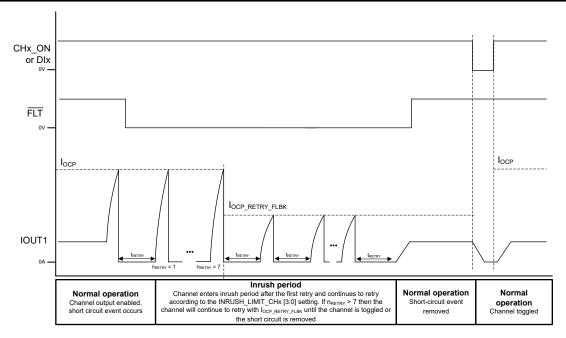

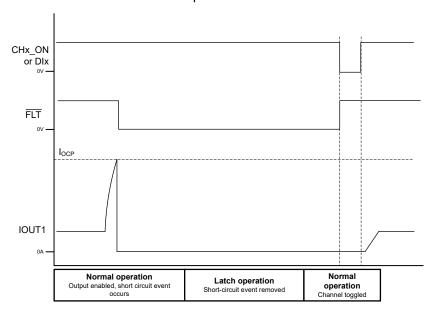

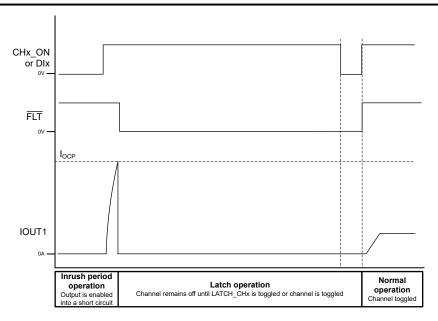

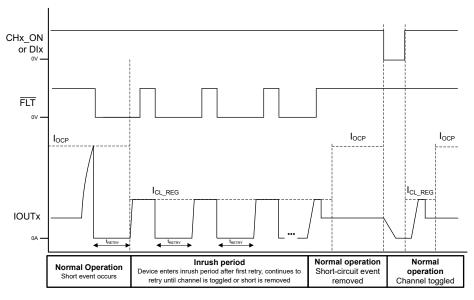

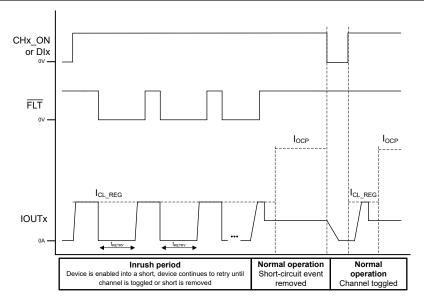

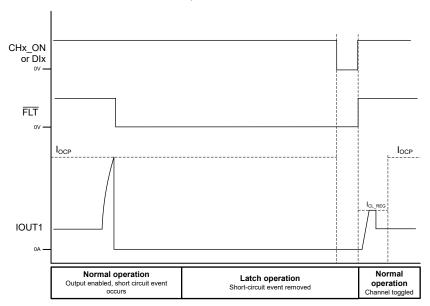

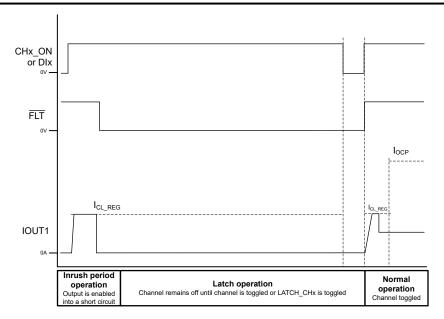

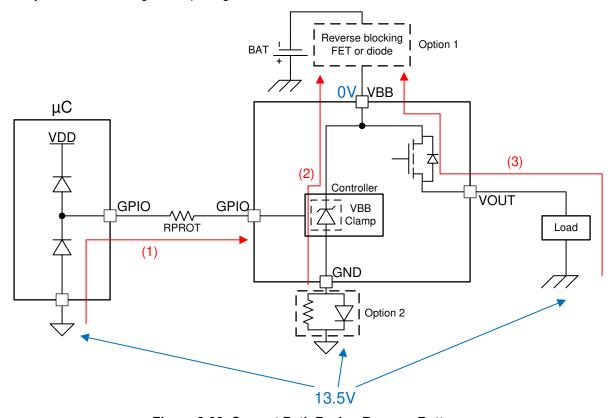

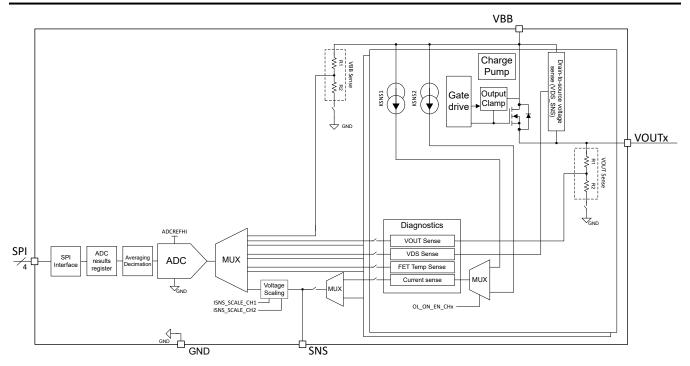

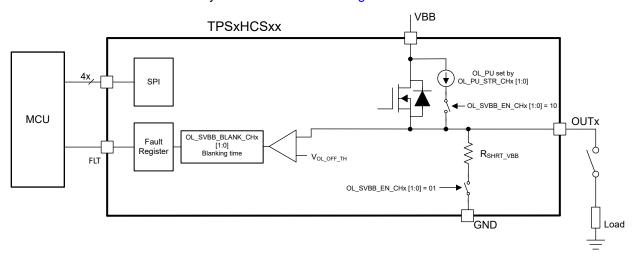

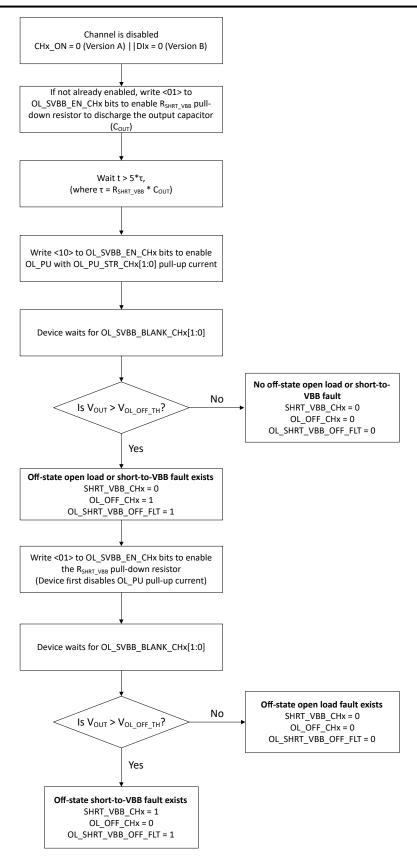

| V <sub>IL,DI</sub>           | Input voltage low-level                                      |                                                                                   |                        |                           |      | 0.8                       | V     |