# TMS320VC5503 Fixed-Point Digital Signal Processor

# Data Manual

Literature Number: SPRS245J April 2004 – Revised January 2008

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### **REVISION HISTORY**

This revision history highlights the technical changes made to SPRS245I to generate SPRS245J.

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                            |  |  |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 18             | Table 2–3, Signal Descriptions (Continued):  – Updated/changed D[15:0] <b>FUNCTION</b> description from " The data bus keepers are <b>disabled</b> at reset," to " The data bus keepers are <b>enabled</b> at reset,". |  |  |  |  |  |

## **Contents**

| Se | ection |            |                                                                       | Pa |

|----|--------|------------|-----------------------------------------------------------------------|----|

| 1  | TMS3   | 20VC5503   | Features                                                              |    |

| 2  | Introd | uction     |                                                                       |    |

|    | 2.1    | Descripti  | on                                                                    |    |

|    | 2.2    |            | gnments                                                               |    |

|    |        | 2.2.1      | Terminal Assignments for the GHH Package                              |    |

|    |        | 2.2.2      | Pin Assignments for the PGE Package                                   |    |

|    | 2.3    | Signal De  | escriptions                                                           |    |

| 3  | Eunot  | ional Ova  | rview                                                                 |    |

| 3  |        |            |                                                                       |    |

|    | 3.1    | -          | On Chin Dual Access DAM (DADAM)                                       |    |

|    |        | 3.1.1      | On-Chip Dual-Access RAM (DARAM)                                       |    |

|    |        | 3.1.2      | On-Chip Read-Only Memory (ROM)                                        |    |

|    |        | 3.1.3      | Memory Maps                                                           |    |

|    | 0.0    | 3.1.4      | Boot Configuration                                                    |    |

|    | 3.2    |            | als                                                                   |    |

|    | 3.3    |            | emory Access (DMA) Controller                                         |    |

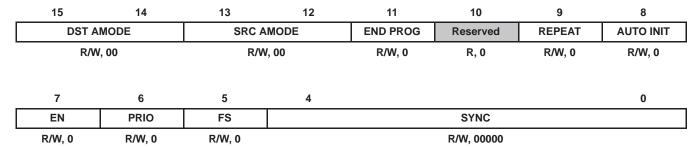

|    |        | 3.3.1      | DMA Channel Control Register (DMA_CCR)                                |    |

|    | 3.4    |            | face                                                                  |    |

|    | 3.5    | _          | able External Buses                                                   |    |

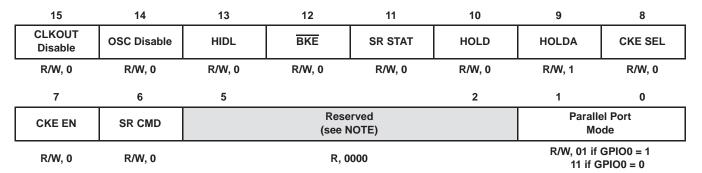

|    |        | 3.5.1      | External Bus Selection Register (EBSR)                                |    |

|    |        | 3.5.2      | Parallel Port                                                         |    |

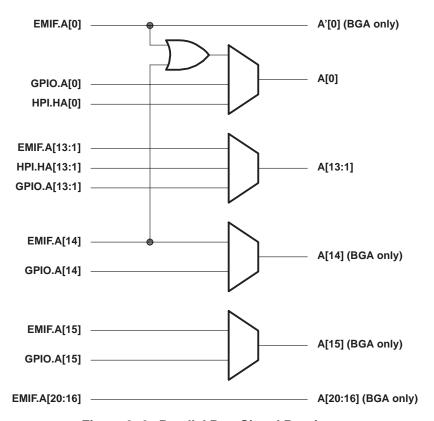

|    |        | 3.5.3      | Parallel Port Signal Routing                                          |    |

|    | 3.6    | General-   | Purpose Input/Output (GPIO) Ports                                     |    |

|    |        | 3.6.1      | Dedicated General-Purpose I/O                                         |    |

|    |        | 3.6.2      | Address Bus General-Purpose I/O                                       |    |

|    |        | 3.6.3      | EHPI General-Purpose I/O                                              |    |

|    | 3.7    | System F   | Register                                                              |    |

|    | 3.8    | Memory-    | -Mapped Registers                                                     |    |

|    | 3.9    | Periphera  | al Register Description                                               |    |

|    | 3.10   | Interrupts | s                                                                     |    |

|    |        | 3.10.1     | IFR and IER Registers                                                 |    |

|    |        | 3.10.2     | Interrupt Timing                                                      |    |

|    |        | 3.10.3     | Waking Up From IDLE Condition                                         |    |

|    |        | 3.10.4     | Idling Clock Domain When External Parallel Bus Operating in EHPI Mode |    |

|    |        |            |                                                                       |    |

| 4  |        |            |                                                                       |    |

|    | 4.1    |            | Concerning JTAG (IEEE 1149.1) Boundary Scan Test Capability           |    |

|    |        | 4.1.1      | Initialization Requirements for Boundary Scan Test                    |    |

|    |        | 4.1.2      | Boundary Scan Description Language (BSDL) Model                       |    |

|    | 4.2    |            | ntation Support                                                       |    |

|    | 4.3    |            | nd Development-Support Tool Nomenclature                              |    |

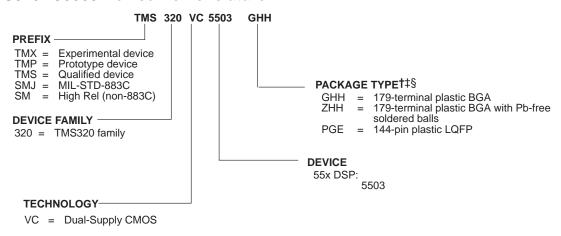

|    | 4.4    | TMS320     | VC5503 Device Nomenclature                                            |    |

| Se | ection   |           |                                                                                                                      | Page |

|----|----------|-----------|----------------------------------------------------------------------------------------------------------------------|------|

| 5  | Electri  | cal Speci | fications                                                                                                            | 65   |

|    | 5.1      | -         | Maximum Ratings                                                                                                      | 65   |

|    | 5.2      |           | nended Operating Conditions                                                                                          | 66   |

|    | 0        | 5.2.1     | Recommended Operating Conditions for CV <sub>DD</sub> = 1.2 V (108 MHz)                                              | 66   |

|    |          | 5.2.2     | Recommended Operating Conditions for CV <sub>DD</sub> = 1.35 V (144 MHz)                                             | 67   |

|    |          | 5.2.3     | Recommended Operating Conditions for CV <sub>DD</sub> = 1.6 V (200 MHz)                                              | 68   |

|    | 5.3      | -         | I Characteristics                                                                                                    | 69   |

|    | 0.0      | 5.3.1     | Electrical Characteristics Over Recommended Operating Case Temperature Range for CV <sub>DD</sub> = 1.2 V (108 MHz)  | 69   |

|    |          | 5.3.2     | Electrical Characteristics Over Recommended Operating Case Temperature Range for CV <sub>DD</sub> = 1.35 V (144 MHz) | 70   |

|    |          | 5.3.3     | Electrical Characteristics Over Recommended Operating Case Temperature Range for CV <sub>DD</sub> = 1.6 V (200 MHz)  | 71   |

|    | 5.4      | ESD Per   | formance                                                                                                             | 72   |

|    | 5.5      |           | arameter Symbology                                                                                                   | 72   |

|    | 5.6      | ŭ         | otions                                                                                                               | 73   |

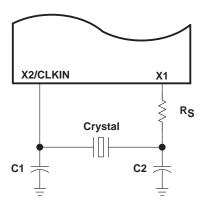

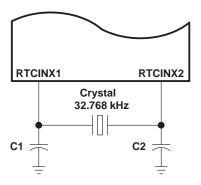

|    |          | 5.6.1     | Internal System Oscillator With External Crystal                                                                     | 73   |

|    |          | 5.6.2     | Layout Considerations                                                                                                | 74   |

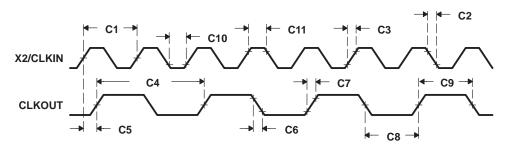

|    |          | 5.6.3     | Clock Generation in Bypass Mode (DPLL Disabled)                                                                      | 75   |

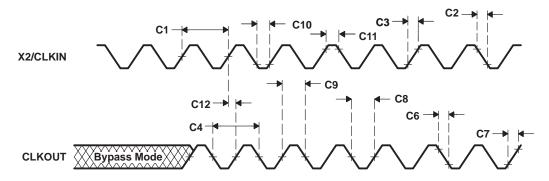

|    |          | 5.6.4     | Clock Generation in Lock Mode (DPLL Synthesis Enabled)                                                               | 76   |

|    |          | 5.6.5     | Real-Time Clock Oscillator With External Crystal                                                                     | 77   |

|    | 5.7      |           | Interface Timings                                                                                                    | 78   |

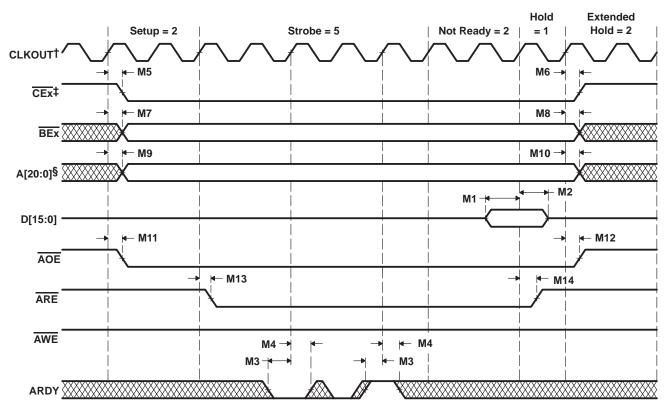

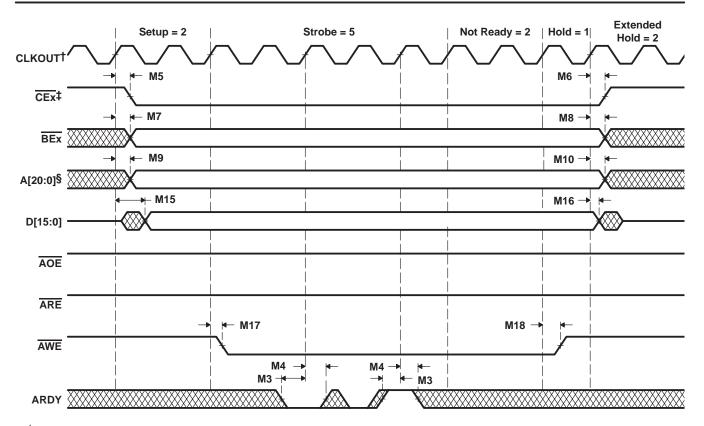

|    |          | 5.7.1     | Asynchronous Memory Timings                                                                                          | 78   |

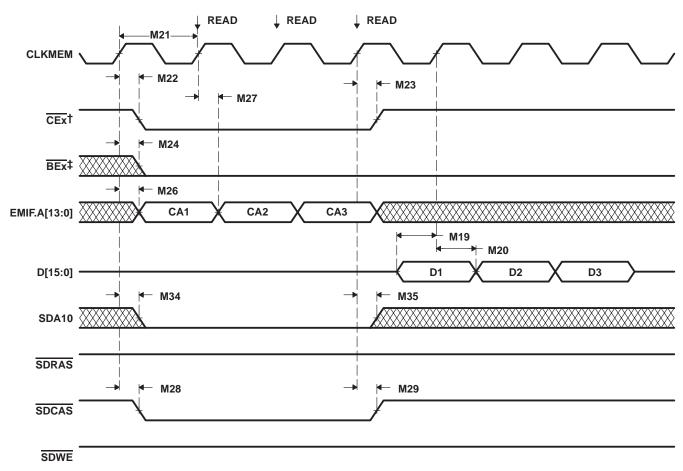

|    |          | 5.7.2     | Synchronous DRAM (SDRAM) Timings                                                                                     | 81   |

|    | 5.8      |           | mings                                                                                                                | 89   |

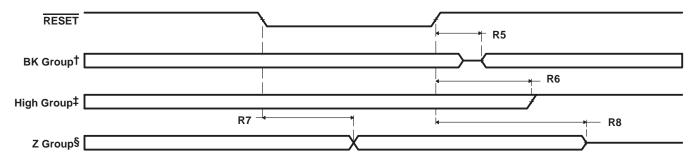

|    |          | 5.8.1     | Power-Up Reset (On-Chip Oscillator Active)                                                                           | 89   |

|    |          | 5.8.2     | Power-Up Reset (On-Chip Oscillator Inactive)                                                                         | 90   |

|    |          | 5.8.3     | Warm Reset                                                                                                           | 91   |

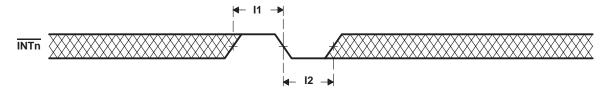

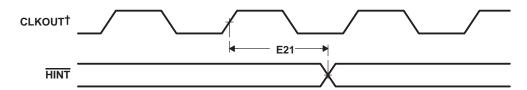

|    | 5.9      | External  | Interrupt Timings                                                                                                    | 92   |

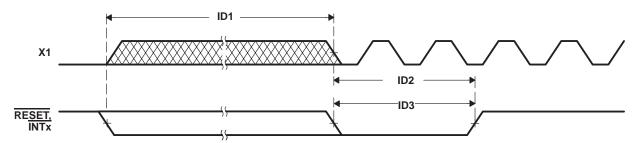

|    | 5.10     |           | From IDLE                                                                                                            | 92   |

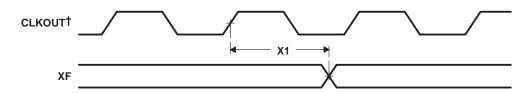

|    | 5.11     |           | ngs                                                                                                                  | 93   |

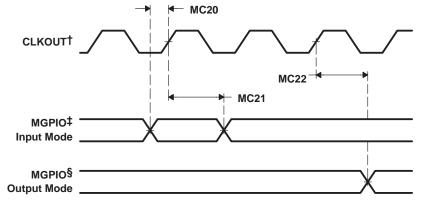

|    | 5.12     |           | Purpose Input/Output (GPIOx) Timings                                                                                 | 94   |

|    | 5.13     |           | JT Timings (Timer0 Only)                                                                                             | 95   |

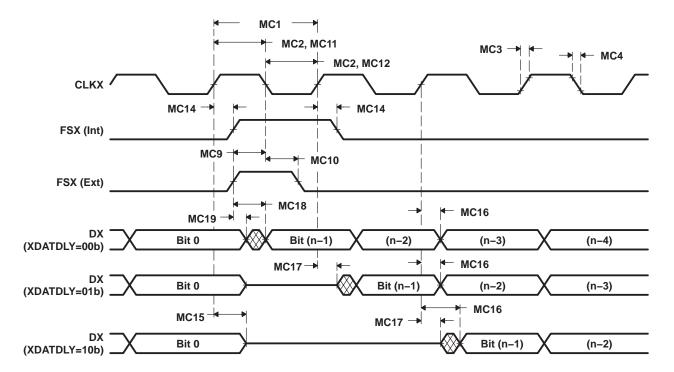

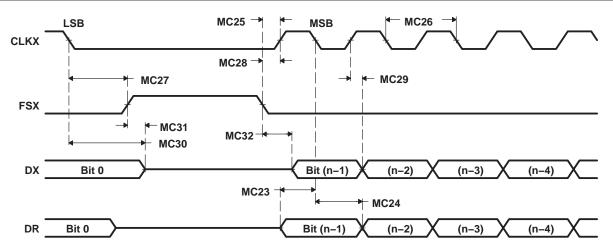

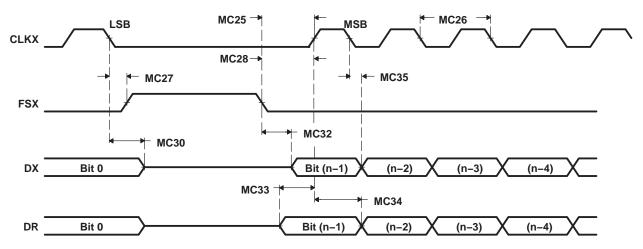

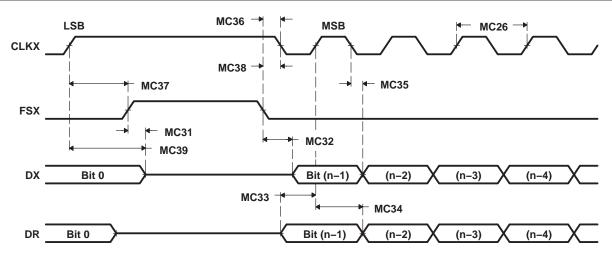

|    | 5.14     |           | nnel Buffered Serial Port (McBSP) Timings                                                                            | 96   |

|    |          | 5.14.1    | McBSP0 Timings                                                                                                       | 96   |

|    |          | 5.14.2    | McBSP1 and McBSP2 Timings                                                                                            | 98   |

|    |          | 5.14.3    | McBSP as SPI Master or Slave Timings                                                                                 | 101  |

|    |          | 5.14.4    | McBSP General-Purpose I/O Timings                                                                                    | 109  |

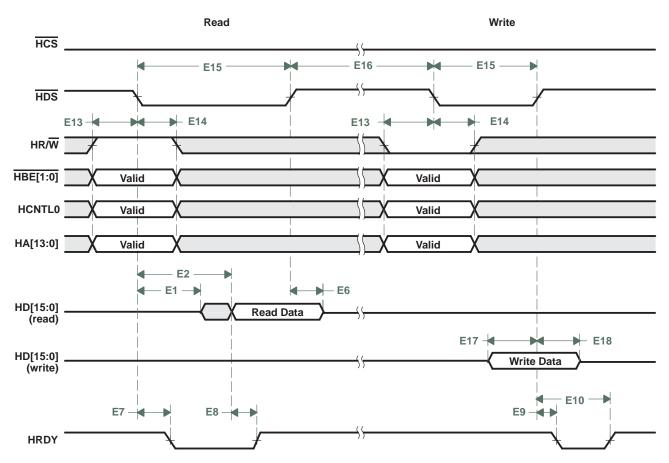

|    | 5.15     |           | ed Host-Port Interface (EHPI) Timings                                                                                | 110  |

|    | 5.16     |           | ngs                                                                                                                  | 116  |

| •  | NA c - L | wind Det  |                                                                                                                      | 444  |

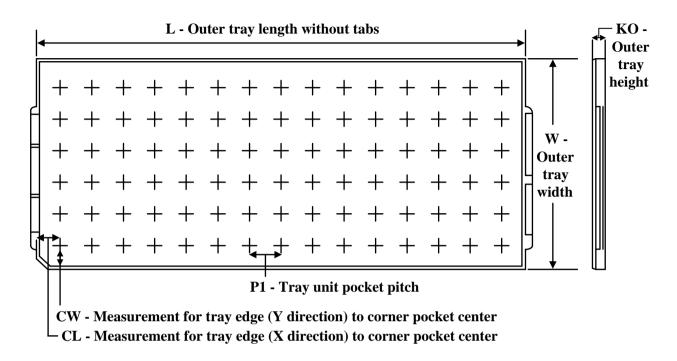

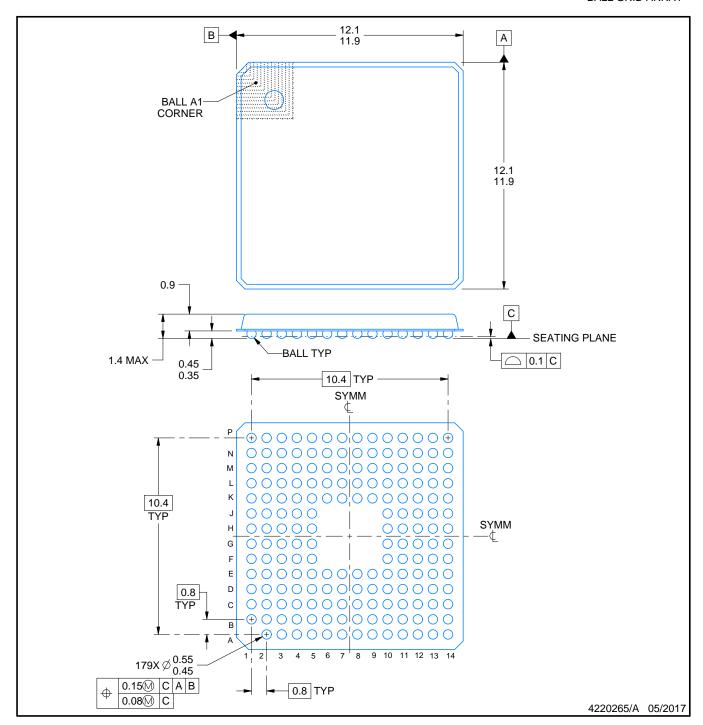

| 6  |          |           | a                                                                                                                    | 119  |

|    | 6.1      | _         | Thermal Resistance Characteristics                                                                                   | 119  |

|    | 6.2      | Packagin  | ng Information                                                                                                       | 119  |

# **List of Figures**

| Figure |                                                       | Page |

|--------|-------------------------------------------------------|------|

| 2–1    | 179-Terminal GHH Ball Grid Array (Bottom View)        | 13   |

| 2–2    | 144-Pin PGE Low-Profile Quad Flatpack (Top View)      | 15   |

| 3–1    | Block Diagram of the TMS320VC5503                     | 27   |

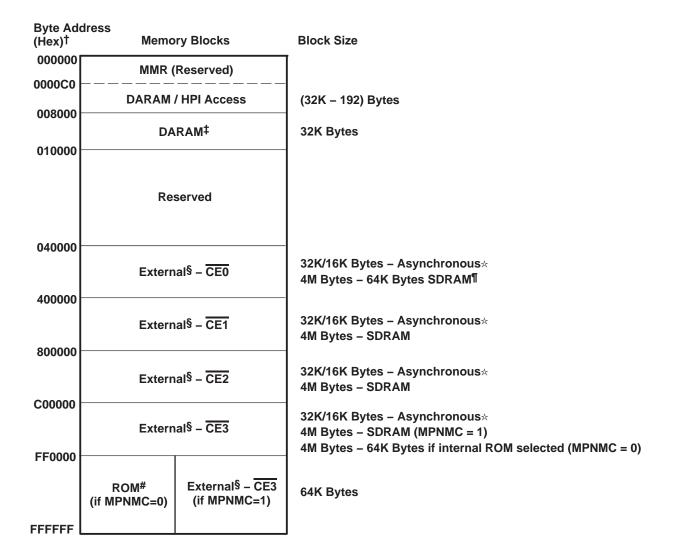

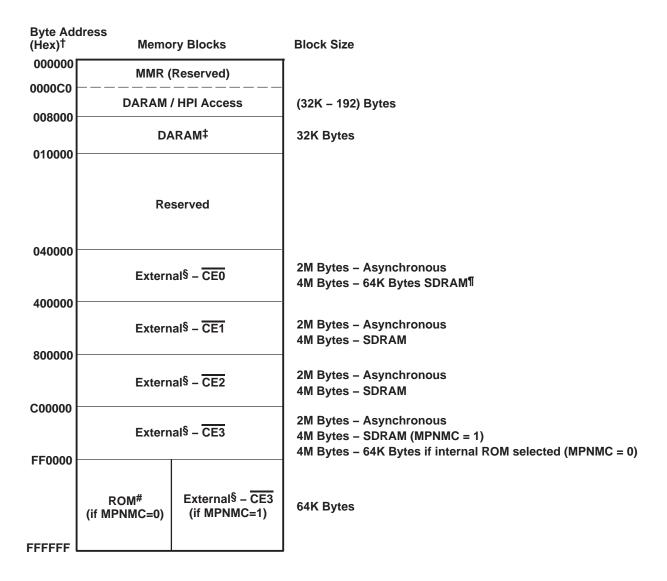

| 3–2    | TMS320VC5503 Memory Map (PGE Package)                 | 29   |

| 3–3    | TMS320VC5503 Memory Map (GHH Package)                 | 30   |

| 3–4    | DMA_CCR Bit Locations                                 | 33   |

| 3–5    | External Bus Selection Register                       | 35   |

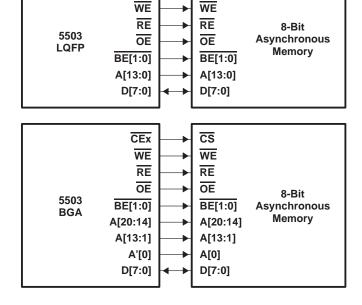

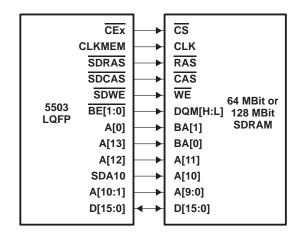

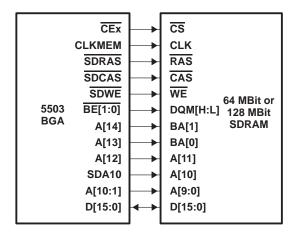

| 3–6    | Parallel Port Signal Routing                          | 38   |

| 3–7    | Parallel Port (EMIF) Signal Interface                 | 39   |

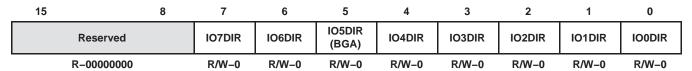

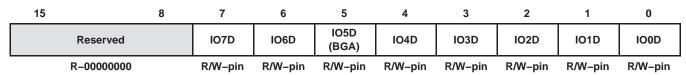

| 3–8    | I/O Direction Register (IODIR) Bit Layout             | 40   |

| 3–9    | I/O Data Register (IODATA) Bit Layout                 | 41   |

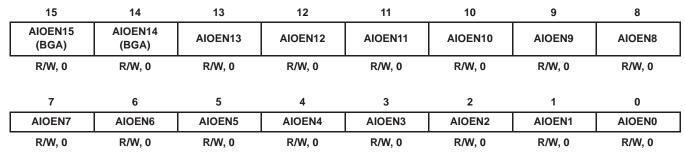

| 3–10   | Address/GPIO Enable Register (AGPIOEN) Bit Layout     | 41   |

| 3–11   | Address/GPIO Direction Register (AGPIODIR) Bit Layout | 42   |

| 3–12   | Address/GPIO Data Register (AGPIODATA) Bit Layout     | 42   |

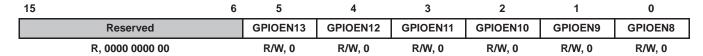

| 3–13   | EHPI GPIO Enable Register (EHPIGPIOEN) Bit Layout     | 43   |

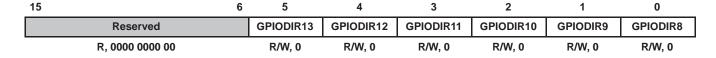

| 3–14   | EHPI GPIO Direction Register (EHPIGPIODIR) Bit Layout | 43   |

| 3–15   | EHPI GPIO Data Register (EHPIGPIODATA) Bit Layout     | 44   |

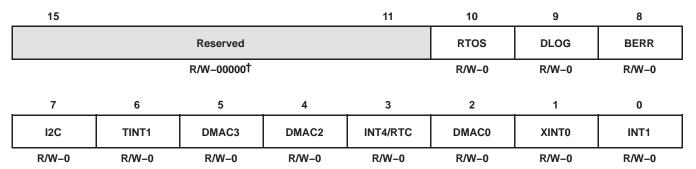

| 3–16   | System Register Bit Locations                         | 45   |

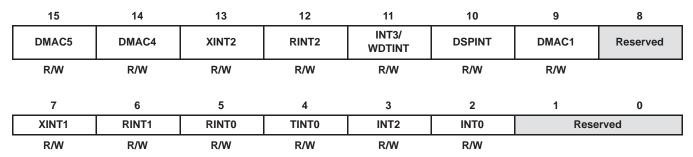

| 3–17   | IFR0 and IER0 Bit Locations                           | 60   |

| 3–18   | IFR1 and IER1 Bit Locations                           | 61   |

| 4–1    | Device Nomenclature for the TMS320VC5503              | 64   |

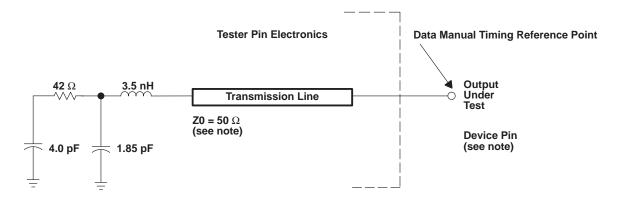

| 5–1    | 3.3-V Test Load Circuit                               | 72   |

| 5–2    | Internal System Oscillator With External Crystal      | 73   |

| 5-3    | Bypass Mode Clock Timings                             | 75   |

| 5-4    | External Multiply-by-N Clock Timings                  | 77   |

| 5-5    | Real-Time Clock Oscillator With External Crystal      | 77   |

| 5–6    | Asynchronous Memory Read Timings                      | 79   |

| 5–7    | Asynchronous Memory Write Timings                     | 80   |

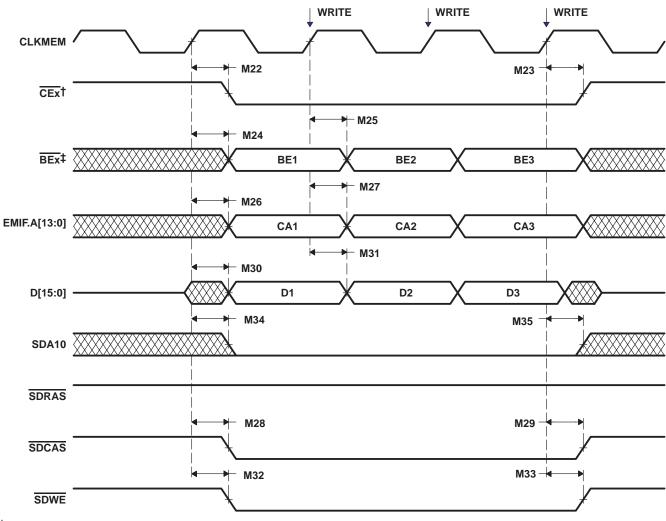

| 5–8    | Three SDRAM Read Commands                             | 82   |

| 5-9    | Three SDRAM WRT Commands                              | 83   |

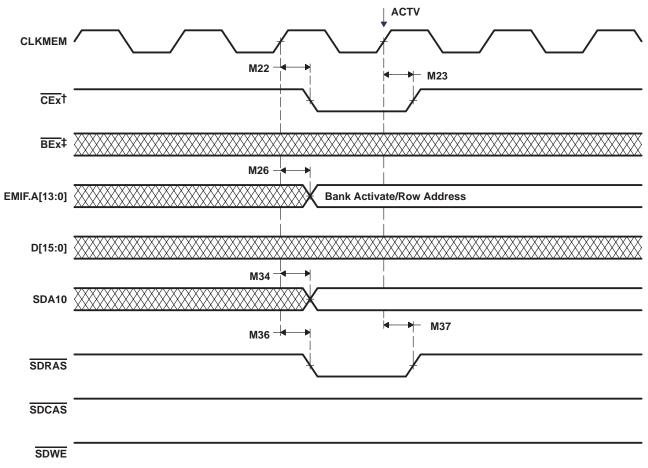

| 5–10   | SDRAM ACTV Command                                    | 84   |

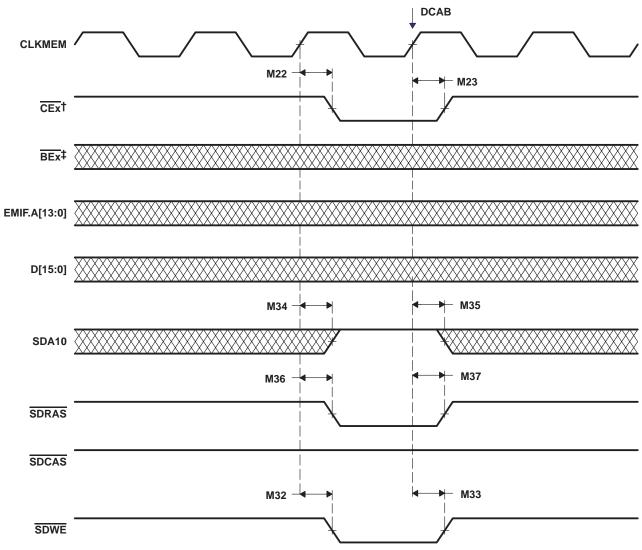

| 5–11   | SDRAM DCAB Command                                    | 85   |

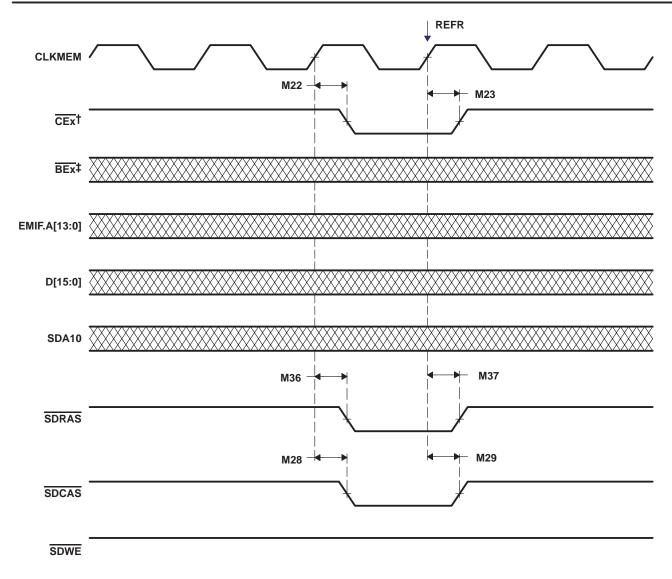

| 5–12   | SDRAM REFR Command                                    | 86   |

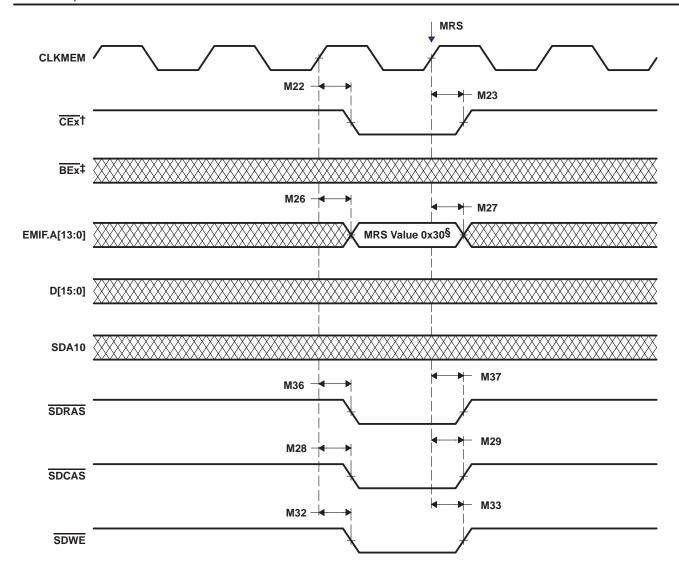

| 5–13   | SDRAM MRS Command                                     | 87   |

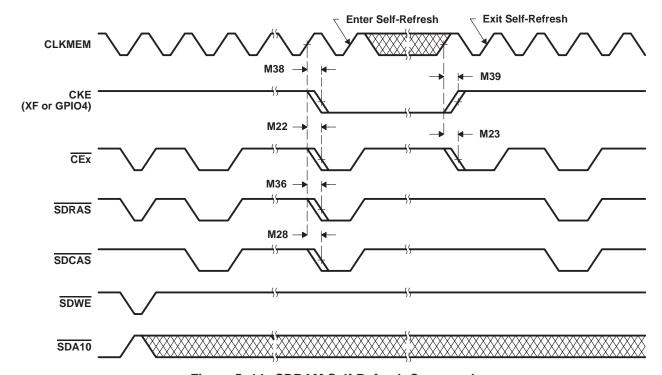

| 5–14   | SDRAM Self-Refresh Command                            | 88   |

| Figure |                                                                         | Page |

|--------|-------------------------------------------------------------------------|------|

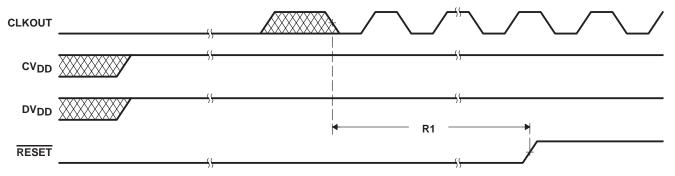

| 5–15   | Power-Up Reset (On-Chip Oscillator Active) Timings                      | 89   |

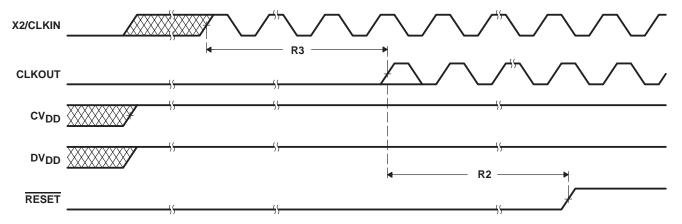

| 5–16   | Power-Up Reset (On-Chip Oscillator Inactive) Timings                    | 90   |

| 5–17   | Reset Timings                                                           | 91   |

| 5–18   | External Interrupt Timings                                              | 92   |

| 5–19   | Wake-Up From IDLE Timings                                               | 92   |

| 5-20   | XF Timings                                                              | 93   |

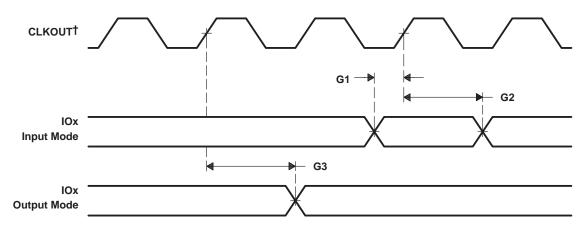

| 5–21   | General-Purpose Input/Output (IOx) Signal Timings                       | 94   |

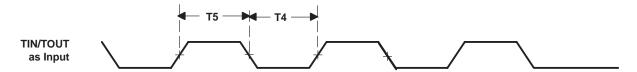

| 5–22   | TIN/TOUT Timings When Configured as Inputs                              | 95   |

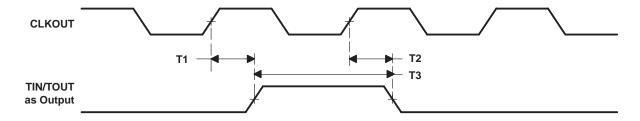

| 5–23   | TIN/TOUT Timings When Configured as Outputs                             | 95   |

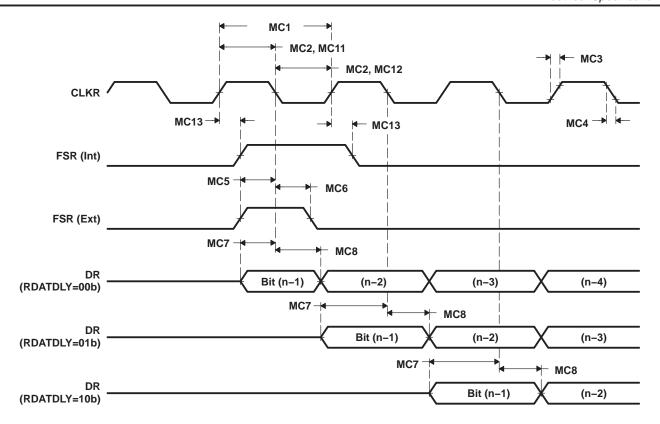

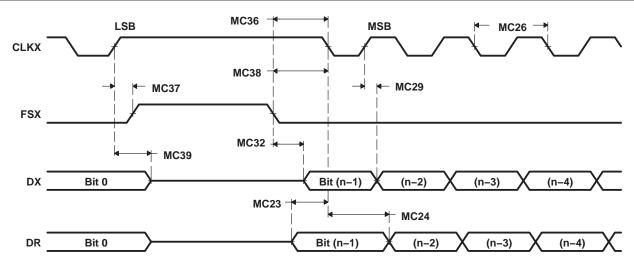

| 5–24   | McBSP Receive Timings                                                   | 100  |

| 5–25   | McBSP Transmit Timings                                                  | 100  |

| 5-26   | McBSP Timings as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0           | 102  |

| 5–27   | McBSP Timings as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0           | 104  |

| 5–28   | McBSP Timings as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1           | 106  |

| 5–29   | McBSP Timings as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1           | 108  |

| 5-30   | McBSP General-Purpose I/O Timings                                       | 109  |

| 5–31   | HINT Timings                                                            | 111  |

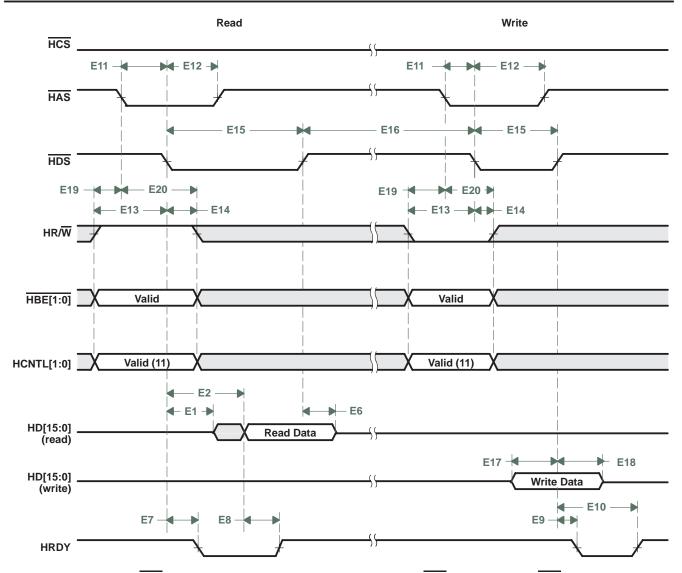

| 5-32   | EHPI Nonmultiplexed Read/Write Timings                                  | 111  |

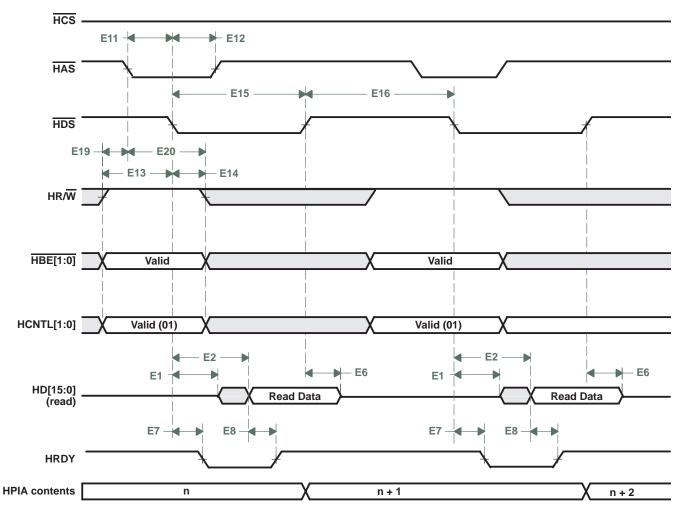

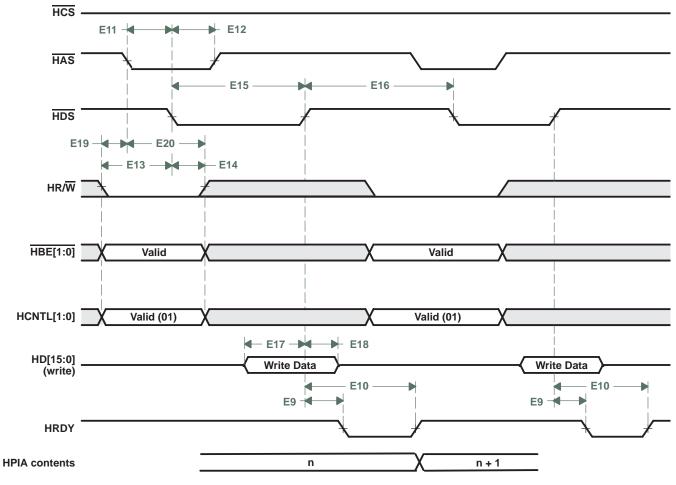

| 5-33   | EHPI Multiplexed Memory (HPID) Read/Write Timings Without Autoincrement | 112  |

| 5-34   | EHPI Multiplexed Memory (HPID) Read Timings With Autoincrement          | 113  |

| 5-35   | EHPI Multiplexed Memory (HPID) Write Timings With Autoincrement         | 114  |

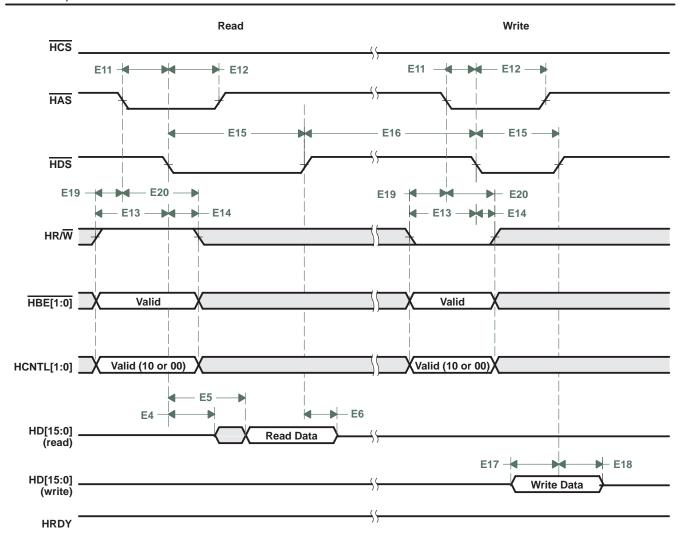

| 5-36   | EHPI Multiplexed Register Read/Write Timings                            | 115  |

| 5–37   | I <sup>2</sup> C Receive Timings                                        | 117  |

| 5–38   | I <sup>2</sup> C Transmit Timings                                       | 118  |

# **List of Tables**

| Table |                                                          | Page |

|-------|----------------------------------------------------------|------|

| 2–1   | Pin Assignments for the GHH Package                      | 14   |

| 2–2   | Pin Assignments for the PGE Package                      | 16   |

| 2–3   | Signal Descriptions                                      | 17   |

| 3–1   | DARAM Blocks                                             | 28   |

| 3–2   | Boot Configuration Summary                               | 31   |

| 3–3   | Synchronization Control Function                         | 33   |

| 3–4   | External Bus Selection Register Bit Field Description    | 35   |

| 3–5   | TMS320VC5503 Parallel Port Signal Routing                | 37   |

| 3–6   | I/O Direction Register (IODIR) Bit Functions             | 40   |

| 3–7   | I/O Data Register (IODATA) Bit Functions                 | 41   |

| 3–8   | Address/GPIO Enable Register (AGPIOEN) Bit Functions     | 41   |

| 3–9   | Address/GPIO Direction Register (AGPIODIR) Bit Functions | 42   |

| 3–10  | Address/GPIO Data Register (AGPIODATA) Bit Functions     | 42   |

| 3–11  | EHPI GPIO Enable Register (EHPIGPIOEN) Bit Functions     | 43   |

| 3–12  | EHPI GPIO Direction Register (EHPIGPIODIR) Bit Functions | 43   |

| 3–13  | EHPI GPIO Data Register (EHPIGPIODATA) Bit Functions     | 44   |

| 3–14  | System Register Bit Fields                               | 45   |

| 3–15  | CPU Memory-Mapped Registers                              | 46   |

| 3–16  | Idle Control, Status, and System Registers               | 48   |

| 3–17  | External Memory Interface Registers                      | 48   |

| 3–18  | DMA Configuration Registers                              | 49   |

| 3–19  | Real-Time Clock Registers                                | 52   |

| 3-20  | Clock Generator                                          | 53   |

| 3–21  | Timers                                                   | 53   |

| 3–22  | Multichannel Serial Port #0                              | 54   |

| 3-23  | Multichannel Serial Port #1                              | 55   |

| 3-24  | Multichannel Serial Port #2                              | 56   |

| 3-25  | GPIO                                                     | 57   |

| 3–26  | Device Revision ID                                       | 57   |

| 3-27  | I <sup>2</sup> C Module Registers                        | 57   |

| 3–28  | Watchdog Timer Registers                                 | 58   |

| 3–29  | External Bus Selection Register                          | 58   |

| 3–30  | Interrupt Table                                          | 59   |

| 3–31  | IFR0 and IER0 Register Bit Fields                        | 60   |

| 3–32  | IFR1 and IER1 Register Bit Fields                        | 61   |

| 5–1   | Recommended Crystal Parameters                           | 73   |

| 5–2   | CLKIN Timing Requirements                                | 75   |

| 5–3   | CLKOUT Switching Characteristics                         | 75   |

| 5–4   | Multiply-By-N Clock Option Timing Requirements           | 76   |

| 5–5   | Multiply-By-N Clock Option Switching Characteristics     | 76   |

| 5–6   | Recommended RTC Crystal Parameters                       | 77   |

| 5–7   | Asynchronous Memory Cycle Timing Requirements            | 78   |

| 5–8   | Asynchronous Memory Cycle Switching Characteristics      | 78   |

|       |                                                          |      |

| Table |                                                                                  | Page |

|-------|----------------------------------------------------------------------------------|------|

| 5–9   | Synchronous DRAM Cycle Timing Requirements                                       | 81   |

| 5–10  | Synchronous DRAM Cycle Switching Characteristics                                 | 81   |

| 5–11  | Power-Up Reset (On-Chip Oscillator Active) Timing Requirements                   | 89   |

| 5–12  | Power-Up Reset (On-Chip Oscillator Inactive) Timing Requirements                 | 90   |

| 5–13  | Power-Up Reset (On-Chip Oscillator Inactive) Switching Characteristics           | 90   |

| 5–14  | Reset Timing Requirements                                                        | 91   |

| 5–15  | Reset Switching Characteristics                                                  | 91   |

| 5–16  | External Interrupt Timing Requirements                                           | 92   |

| 5–17  | Wake-Up From IDLE Switching Characteristics                                      | 92   |

| 5–18  | XF Switching Characteristics                                                     | 93   |

| 5–19  | GPIO Pins Configured as Inputs Timing Requirements                               | 94   |

| 5-20  | GPIO Pins Configured as Outputs Switching Characteristics                        | 94   |

| 5–21  | TIN/TOUT Pins Configured as Inputs Timing Requirements                           | 95   |

| 5–22  | TIN/TOUT Pins Configured as Outputs Switching Characteristics                    | 95   |

| 5-23  | McBSP0 Timing Requirements                                                       | 96   |

| 5-24  | McBSP0 Switching Characteristics                                                 | 97   |

| 5-25  | McBSP1 and McBSP2 Timing Requirements                                            | 98   |

| 5-26  | McBSP1 and McBSP2 Switching Characteristics                                      | 99   |

| 5–27  | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0)       | 101  |

| 5–28  | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0) | 101  |

| 5–29  | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 0)       | 103  |

| 5-30  | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 0) | 103  |

| 5–31  | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1)       | 105  |

| 5-32  | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1) | 105  |

| 5-33  | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1)       | 107  |

| 5-34  | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1) | 107  |

| 5-35  | McBSP General-Purpose I/O Timing Requirements                                    | 109  |

| 5-36  | McBSP General-Purpose I/O Switching Characteristics                              | 109  |

| 5-37  | EHPI Timing Requirements                                                         | 110  |

| 5-38  | EHPI Switching Characteristics                                                   | 110  |

| 5-39  | I <sup>2</sup> C Signals (SDA and SCL) Timing Requirements                       | 116  |

| 5–40  | I <sup>2</sup> C Signals (SDA and SCL) Switching Characteristics                 | 118  |

| 6–1   | Thermal Resistance Characteristics (Ambient)                                     | 119  |

| 6 2   | Thormal Posistance Characteristics (Case)                                        | 110  |

#### 1 TMS320VC5503 Features

- High-Performance, Low-Power, Fixed-Point TMS320C55x™ Digital Signal Processor

- 9.26-, 6.95-, 5-ns Instruction Cycle Time

- 108-, 144-, 200-MHz Clock Rate

- One/Two Instruction(s) Executed per Cycle

- Dual Multipliers [Up to 400 Million Multiply-Accumulates per Second (MMACS)]

- Two Arithmetic/Logic Units (ALUs)

- Three Internal Data/Operand Read Buses and Two Internal Data/Operand Write **Buses**

- 32K x 16-Bit On-Chip RAM, Composed of:

- 64K Bytes of Dual-Access RAM (DARAM) 8 Blocks of 4K × 16-Bit

- 64K Bytes of One-Wait-State On-Chip ROM (32K × 16-Bit)

- 8M × 16-Bit Maximum Addressable External **Memory Space (Synchronous DRAM)**

- **16-Bit External Parallel Bus Memory** Supporting Either:

- External Memory Interface (EMIF) With **GPIO Capabilities and Glueless Interface**

- Asynchronous Static RAM (SRAM)

- Asynchronous EPROM

- Synchronous DRAM (SDRAM)

- 16-Bit Parallel Enhanced Host-Port Interface (EHPI) With GPIO Capabilities

- **Programmable Low-Power Control of Six Device Functional Domains**

- **On-Chip Scan-Based Emulation Logic**

- **On-Chip Peripherals**

- Two 20-Bit Timers

- Watchdog Timer

- Six-Channel Direct Memory Access (DMA) Controller

- Three Multichannel Buffered Serial Ports (McBSPs)

- Programmable Phase-Locked Loop **Clock Generator**

- Seven (LQFP) or Eight (BGA) General-Purpose I/O (GPIO) Pins and a General-**Purpose Output Pin (XF)**

- Inter-Integrated Circuit (I<sup>2</sup>C) Multi-Master and Slave Interface

- Real-Time Clock (RTC) With Crystal Input, Separate Clock Domain, Separate **Power Supply**

- IEEE Std 1149.1<sup>†</sup> (JTAG) Boundary Scan Logic

- Packages:

- 144-Terminal Low-Profile Quad Flatpack (LQFP) (PGE Suffix)

- 179-Terminal MicroStar BGA™ (Ball Grid Array) (GHH and ZHH Suffixes)

SPRS245J

- 1.2-V Core (108 MHz), 2.7-V 3.6-V I/Os

- 1.35-V Core (144 MHz), 2.7-V 3.6-V I/Os

- 1.6-V Core (200 MHz), 2.7-V 3.6-V I/Os

#### 2 Introduction

This section describes the main features of the TMS320VC5503, lists the pin assignments, and describes the function of each pin. This data manual also provides a detailed description section, electrical specifications, parameter measurement information, and mechanical data about the available packaging.

**NOTE:** This data manual is designed to be used in conjunction with the *TMS320C55x*<sup>™</sup> *DSP Functional Overview* (literature number SPRU312), the *TMS320C55x DSP CPU Reference Guide* (literature number SPRU371), and the *TMS320C55x DSP Peripherals Overview Reference Guide* (literature number SPRU317).

## 2.1 Description

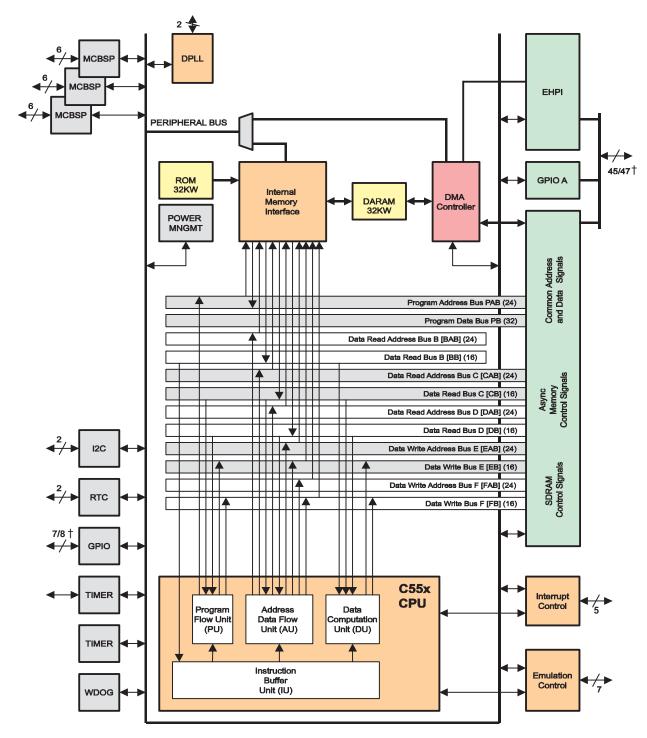

The TMS320VC5503 fixed-point digital signal processor (DSP) is based on the TMS320C55x DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on reduction in power dissipation. The CPU supports an internal bus structure that is composed of one program bus, three data read buses, two data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to three data reads and two data writes in a single cycle. In parallel, the DMA controller can perform up to two data transfers per cycle independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x DSP generation supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to AU and DU resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions.

The 64K bytes of on-chip memory on TMS320VC5503 is sufficient for many small hand-held appliances, portable personal appliances, gaming devices, and personal medical care appliances. Many of these appliances typically require 64K bytes or smaller amount of on-chip memory and need to operate in standby mode for more than 60% to 70% of the time. For applications that require more than 64K bytes of on-chip memory but less than 128K bytes of memory, Texas Instruments (TI) offers the TMS320VC5507 device, which is based on the TMS320C55x DSP core.

The general-purpose input and output functions provide sufficient pins for status, interrupts, and bit I/O for LCDs, keyboards, and media interfaces. The parallel interface operates in two modes, either as a slave to a microcontroller using the HPI port or as a parallel media interface using the asynchronous EMIF. Serial media is supported through three McBSPs.

The 5503 peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM. Additional peripherals include real-time clock, watchdog timer, and I<sup>2</sup>C multi-master and slave interface. Three full-duplex multichannel buffered serial ports (McBSPs) provide glueless interface to a variety of industry-standard serial devices, and multichannel communication with up to 128 separately enabled channels. The enhanced host-port interface (HPI) is a 16-bit parallel interface used to provide host processor access to 32K bytes of internal memory on the 5503. The HPI can be configured in either multiplexed or non-multiplexed mode to provide glueless interface to a wide variety of host processors. The DMA controller provides data movement for six independent channel contexts without CPU intervention, providing DMA throughput of up to two 16-bit words per cycle. Two general-purpose timers, up to eight dedicated general-purpose I/O (GPIO) pins, and digital phase-locked loop (DPLL) clock generation are also included.

C55x, eXpressDSP, Code Composer Studio, DSP/BIOS, RTDX, and XDS510 are trademarks of Texas Instruments.

The 5503 is supported by the industry's award-winning eXpressDSP™, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, Texas Instruments' algorithm standard, and the industry's largest third-party network. The Code Composer Studio IDE features code generation tools including a C Compiler and Visual Linker, simulator, RTDX™, XDS510™ emulation device drivers, and evaluation modules. The 5503 is also supported by the C55x DSP Library which features more than 50 foundational software kernels (FIR filters, IIR filters, FFTs, and various math functions) as well as chip and board support libraries.

#### 2.2 Pin Assignments

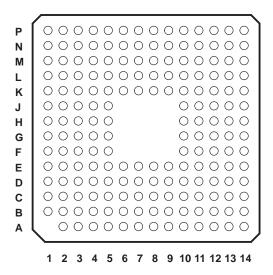

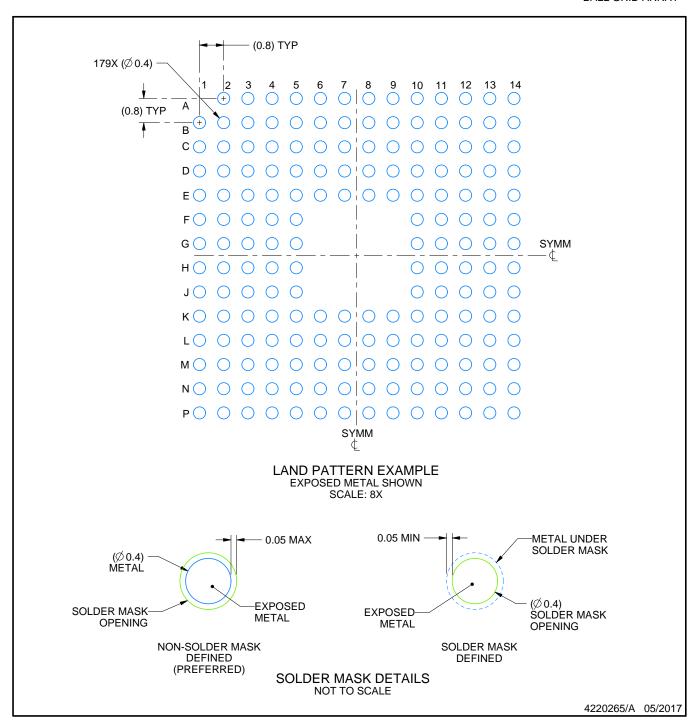

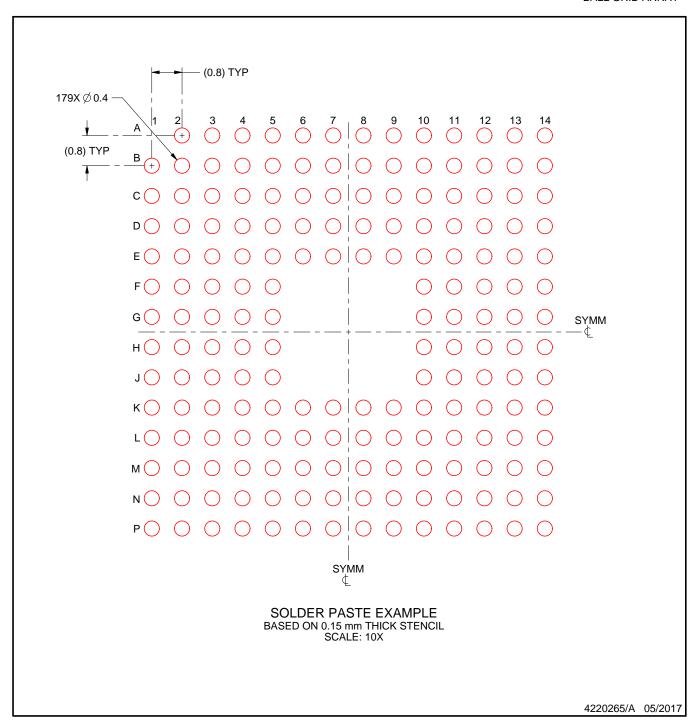

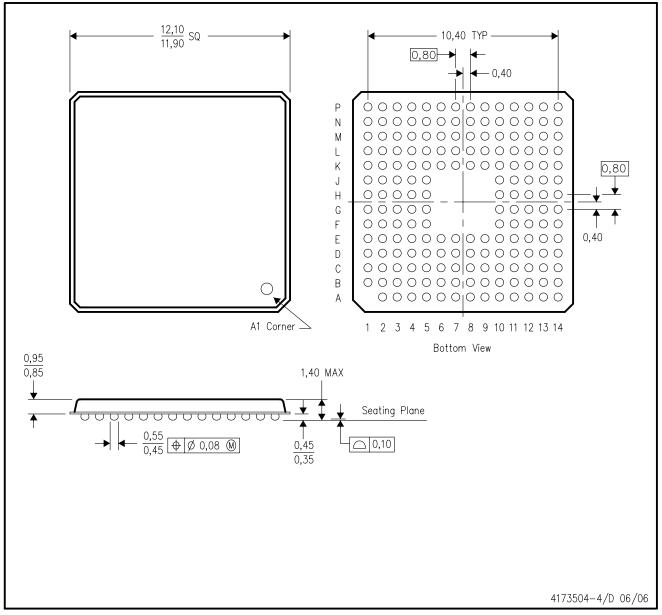

Figure 2–1 illustrates the ball locations for the 179-pin ball grid array (BGA) package and is used in conjunction with Table 2–1 to locate signal names and ball grid numbers.

$DV_{DD}$  is the power supply for the I/O pins while  $CV_{DD}$  is the power supply for the core.  $V_{SS}$  is the ground for both the I/O pins and the core.  $RCV_{DD}$  and  $RDV_{DD}$  are RTC module core and I/O supply, respectively.

#### 2.2.1 Terminal Assignments for the GHH and ZHH Packages

Figure 2–1. 179-Terminal GHH and ZHH Ball Grid Array (Bottom View)

Table 2-1. Pin Assignments for the GHH and ZHH Packages

| BALL# | SIGNAL NAME       | BALL# | SIGNAL<br>NAME   | BALL# | SIGNAL<br>NAME   | BALL# | SIGNAL<br>NAME   |

|-------|-------------------|-------|------------------|-------|------------------|-------|------------------|

| A2    | V <sub>SS</sub>   | D5    | GPIO5            | H2    | $DV_DD$          | L13   | D15              |

| А3    | GPIO4             | D6    | DR0              | H3    | A19              | L14   | CV <sub>DD</sub> |

| A4    | DV <sub>DD</sub>  | D7    | CLKR1            | H4    | C4               | M1    | C10              |

| A5    | FSR0              | D8    | DR1              | H5    | C5               | M2    | C13              |

| A6    | CV <sub>DD</sub>  | D9    | DV <sub>DD</sub> | H10   | DV <sub>DD</sub> | M3    | VSS              |

| A7    | FSR1              | D10   | FSX2             | H11   | A'[0]            | M4    | CV <sub>DD</sub> |

| A8    | $DV_DD$           | D11   | V <sub>SS</sub>  | H12   | RESET            | M5    | V <sub>SS</sub>  |

| A9    | CLKR2             | D12   | NC               | H13   | SDA              | M6    | A5               |

| A10   | DR2               | D13   | NC               | H14   | SCL              | M7    | A1               |

| A11   | DX2               | D14   | NC               | J1    | C6               | M8    | A15              |

| A12   | RTCINX1           | E1    | GPIO1            | J2    | $DV_DD$          | M9    | D3               |

| A13   | RDV <sub>DD</sub> | E2    | GPIO2            | J3    | C7               | M10   | D6               |

| A14   | RDV <sub>DD</sub> | E3    | DV <sub>DD</sub> | J4    | C8               | M11   | CV <sub>DD</sub> |

| B1    | Vss               | E4    | VSS              | J5    | CV <sub>DD</sub> | M12   | DV <sub>DD</sub> |

| B2    | CV <sub>DD</sub>  | E5    | VSS              | J10   | CV <sub>DD</sub> | M13   | VSS              |

| В3    | GPIO3             | E6    | DV <sub>DD</sub> | J11   | CV <sub>DD</sub> | M14   | D12              |

| B4    | TIN/TOUT0         | E7    | DX0              | J12   | TRST             | N1    | V <sub>SS</sub>  |

| B5    | CLKR0             | E8    | FSX1             | J13   | TCK              | N2    | VSS              |

| B6    | FSX0              | E9    | DX1              | J14   | TMS              | N3    | A13              |

| B7    | CV <sub>DD</sub>  | E10   | NC               | K1    | A18              | N4    | A10              |

| B8    | CV <sub>DD</sub>  | E11   | NC               | K2    | C9               | N5    | A7               |

| B9    | V <sub>SS</sub>   | E12   | V <sub>SS</sub>  | K3    | C11              | N6    | DV <sub>DD</sub> |

| B10   | CLKX2             | E13   | V <sub>SS</sub>  | K4    | V <sub>SS</sub>  | N7    | CV <sub>DD</sub> |

| B11   | Vss               | E14   | XF               | K5    | Vss              | N8    | CVDD             |

| B12   | RTCINX2           | F1    | X1               | K6    | A3               | N9    | Vss              |

| B13   | RDVDD             | F2    | X2/CLKIN         | K7    | A2               | N10   | Vss              |

| B14   | Vss               | F3    | GPIO0            | K8    | D1               | N11   | D8               |

| C1    | NC NC             | F4    | V <sub>SS</sub>  | K9    | A14              | N12   | D11              |

| C2    | V <sub>SS</sub>   | F5    | CLKOUT           | K10   | DV <sub>DD</sub> | N13   | DV <sub>DD</sub> |

| C3    | NC NC             | F10   | DV <sub>DD</sub> | K11   | EMU0             | N14   | VSS              |

| C4    | GPIO6             | F11   | VSS              | K12   | EMU1/OFF         | P1    | V <sub>SS</sub>  |

| C5    | Vss               | F12   | INT4             | K13   | TDO              | P2    | VSS              |

| C6    | CLKX0             | F13   | DV <sub>DD</sub> | K14   | TDI              | P3    | A12              |

| C7    | V <sub>SS</sub>   | F14   | INT3             | L1    | CV <sub>DD</sub> | P4    | A9               |

| C8    | CLKX1             | G1    | CV <sub>DD</sub> | L2    | C14              | P5    | A17              |

| C9    | FSR2              | G2    | C1               | L3    | C12              | P6    | A4               |

| C10   | CV <sub>DD</sub>  | G3    | A20              | L4    | A11              | P7    | A16              |

| C11   | Vss               | G4    | C2               | L5    | A8               | P8    | DV <sub>DD</sub> |

| C12   | RCV <sub>DD</sub> | G5    | C0               | L6    | A6               | P9    | D2               |

| C13   | Vss               | G10   | INT2             | L7    | A0               | P10   | D5               |

| C14   | DV <sub>DD</sub>  | G11   | CV <sub>DD</sub> | L8    | D0               | P11   | D7               |

| D1    | GPIO7             | G12   | Vss              | L9    | D4               | P12   | D10              |

| D2    | DV <sub>DD</sub>  | G13   | INT1             | L10   | D9               | P13   | DV <sub>DD</sub> |

| D3    | RSVD2             | G14   | INTO             | L11   | D13              | P14   | DVDD             |

| D4    | RSVD1             | H1    | C3               | L12   | D14              |       | טטיי             |

#### 2.2.2 Pin Assignments for the PGE Package

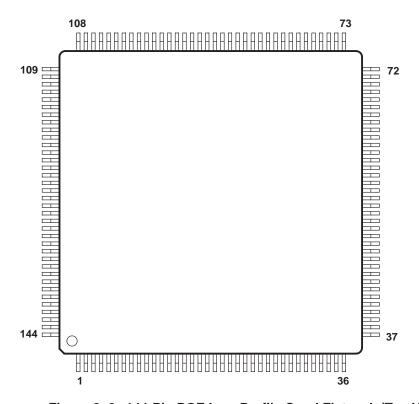

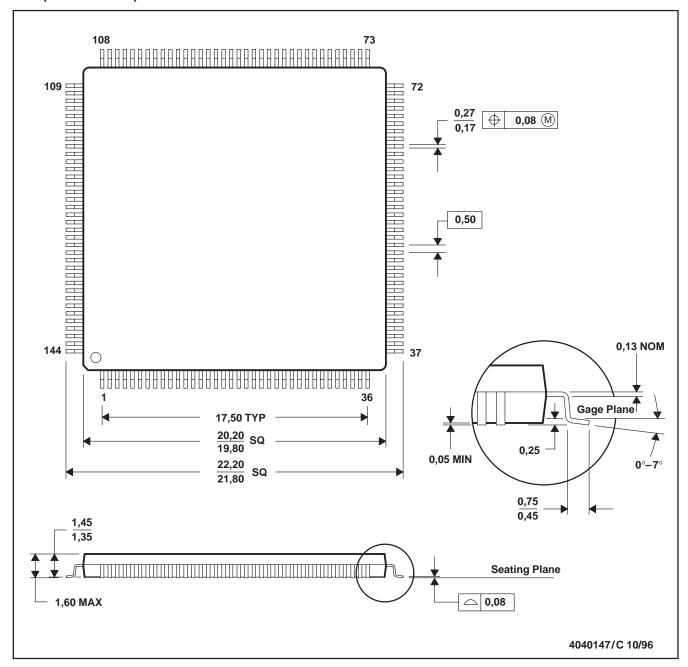

The TMS320VC5503PGE 144-pin low-profile quad flatpack (LQFP) pin assignments are shown in Figure 2–2 and is used in conjunction with Table 2-2 to locate signal names and pin numbers.

${\rm DV_{DD}}$  is the power supply for the I/O pins while  ${\rm CV_{DD}}$  is the power supply for the core.  ${\rm V_{SS}}$  is the ground for both the I/O pins and the core.  ${\rm RCV_{DD}}$  and  ${\rm RDV_{DD}}$  are RTC module core and I/O supply, respectively.

Figure 2–2. 144-Pin PGE Low-Profile Quad Flatpack (Top View)

Table 2-2. Pin Assignments for the PGE Package

| PIN NO. | SIGNAL NAME       |

|---------|------------------|---------|------------------|---------|------------------|---------|-------------------|

| 1       | V <sub>SS</sub>  | 37      | V <sub>SS</sub>  | 73      | V <sub>SS</sub>  | 109     | $RDV_{DD}$        |

| 2       | NC               | 38      | A13              | 74      | D12              | 110     | RCV <sub>DD</sub> |

| 3       | RSVD1            | 39      | A12              | 75      | D13              | 111     | RTCINX2           |

| 4       | RSVD2            | 40      | A11              | 76      | D14              | 112     | RTCINX1           |

| 5       | $DV_DD$          | 41      | CV <sub>DD</sub> | 77      | D15              | 113     | V <sub>SS</sub>   |

| 6       | GPIO7            | 42      | A10              | 78      | CV <sub>DD</sub> | 114     | Vss               |

| 7       | Vss              | 43      | A9               | 79      | EMU0             | 115     | V <sub>SS</sub>   |

| 8       | $DV_DD$          | 44      | A8               | 80      | EMU1/OFF         | 116     | DX2               |

| 9       | GPIO2            | 45      | Vss              | 81      | TDO              | 117     | FSX2              |

| 10      | GPIO1            | 46      | A7               | 82      | TDI              | 118     | CV <sub>DD</sub>  |

| 11      | V <sub>SS</sub>  | 47      | A6               | 83      | CV <sub>DD</sub> | 119     | CLKX2             |

| 12      | GPIO0            | 48      | A5               | 84      | TRST             | 120     | DR2               |

| 13      | X2/CLKIN         | 49      | $DV_DD$          | 85      | TCK              | 121     | FSR2              |

| 14      | X1               | 50      | A4               | 86      | TMS              | 122     | Vss               |

| 15      | CLKOUT           | 51      | А3               | 87      | CV <sub>DD</sub> | 123     | CLKR2             |

| 16      | C0               | 52      | A2               | 88      | $DV_DD$          | 124     | DX1               |

| 17      | C1               | 53      | CV <sub>DD</sub> | 89      | SDA              | 125     | FSX1              |

| 18      | CV <sub>DD</sub> | 54      | A1               | 90      | SCL              | 126     | $DV_DD$           |

| 19      | C2               | 55      | A0               | 91      | RESET            | 127     | CLKX1             |

| 20      | C3               | 56      | $DV_DD$          | 92      | Vss              | 128     | DR1               |

| 21      | C4               | 57      | D0               | 93      | INT0             | 129     | FSR1              |

| 22      | C5               | 58      | D1               | 94      | INT1             | 130     | CLKR1             |

| 23      | C6               | 59      | D2               | 95      | CV <sub>DD</sub> | 131     | DX0               |

| 24      | $DV_DD$          | 60      | V <sub>SS</sub>  | 96      | INT2             | 132     | CV <sub>DD</sub>  |

| 25      | C7               | 61      | D3               | 97      | ĪNT3             | 133     | FSX0              |

| 26      | C8               | 62      | D4               | 98      | $DV_DD$          | 134     | CLKX0             |

| 27      | C9               | 63      | D5               | 99      | INT4             | 135     | DR0               |

| 28      | C11              | 64      | V <sub>SS</sub>  | 100     | Vss              | 136     | FSR0              |

| 29      | CV <sub>DD</sub> | 65      | D6               | 101     | XF               | 137     | CLKR0             |

| 30      | CV <sub>DD</sub> | 66      | D7               | 102     | V <sub>SS</sub>  | 138     | V <sub>SS</sub>   |

| 31      | C14              | 67      | D8               | 103     | V <sub>SS</sub>  | 139     | $DV_DD$           |

| 32      | C12              | 68      | CV <sub>DD</sub> | 104     | DV <sub>DD</sub> | 140     | TIN/TOUT0         |

| 33      | Vss              | 69      | D9               | 105     | NC               | 141     | GPIO6             |

| 34      | C10              | 70      | D10              | 106     | NC               | 142     | GPIO4             |

| 35      | C13              | 71      | D11              | 107     | $DV_DD$          | 143     | GPIO3             |

| 36      | Vss              | 72      | DV <sub>DD</sub> | 108     | Vss              | 144     | Vss               |

## 2.3 Signal Descriptions

Table 2–3 lists each signal, function, and operating mode(s) grouped by function. See Section 2.2 for pin locations based on package type.

Table 2-3. Signal Descriptions

| TERMINAL NAME       | MULTIPLEXED<br>SIGNAL NAME | I/O/Z† | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | вк‡ | RESET<br>CONDITION                                  |

|---------------------|----------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------|

|                     |                            |        | PARALLEL BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |                                                     |

| A[13:0]             |                            | I/O/Z  | A subset of the parallel address bus A13–A0 of the C55x <sup>™</sup> DSP core bonded to external pins. These pins serve in one of three functions: HPI address bus (HPI.HA[13:0]), EMIF address bus (EMIF.A[13:0]), or general-purpose I/O (GPIO.A[13:0]). The initial state of these pins depends on the GPIO0 pin. See Section 3.5.1 for more information.  The address bus has a bus holder feature that eliminates passive component requirement and the power dissipation associated with them. The bus holders keep the address bus at the previous logic level when the bus goes into a high-impedance state. |     |                                                     |

|                     | HPI.HA[13:0]               | ı      | HPI address bus. HPI.HA[13:0] is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 10. This setting enables the HPI in non-multiplexed mode.  HPI.HA[13:0] provides DSP internal memory access to host. In non-multiplexed mode, these signals are driven by an external host as address lines.                                                                                                                                                                                                                                                                               | BK  | GPIO0 = 1:<br>Output,<br>EMIF.A[13:0]<br>GPIO0 = 0: |

|                     | EMIF.A[13:0]               | O/Z    | EMIF address bus. EMIF.A[13:0] is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 01. This setting enables the full EMIF mode and the EMIF drives the parallel port address bus. The internal A[14] address is exclusive-ORed with internal A[0] address and the result is routed to the A[0] pin.                                                                                                                                                                                                                                                                          |     | Input,<br>HPI.HA[13:0]                              |

|                     | GPIO.A[13:0]               | I/O/Z  | General-purpose I/O address bus. GPIO.A[13:0] is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 11. This setting enables the HPI in multiplexed mode with the Parallel Port GPIO register controlling the parallel port address bus. GPIO is also selected when the Parallel Port Mode bit field is 00, enabling the Data EMIF mode.                                                                                                                                                                                                                                       |     |                                                     |

| A'[0]<br>(BGA only) | EMIF.A'[0]                 | O/Z    | EMIF address bus A'[0]. This pin is not multiplexed with EMIF.A[14] and is used as the least significant external address pin on the BGA package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | Output                                              |

$<sup>^{\</sup>dagger}$  I = Input, O = Output, S = Supply, Hi-Z = High-impedance

<sup>‡</sup>BK = bus keeper (the bus keeper maintains the previous voltage level during reset or while the output pin is not driven), PU = pullup, PD = pulldown, H = hysteresis input buffer, FS = fail-safe buffer

Table 2-3. Signal Descriptions (Continued)

| TERMINAL NAME          | MULTIPLEXED<br>SIGNAL NAME | I/O/Z† | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                          | вк‡ | RESET<br>CONDITION                                  |

|------------------------|----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------|

|                        |                            |        | PARALLEL BUS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                          |     |                                                     |

| A[15:14]<br>(BGA only) |                            | I/O/Z  | A subset of the parallel address bus A15–A14 of the C55x <sup>™</sup> DSP core bonded to external pins. These pins serve in one of two functions: EMIF address bus (EMIF.A[15:14]), or general-purpose I/O (GPIO.A[15:14]). The initial state of these pins depends on the GPIO0 pin. See Section 3.5.1 for more information.                                                                                     |     |                                                     |

| (EG/Comy)              |                            |        | The address bus has a bus holder feature that eliminates passive component requirement and the power dissipation associated with them. The bus holders keep the address bus at the previous logic level when the bus goes into a high-impedance state.                                                                                                                                                            | ВK  | GPIO0 = 1:<br>Output,<br>EMIF.A[15:14]              |

|                        | EMIF.A[15:14]              | O/Z    | EMIF address bus. EMIF.A[15:14] is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 01. This setting enables the full EMIF mode and the EMIF drives the parallel port address bus.                                                                                                                                                                                        |     | GPIO0 = 0:<br>Input,<br>GPIO.A[15:14]               |

|                        | GPIO.A[15:14]              | I/O/Z  | General-purpose I/O address bus. GPIO.A[15:14] is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 11. This setting enables the HPI in multiplexed mode with the Parallel Port GPIO register controlling the parallel port address bus. GPIO is also selected when the Parallel Port Mode bit field is 00, enabling the Data EMIF mode.                                   |     | , ,                                                 |

| A[20:16]<br>(BGA only) | EMIF.A[20:16]              | O/Z    | EMIF address bus. At reset, these address pins are set as output.  NOTE: These pins only function as EMIF address pins and they are not multiplexed for any other function.                                                                                                                                                                                                                                       |     | Output                                              |

|                        |                            |        | A subset of the parallel bidirectional data bus D31–D0 of the C55x™ DSP core. These pins serve in one of two functions: EMIF data bus (EMIF.D[15:0]) or HPI data bus (HPI.HD[15:0]). The initial state of these pins depends on the GPIO0 pin. See Section 3.5.1 for more information.                                                                                                                            |     | GPIO0 = 1:                                          |

| D[15:0]                |                            | I/O/Z  | The data bus includes bus keepers to reduce the static power dissipation caused by floating, unused pins. This eliminates the need for external bias resistors on unused pins. When the data bus is not being driven by the CPU, the bus keepers keep the pins at the logic level that was most recently driven. (The data bus keepers are enabled at reset, and can be enabled/disabled under software control.) | ВК  | Input, EMIF.D[15:0]  GPIO0 = 0: Input, HPI.HD[15:0] |

|                        | EMIF.D[15:0]               | I/O/Z  | EMIF data bus. EMIF.D[15:0] is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 00 or 01.                                                                                                                                                                                                                                                                                 |     | , , , ,                                             |

| +, , , ,               | HPI.HD[15:0]               | I/O/Z  | HPI data bus. HPI.HD[15:0] is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 10 or 11.                                                                                                                                                                                                                                                                                  |     |                                                     |

$<sup>^{\</sup>dagger}$ I = Input, O = Output, S = Supply, Hi-Z = High-impedance  $^{\ddagger}$ BK = bus keeper (the bus keeper maintains the previous voltage level during reset or while the output pin is not driven), PU = pullup, PD = pulldown, H = hysteresis input buffer, FS = fail-safe buffer

SPRS245J

Table 2-3. Signal Descriptions (Continued)

| TERMINAL<br>NAME | MULTIPLEXED<br>SIGNAL NAME | I/O/Z†                                                                                                                                                                                                                                                                                | FUNCTION                                                                                                                                                                                                                                                                                       | вк‡ | RESET<br>CONDITION                       |

|------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------|

|                  |                            |                                                                                                                                                                                                                                                                                       | PARALLEL BUS (CONTINUED)                                                                                                                                                                                                                                                                       |     |                                          |

| СО               |                            | EMIF asynchronous memory read enable or general-purpose IO8. This pin serves in one of two functions: EMIF asynchronous memory read enable (EMIF.ARE) or general-purpose IO8 (GPIO8). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information. |                                                                                                                                                                                                                                                                                                |     | GPIO0 = 1:<br>Output,<br>EMIF.ARE        |

|                  | EMIF.ARE O/Z               |                                                                                                                                                                                                                                                                                       | Active-low EMIF asynchronous memory read enable. EMIF. ARE is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 00 or 01.                                                                                                                               | BK  | GPIO0 = 0:<br>Input,                     |

|                  | GPIO8                      | I/O/Z                                                                                                                                                                                                                                                                                 | General-purpose IO8. GPIO8 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 10 or 11.                                                                                                                                                        |     | GPIO8                                    |

| C1               |                            | O/Z                                                                                                                                                                                                                                                                                   | EMIF asynchronous memory output enable or HPI interrupt output. This pin serves in one of two functions: EMIF asynchronous memory output enable (EMIF.AOE) or HPI interrupt output (HPI.HINT). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information. |     | GPIO0 = 1:<br>Output,<br>EMIF.AOE        |

|                  | EMIF.AOE O/Z               |                                                                                                                                                                                                                                                                                       | Active-low asynchronous memory output enable. EMIF. AOE is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 00 or 01.                                                                                                                                  |     | GPIO0 = 0:<br>Output,                    |

|                  | HPI.HINT O/Z               |                                                                                                                                                                                                                                                                                       | Active-low HPI interrupt output. HPI. HINT is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 10 or 11.                                                                                                                                               |     | HPI.HINT                                 |

| C2               |                            | I/O/Z                                                                                                                                                                                                                                                                                 | EMIF asynchronous memory write enable or HPI read/write. This pin serves in one of two functions: EMIF asynchronous memory write enable (EMIF.AWE) or HPI read/write (HPI.HR/W). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information.               |     | GPIO0 = 1:<br>Output,                    |

|                  | EMIF.AWE                   | O/Z                                                                                                                                                                                                                                                                                   | Active-low EMIF asynchronous memory write enable. EMIF.AWE is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 00 or 01.                                                                                                                               | ВК  | EMIF.AWE  GPIO0 = 0: Input,              |

| HPI.HR/W         |                            | I                                                                                                                                                                                                                                                                                     | HPI read/write. HPI.HR $\overline{W}$ is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 10 or 11. HPI.HR $\overline{W}$ controls the direction of the HPI transfer.                                                                                  |     | HPI.HR/W                                 |

| С3               |                            | I/O/Z                                                                                                                                                                                                                                                                                 | EMIF data ready input or HPI ready output. This pin serves in one of two functions: EMIF data ready input (EMIF.ARDY) or HPI ready output (HPI.HRDY). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information.                                          |     | GPIO0 = 1:<br>Input,                     |

|                  | EMIF.ARDY I                |                                                                                                                                                                                                                                                                                       | EMIF data ready input. Used to insert wait states for slow memories. EMIF.ARDY is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 00 or 01. When this pin is used as ARDY, an external $2.2~\mathrm{k}\Omega$ pull-up resistor is recommended.        | Н   | EMIF.ARDY  GPIO0 = 0:  Output,  HPI.HRDY |

|                  | HPI.HRDY                   | 0                                                                                                                                                                                                                                                                                     | HPI ready output. HPI.HRDY is selected when the Parallel Port Mode bit field of the External Bus Selection Register is 10 or 11.                                                                                                                                                               |     | 1111.111.01                              |

$<sup>^{\</sup>dagger}$  I = Input, O = Output, S = Supply, Hi-Z = High-impedance

<sup>‡</sup>BK = bus keeper (the bus keeper maintains the previous voltage level during reset or while the output pin is not driven), PU = pullup, PD = pulldown, H = hysteresis input buffer, FS = fail-safe buffer

Table 2-3. Signal Descriptions (Continued)

| TERMINAL<br>NAME | MULTIPLEXED<br>SIGNAL NAME | I/O/Z† | FUNCTION                                                                                                                                                                                                                                                                                                                                              | вк‡ | RESET<br>CONDITION                |

|------------------|----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|

|                  |                            |        | PARALLEL BUS (CONTINUED)                                                                                                                                                                                                                                                                                                                              |     |                                   |

| C4               | C4                         |        | EMIF chip select for memory space CE0 or general-purpose IO9. This pin serves in one of two functions: EMIF chip select for memory space CE0 (EMIF. CE0) or general-purpose IO9 (GPIO9). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information.                                                              |     | GPIO0 = 1:<br>Output,<br>EMIF.CE0 |

|                  | EMIF.CE0                   | O/Z    | Active-low EMIF chip select for memory space CE0. EMIF. CE0 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 00 or 01.                                                                                                                                                                              | ВК  | GPIO0 = 0:<br>Input,              |

|                  | GPIO9                      | I/O/Z  | General-purpose IO9. GPIO9 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 10 or 11.                                                                                                                                                                                                               |     | GPIO9                             |

| C5               |                            | I/O/Z  | EMIF chip select for memory space CE1 or general-purpose IO10. This pin serves in one of two functions: EMIF chip-select for memory space CE1 (EMIF.CE1) or general-purpose IO10 (GPIO10). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information.                                                            |     | GPIO0 = 1:<br>Output,<br>EMIF.CE1 |

|                  | EMIF.CE1                   |        | Active-low EMIF chip select for memory space CE1. EMIF. CE1 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 00 or 01.                                                                                                                                                                              | ВК  | GPIO0 = 0:<br>Input,              |

| GPIO10 I/O       |                            | I/O/Z  | General-purpose IO10. GPIO10 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 10 or 11.                                                                                                                                                                                                             |     | GPIO10                            |

| C6               | C6 I/C                     |        | EMIF chip select for memory space CE2 or HPI control input 0. This pin serves in one of two functions: EMIF chip-select for memory space CE2 (EMIF.CE2) or HPI control input 0 (HPI.HCNTL0). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information.                                                          |     | GPIO0 = 1:<br>Output,             |

|                  | EMIF.CE2                   | O/Z    | Active-low EMIF chip select for memory space CE2. EMIF. CE2 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 00 or 01.                                                                                                                                                                              | ВК  | EMIF.CE2  GPIO0 = 0:              |

|                  | HPI.HCNTL0                 | ı      | HPI control input 0. This pin, in conjunction with HPI.HCNTL1, selects a host access to one of the three HPI registers. HPI.HCNTL0 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 10 or 11.                                                                                                       |     | Input,<br>HPI.HCNTL0              |

| C7               |                            | I/O/Z  | EMIF chip select for memory space CE3, general-purpose IO11, or HPI control input 1. This pin serves in one of three functions: EMIF chip-select for memory space CE3 (EMIF.CE3), general-purpose IO11 (GPIO11), or HPI control input 1 (HPI.HCNTL1). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information. |     | GPIO0 = 1:<br>Output,             |

|                  | EMIF.CE3                   | O/Z    | Active-low EMIF chip select for memory space CE3. EMIF.CE3 is selected when the Parallel Port Mode bit field is of the External Bus Selection Register set to 00 or 01.                                                                                                                                                                               | ВК  | EMIF.CE3  GPIO0 = 0:              |

|                  | GPIO11                     | I/O/Z  | General-purpose IO11. GPIO11 is selected when the Parallel Port Mode bit field is set to 10.                                                                                                                                                                                                                                                          |     | Input,<br>HPI.HCNTL1              |

|                  | HPI.HCNTL1                 | I      | HPI control input 1. This pin, in conjunction with HPI.HCNTL0, selects a host access to one of the three HPI registers. The HPI.HCNTL1 mode is selected when the Parallel Port Mode bit field is set to 11.                                                                                                                                           |     |                                   |

$<sup>^{\</sup>dagger}$ I = Input, O = Output, S = Supply, Hi-Z = High-impedance  $^{\ddagger}$ BK = bus keeper (the bus keeper maintains the previous voltage level during reset or while the output pin is not driven), PU = pullup, PD = pulldown, H = hysteresis input buffer, FS = fail-safe buffer

Table 2-3. Signal Descriptions (Continued)

| TERMINAL NAME | MULTIPLEXED<br>SIGNAL NAME | I/O/Z† | FUNCTION                                                                                                                                                                                                                                                                                                           | вк‡                   | RESET<br>CONDITION     |

|---------------|----------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|

|               |                            |        | PARALLEL BUS (CONTINUED)                                                                                                                                                                                                                                                                                           |                       |                        |

| C8            | C8 I/C                     |        | EMIF byte enable 0 control or HPI byte identification. This pin serves in o of two functions: EMIF byte enable 0 control (EMIF.BE0) or HPI by identification (HPI.HBE0). The initial state of this pin depends on t GPIO0 pin. See Section 3.5.1 for more information.                                             |                       | GPIO0 = 1:<br>Output,  |

|               |                            |        | Active-low EMIF byte enable 0 control. EMIF.BE0 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 00 or 01.                                                                                                                                                       | ВК                    | GPIO0 = 0:             |

|               | HPI.HBE0                   | ı      | HPI byte identification. This pin, in conjunction with HPI.HBE1, identifies the first or second byte of the transfer. HPI.HBE0 is selected when the Parallel Port Mode bit field is set to 10 or 11.                                                                                                               |                       | Input,<br>HPI.HBE0     |

| C9            |                            | I/O/Z  | EMIF byte enable 1 control or HPI byte identification. This pin serves in one of two functions: EMIF byte enable 1 control (EMIF.BE1) or HPI byte identification (HPI.HBE1). The initial state of this pin depends on the GPIO0 pin. See Section 3.5.1 for more information.                                       | GPIO0 = 1:<br>Output, |                        |

|               | EMIF.BE1                   | O/Z    | Active-low EMIF byte enable 1 control. EMIF.BE1 is selected when the Parallel Port Mode bit field of the External Bus Selection Register is set to 00 or 01.                                                                                                                                                       | ВК                    | GPIO0 = 0:             |

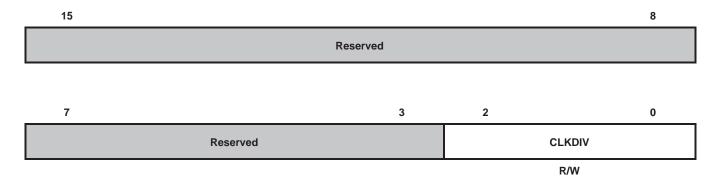

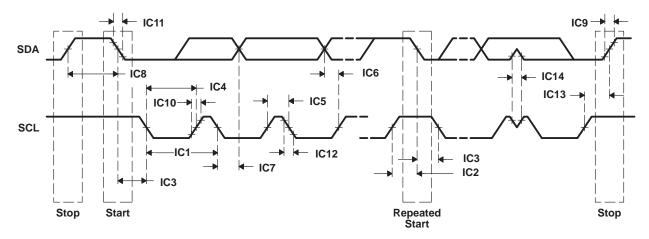

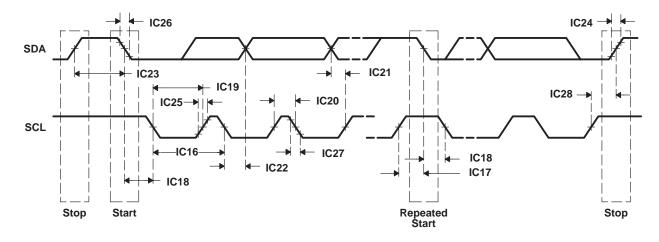

| HPI.HBE1      |                            | I      | HPI byte identification. This pin, in conjunction with HPI. HBE0, identifies the first or second byte of the transfer. HPI. HBE1 is selected when the Parallel Port Mode bit field is set to 10 or 11.                                                                                                             |                       | Input,<br>HPI.HBE1     |