# TMS320VC5501 Fixed-Point Digital Signal Processor

# Data Manual

Literature Number: SPRS206K December 2002 – Revised November 2008

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# **REVISION HISTORY**

This data sheet revision history highlights the technical changes made to the SPRS206J device-specific data sheet to make it an SPRS206K revision.

Scope: See table below.

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21             | Table 2–4, Signal Descriptions:  HD[7:0]: removed "M" from "Other" column  HC0: removed "M" from "Other" column  HC1: removed "M" from "Other" column  HCNTL0: removed "M" from "Other" column  HCNTL1: removed "M" from "Other" column  HCNTL1: removed "M" from "Other" column  HR/W: removed "M" from "Other" column |

| 88             | Table 3–29, Peripheral IDLE Control Register Bit Field Description:  Updated footnote                                                                                                                                                                                                                                   |

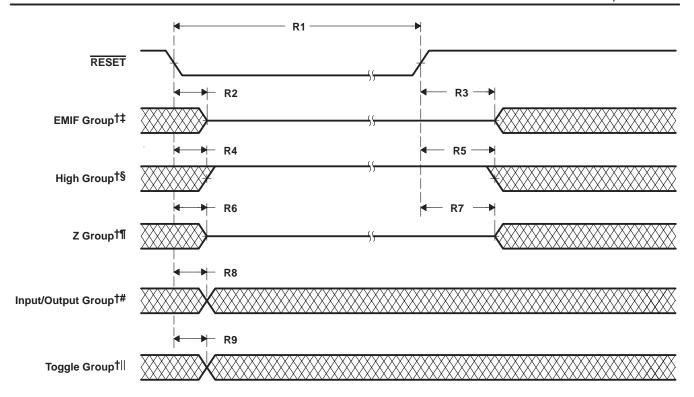

| 161            | Figure 5–22, Reset Timings:  – Added footnote about the state of the DSP pins during power up                                                                                                                                                                                                                           |

# **Contents**

| Se | ction   |           |                                             | Page |

|----|---------|-----------|---------------------------------------------|------|

| 1  | TMS32   | 0VC5501   | Features                                    | 15   |

| 2  | Introdu | uction    |                                             | 16   |

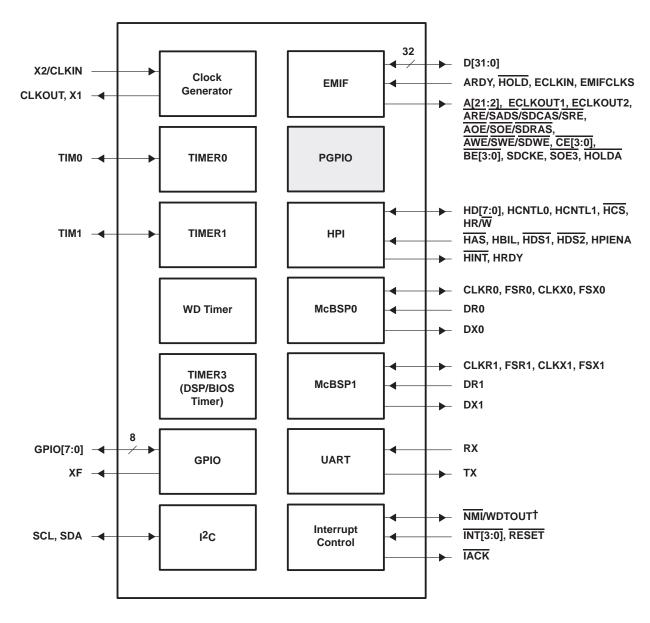

|    | 2.1     | Descripti | on                                          | 16   |

|    | 2.2     | Pin Assig | gnments                                     | 17   |

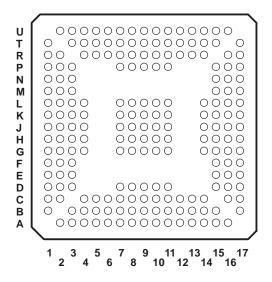

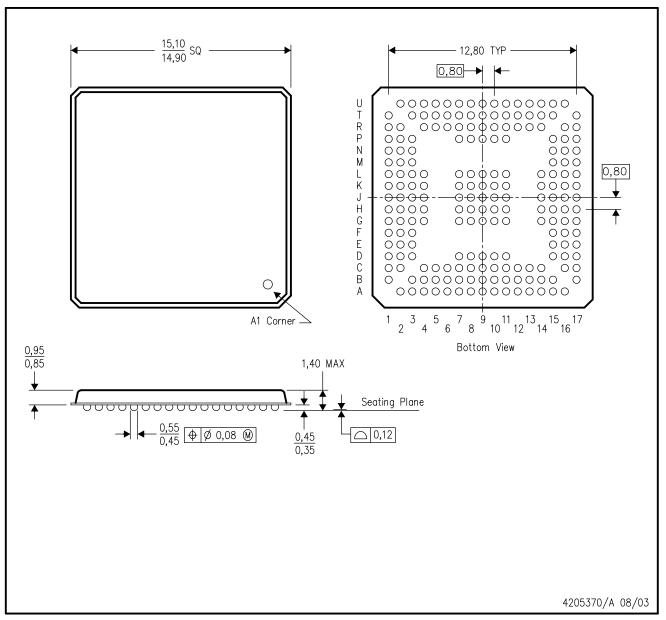

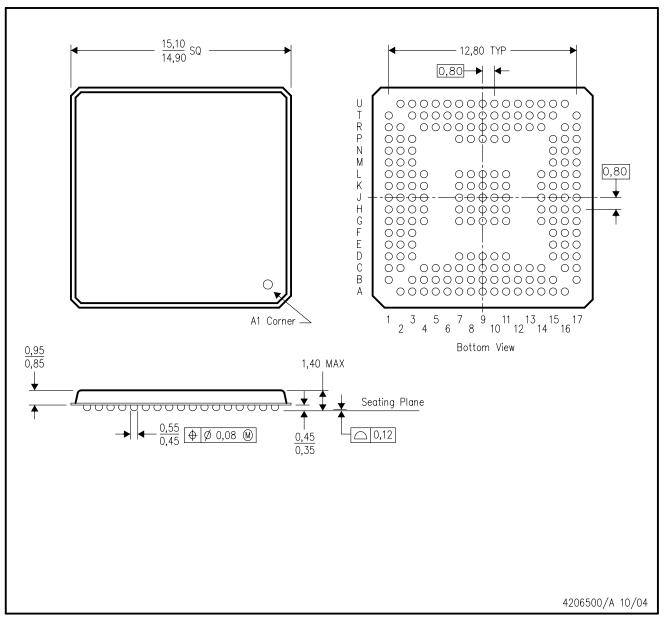

|    |         | 2.2.1     | Ball Grid Array (GZZ and ZZZ)               | 17   |

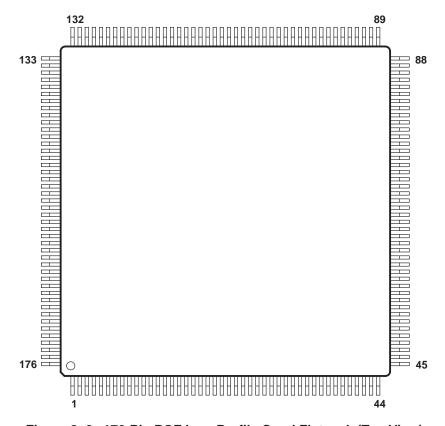

|    |         | 2.2.2     | Low-Profile Quad Flatpack (PGF)             | 19   |

|    | 2.3     | Signal De | escriptions                                 | 21   |

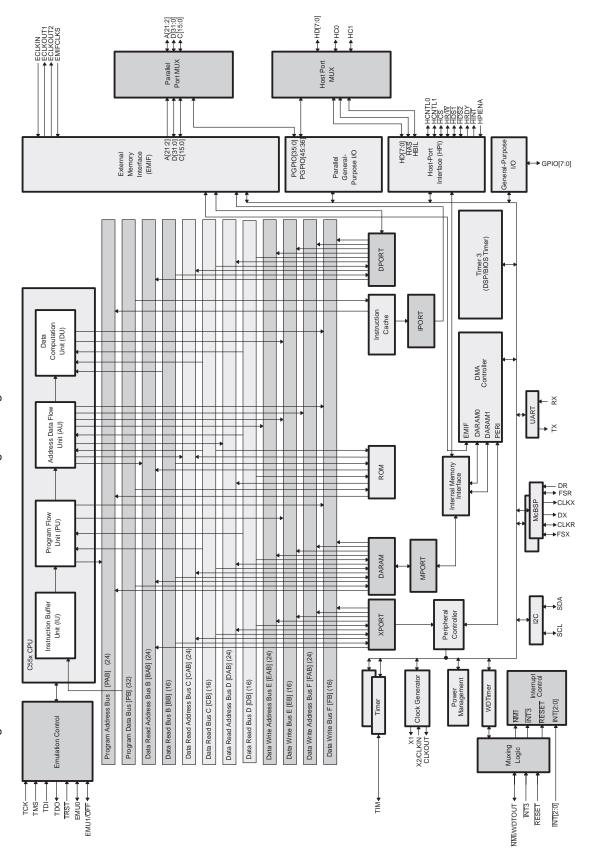

| 3  | Functi  | onal Ove  | rview                                       | 38   |

|    | 3.1     | Memory    |                                             | 39   |

|    |         | 3.1.1     | On-Chip ROM                                 | 39   |

|    |         | 3.1.2     | On-Chip Dual-Access RAM (DARAM)             | 40   |

|    |         | 3.1.3     | Instruction Cache                           | 40   |

|    |         | 3.1.4     | Memory Map                                  | 41   |

|    |         | 3.1.5     | Boot Configuration                          | 42   |

|    | 3.2     | Periphera | als                                         | 42   |

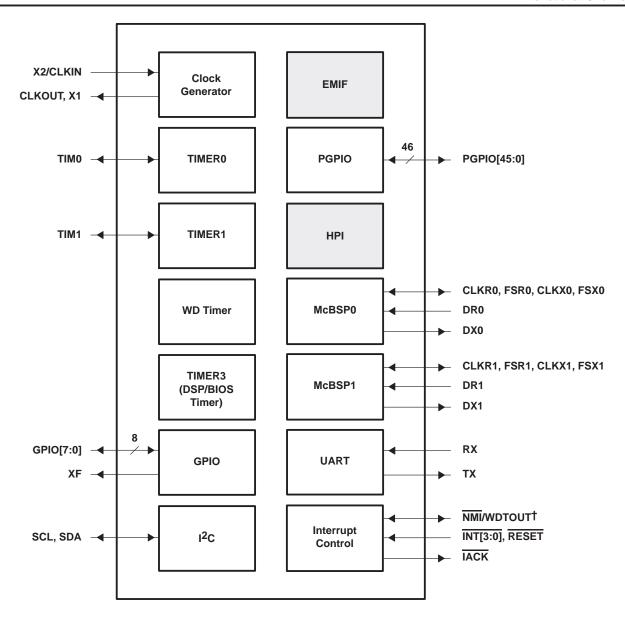

|    | 3.3     | Configura | able External Ports and Signals             | 43   |

|    |         | 3.3.1     | Parallel Port Mux                           | 43   |

|    |         | 3.3.2     | Host Port Mux                               | 45   |

|    |         | 3.3.3     | External Bus Selection Register (XBSR)      | 46   |

|    |         | 3.3.4     | Configuration Examples                      | 48   |

|    | 3.4     | Timers .  |                                             | 50   |

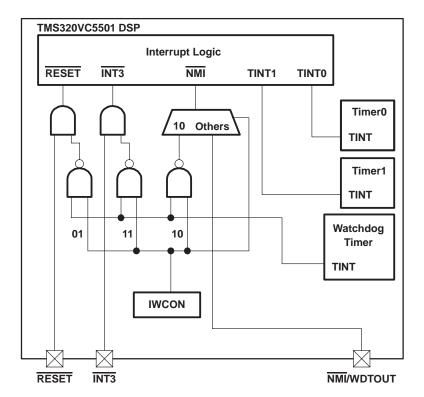

|    |         | 3.4.1     | Timer Interrupts                            | 51   |

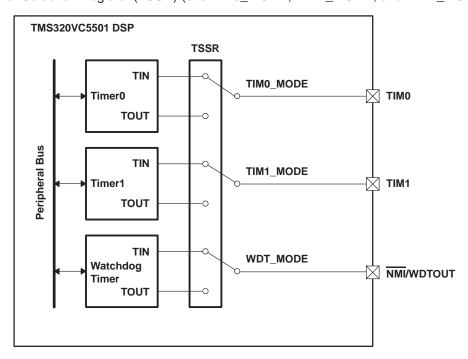

|    |         | 3.4.2     | Timer Pins                                  | 52   |

|    |         | 3.4.3     | Timer Signal Selection Register (TSSR)      | 53   |

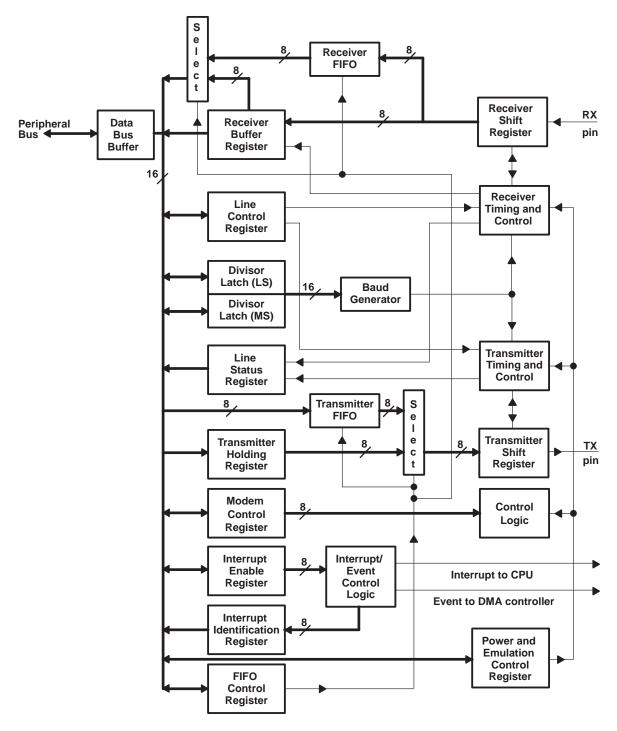

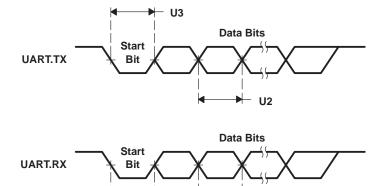

|    | 3.5     |           | Asynchronous Receiver/Transmitter (UART)    | 54   |

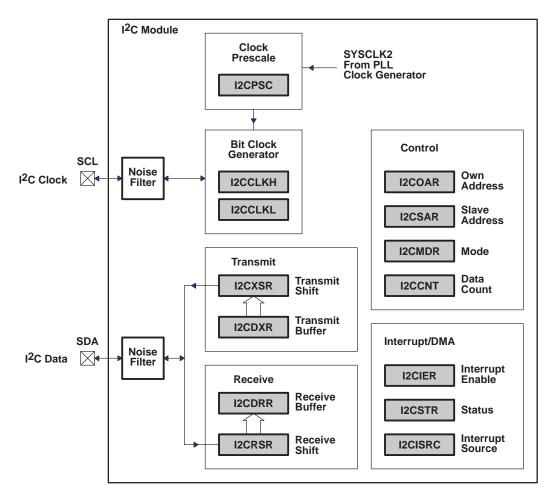

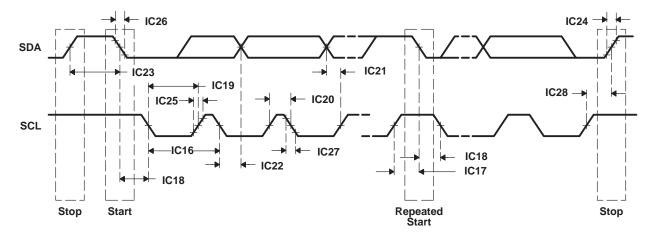

|    | 3.6     |           | egrated Circuit (I <sup>2</sup> C) Module   | 56   |

|    | 3.7     |           | t Interface (HPI)                           | 57   |

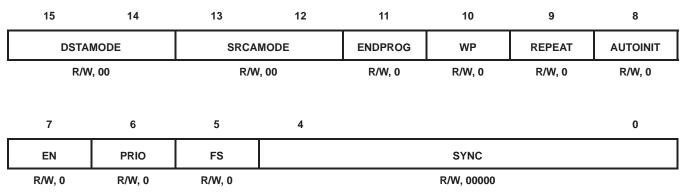

|    | 3.8     |           | emory Access (DMA) Controller               | 58   |

|    |         | 3.8.1     | DMA Channel 0 Control Register (DMA_CCR0)   | 58   |

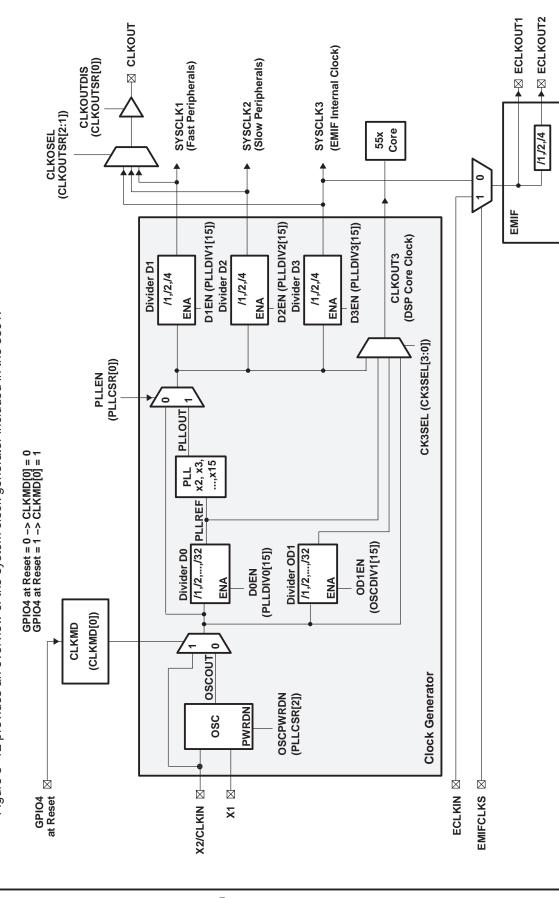

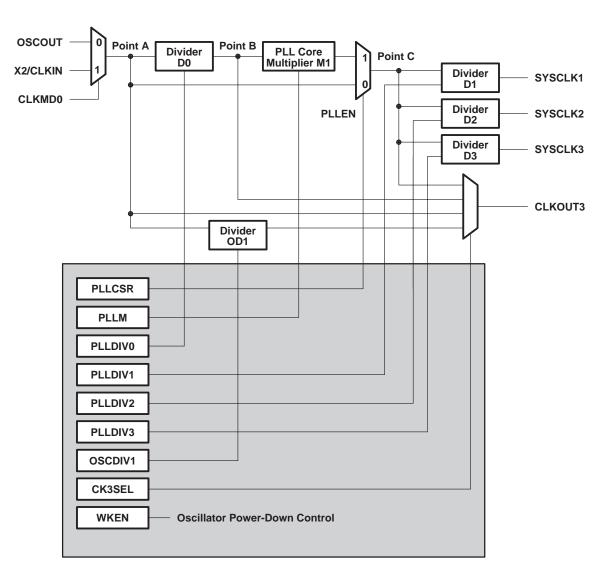

|    | 3.9     |           | Clock Generator                             | 60   |

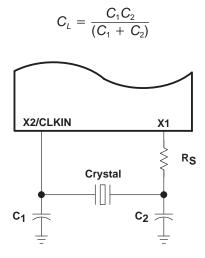

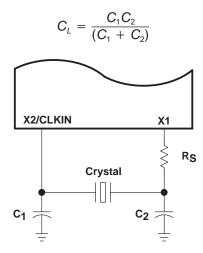

|    |         | 3.9.1     | Input Clock Source                          | 61   |

|    |         | 3.9.2     | Clock Groups                                | 63   |

|    |         | 3.9.3     | EMIF Input Clock Selection                  | 64   |

|    |         | 3.9.4     | Changing the Clock Group Frequencies        | 64   |

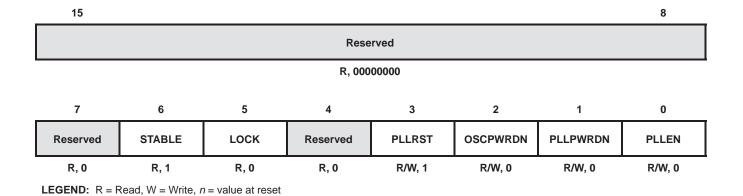

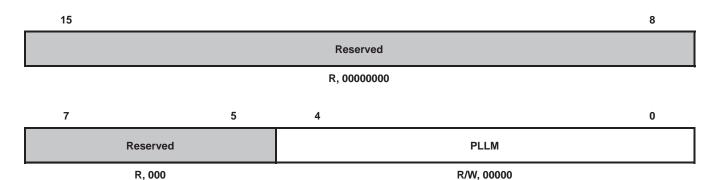

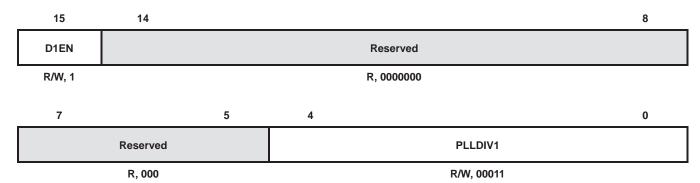

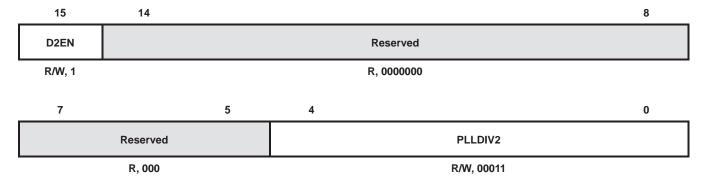

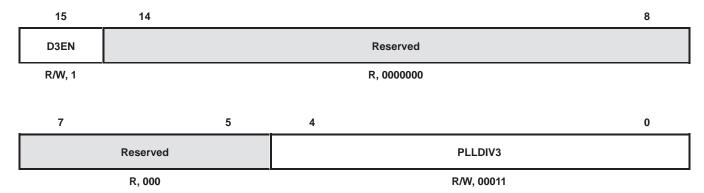

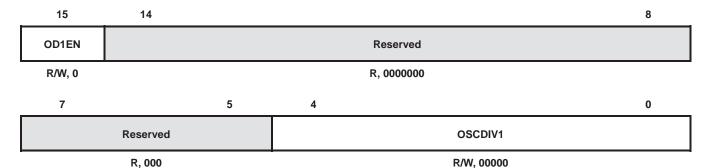

|    |         | 3.9.5     | PLL Control Registers                       | 66   |

|    |         | 3.9.6     | Reset Sequence                              | 76   |

|    | 3.10    | Idle Cont |                                             | 77   |

|    |         | 3.10.1    | Clock Domains                               | 77   |

|    |         | 3.10.2    | IDLE Procedures                             | 77   |

|    |         | 3.10.3    | Module Behavior at Entering IDLE State      | 80   |

|    |         | 3.10.4    | Wake-Up Procedures                          | 81   |

|    |         | 3.10.5    | Auto-Wakeup/Idle Function for McBSP and DMA | 84   |

| Se | ection     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |            | 3.10.6 Clock State of Multiplexed Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    |            | 3.10.7 IDLE Control and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | 3.11       | General-Purpose I/O (GPIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|    |            | 3.11.1 General-Purpose I/O Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |            | 3.11.2 Parallel Port General-Purpose I/O (PGPIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 3.12       | External Bus Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |            | 3.12.1 External Bus Control Register (XBCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 3.13       | Internal Ports and System Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |            | 3.13.1 XPORT Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |            | 3.13.2 DPORT Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |            | 3.13.3 IPORT Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

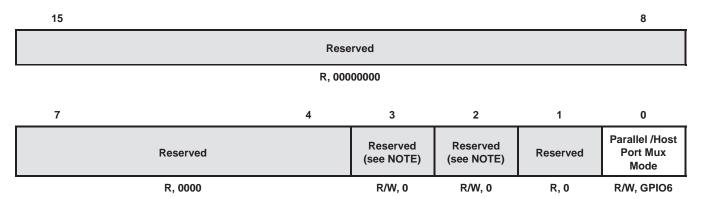

|    |            | 3.13.4 System Configuration Register (CONFIG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |            | 3.13.5 Time-Out Control Register (TOCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|    | 3.14       | CPU Memory-Mapped Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 3.15       | Peripheral Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 3.16       | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

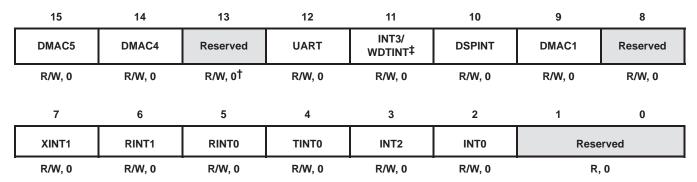

|    | 0.10       | 3.16.1 IFR and IER Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

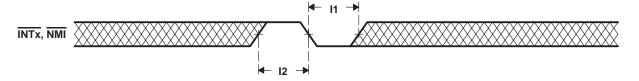

|    |            | 3.16.2 Interrupt Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

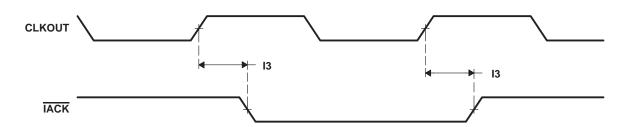

|    |            | 3.16.3 Interrupt Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

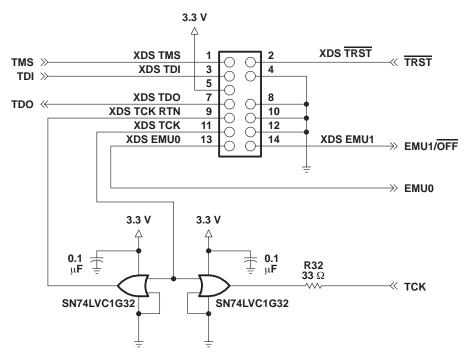

|    | 3.17       | Notice Concerning TCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 0          | Notice Contesting For Transfer and Transfer |

| 4  | Suppo      | ort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 4.1        | Notices Concerning JTAG (IEEE 1149.1) Boundary Scan Test Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |            | 4.1.1 Initialization Requirements for Boundary Scan Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    |            | 4.1.2 Boundary Scan Description Language (BSDL) Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 4.2        | Documentation Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 4.3        | Device and Development-Support Tool Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 1.0        | Dovido and Dovidopinion Capport roof romandiatare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5  | Electr     | ical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •  | 5.1        | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | 5.2        | Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 5.3        | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 5.4        | Electrical Characteristics Over Recommended Operating Case Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

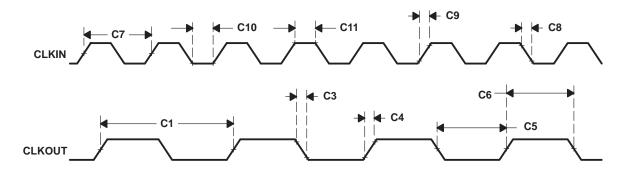

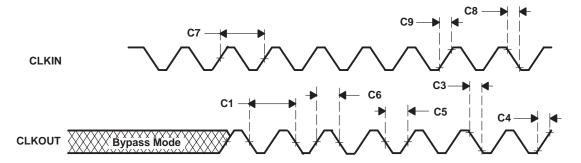

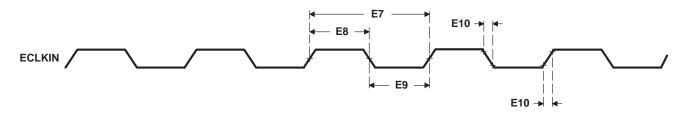

|    | 5.5        | Timing Parameter Symbology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |