**THS4552** SBOS831B - DECEMBER 2016 - REVISED JUNE 2021

### **THS4552**

# Dual-Channel, Low-Noise, Precision, 150-MHz, Fully Differential Amplifier

#### 1 Features

- Bandwidth: 150 MHz (G = 1 V/V)

- Differential output slew rate: 220 V/µs

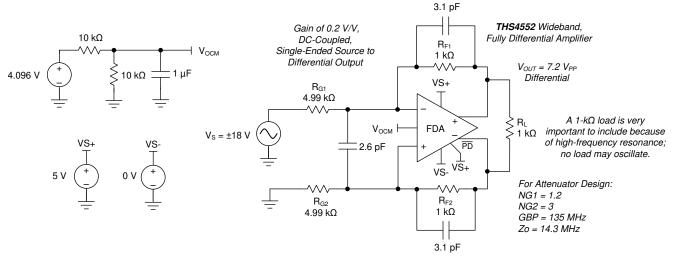

- Gain bandwidth product: 135 MHz

- Negative rail input (NRI), rail-to-rail output (RRO)

- Wide output common-mode control range

- Single-supply operating range: 2.7 V to 5.4 V

- Trimmed-supply current: 1.37 mA per channel at 5 V

- 25°C input offset: ±175 µV (maximum)

- Input offset voltage drift: ±2.0 µV/°C (maximum)

- Differential input voltage noise: 3.3 nV/√ Hz

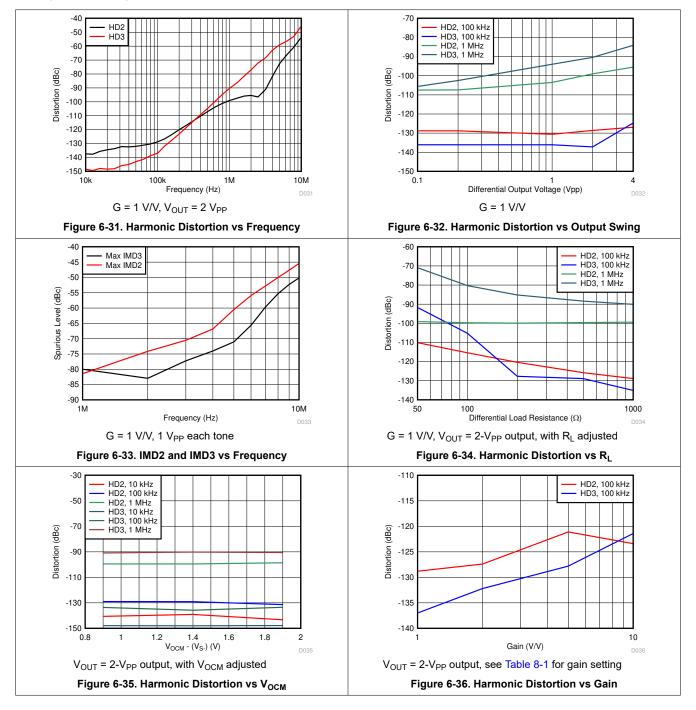

- HD2: -128 dBc at 2 V<sub>PP</sub>, 100 kHz

- HD3: -139 dBc at 2 V<sub>PP</sub>, 100 kHz

- < 50 ns settling time: 4 V Step to 0.01%

- 18-bit settling time: 4 V Step, < 500 ns

### 2 Applications

- 24-Bit, delta-sigma ( $\Delta\Sigma$ ) ADC drivers

- 16- to 20-Bit, differential, high-speed SAR drivers

- Differential active filters

- Differential transimpedance amplifiers

- Pin-compatible upgrade to the THS4522 (TSSOP-16 only)

### 3 Description

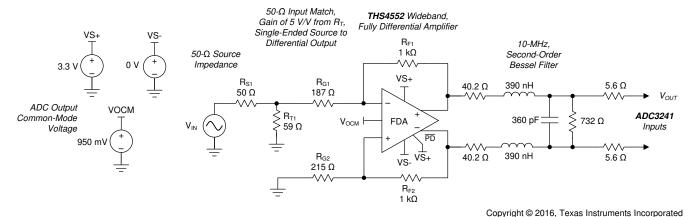

The THS4552 fully differential amplifier offers an easy interface from single-ended sources to the differential output required by high-precision analogto-digital converters (ADCs). Designed for exceptional dc accuracy, low noise, and robust capacitive load driving, this device is well suited for data acquisition systems where high precision is required along with the best signal-to-noise ratio (SNR) and spurious-free dynamic range (SFDR) through the amplifier and ADC combination.

The THS4552 features the negative rail input required when interfacing a dc-coupled, ground-centered, source signal to a single-supply differential input ADC. Very low dc error and drift terms support the emerging 16- to 20-bit successive-approximation register (SAR) input requirements. A wide-range output commonmode control supports the ADC running from 1.8 V to 5 V supplies with ADC common-mode input requirements from 0.7 V to greater than 3.0 V.

The THS4552 device is characterized for operation over the wide temperature range of -40°C to +125°C, and is available in 16-pin TSSOP and 24-pin VQFN packages.

#### Low-Power ADCs Supported by the THS4552<sup>(1)</sup>

| PART<br>NUMBER | ADC TYPE    | RESOLUTION, SPEED          |  |  |  |  |  |  |

|----------------|-------------|----------------------------|--|--|--|--|--|--|

| ADS1278        | Delta sigma | Octal, 24 bits, 0.512 MSPS |  |  |  |  |  |  |

| ADS8694        | SAR         | Quad, 18 bits, 0.5 MSPS    |  |  |  |  |  |  |

| ADC3221        | Pipeline    | Dual, 12 bits, 25 MSPS     |  |  |  |  |  |  |

| ADC3241        | Pipeline    | Dual, 14 bits, 25 MSPS     |  |  |  |  |  |  |

For all available packages, see the orderable addendum at the end of the datasheet.

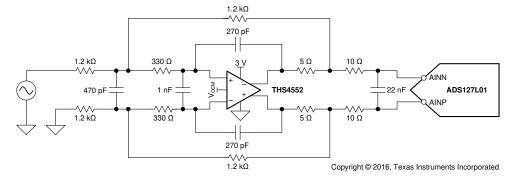

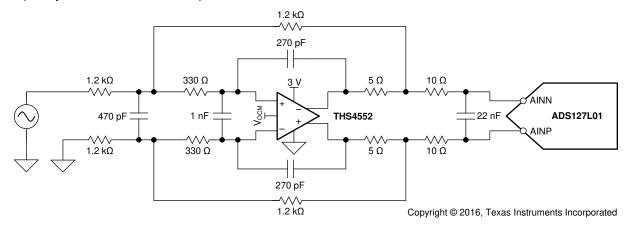

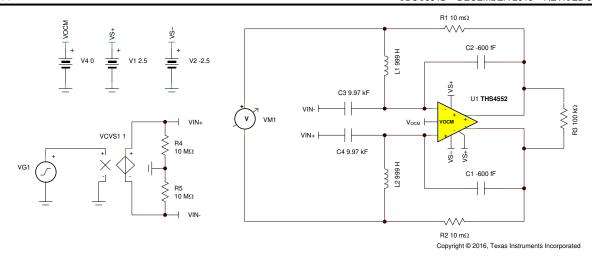

Simplified Schematic: Gain of 1-V/V, Single-Ended Input to Differential Output, 500-kHz, Multiple Feedback Filter Interface to the ADS127L01 (1 of 2 Channels)

### **Table of Contents**

| 1 Features1                                                  | 8 Detailed Description                                | .27  |

|--------------------------------------------------------------|-------------------------------------------------------|------|

| 2 Applications1                                              | 8.1 Overview                                          |      |

| B Description1                                               | 8.2 Functional Block Diagram                          | . 27 |

| 4 Revision History2                                          | 8.3 Feature Description                               | 28   |

| 5 Pin Configuration and Functions4                           | 8.4 Device Functional Modes                           | 36   |

| Specifications5                                              | 9 Application and Implementation                      | .41  |

| 6.1 Absolute Maximum Ratings5                                | 9.1 Application Information                           | . 41 |

| 6.2 ESD Ratings5                                             | 9.2 Typical Applications                              | . 50 |

| 6.3 Recommended Operating Conditions5                        | 10 Power Supply Recommendations                       | 56   |

| 6.4 Thermal Information6                                     | 10.1 Thermal Analysis                                 |      |

| 6.5 Electrical Characteristics: $(V_{S+}) - (V_{S-}) = 5 V6$ | 11 Layout                                             | . 57 |

| 6.6 Electrical Characteristics: $(V_{S+}) - (V_{S-}) = 3 V9$ | 11.1 Layout Guidelines                                | . 57 |

| 6.7 Typical Characteristics: $(V_{S+}) - (V_{S-}) = 5 V$     | 11.2 Layout Example                                   | . 58 |

| 6.8 Typical Characteristics: $(V_{S+}) - (V_{S-}) = 3 V$     | 11.3 EVM Board                                        | .59  |

| 6.9 Typical Characteristics: 3 V to 5 V Supply Range18       | 12 Device and Documentation Support                   | 60   |

| 7 Parameter Measurement Information22                        | 12.1 Device Support                                   |      |

| 7.1 Example Characterization Circuits22                      | 12.2 Documentation Support                            | . 62 |

| 7.2 Output Interface Circuit for DC-Coupled                  | 12.3 Receiving Notification of Documentation Updates. | .63  |

| Differential Testing24                                       | 12.4 Support Resources                                | . 63 |

| 7.3 Output Common-Mode Measurements24                        | 12.5 Trademarks                                       | .63  |

| 7.4 Differential Amplifier Noise Measurements25              | 12.6 Electrostatic Discharge Caution                  | .63  |

| 7.5 Balanced Split-Supply Versus Single-Supply               | 12.7 Glossary                                         | .63  |

| Characterization25                                           | 13 Mechanical, Packaging, and Orderable               |      |

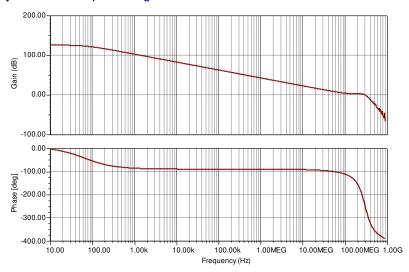

| 7.6 Simulated Characterization Curves25                      | Information                                           | . 63 |

| 7.7 Terminology and Application Assumptions26                |                                                       |      |

|                                                              |                                                       |      |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision A (July 2017) to Revision B (June 2021)                                                                                                                                                          | Page |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Updated the numbering format for tables, figures, and cross-references throughout the document  Removed the I <sub>IB</sub> input bias current (positive current out-of-node) minumum limits in the <i>Electrical</i> | 1    |

|   | Characteristics: $(V_{S+}) - (V_{S-}) = 5 \text{ V}$ section                                                                                                                                                          | 6    |

| • | Removed the $I_{IB}$ input bias current (positive current out-of-node) minumum limits in the <i>Electrical Characteristics:</i> $(V_{S+}) - (V_{S-}) = 3 \ V$ section                                                 | 9    |

| С | hanges from Revision * (December 2016) to Revision A (July 2017)                                                                                                                                                      | Page |

# **Device Family Comparison (Dual-Channel, Precision FDAs)**

| DEVICE  | BW, G = 1 (MHz) | I <sub>Q</sub> , 5 V<br>(mA/Ch) | INPUT NOISE<br>(nV/√ Hz) | THD (dBc) 2 V <sub>PP</sub><br>AT 10 kHz | RAIL-TO-RAIL     | SINGLE<br>VERSIONS |

|---------|-----------------|---------------------------------|--------------------------|------------------------------------------|------------------|--------------------|

| THS4552 | 150             | 1.37                            | 3.3                      | -138                                     | Negative in, out | THS4551            |

| THS4522 | 145             | 1.14                            | 5.6                      | -120                                     | Negative in, out | THS4521            |

| THS4532 | 36              | 0.25                            | 10                       | -118                                     | Negative in, out | THS4531A           |

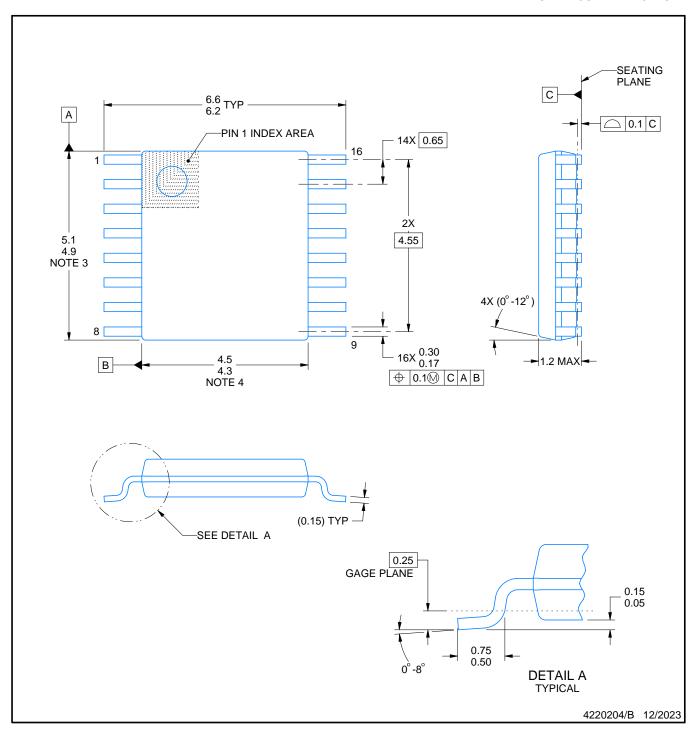

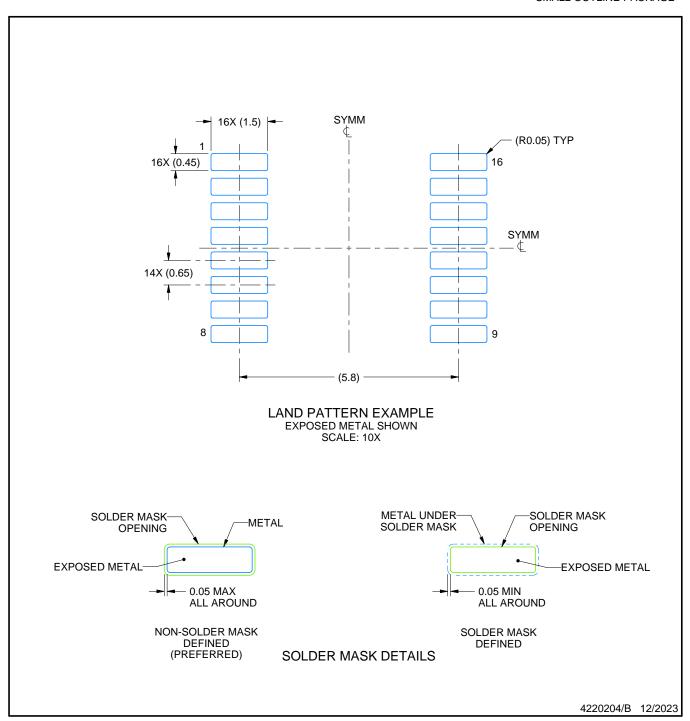

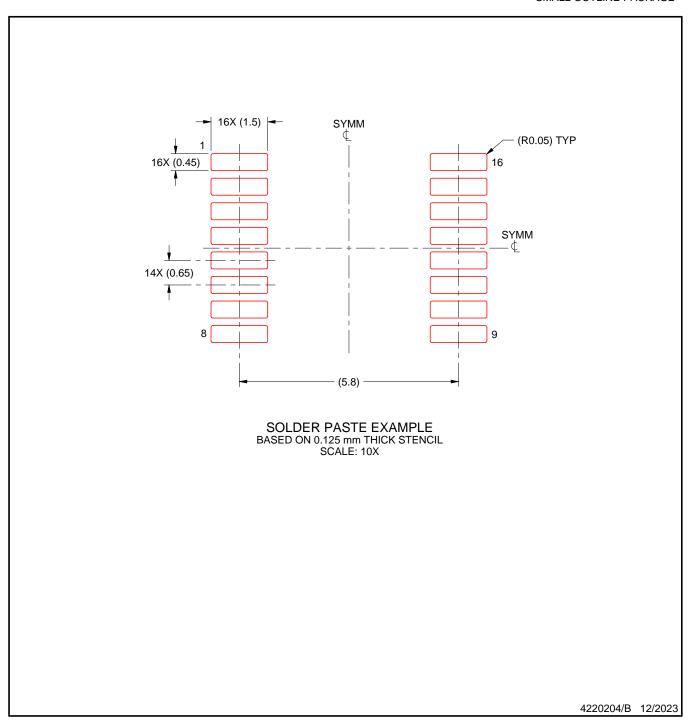

## **5 Pin Configuration and Functions**

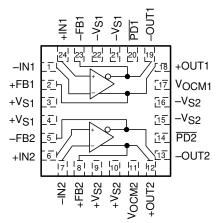

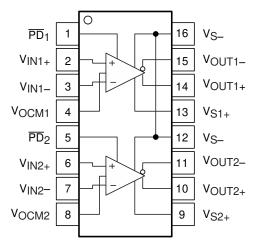

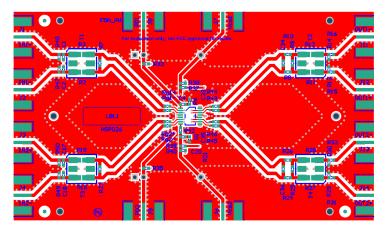

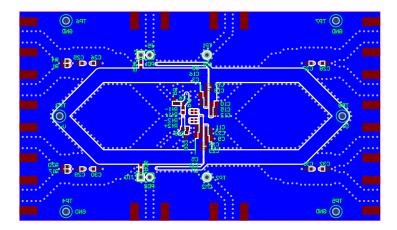

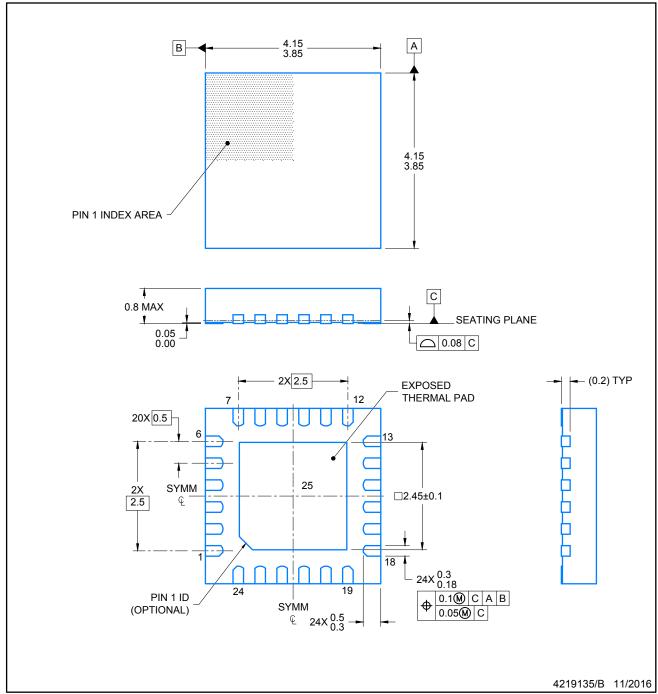

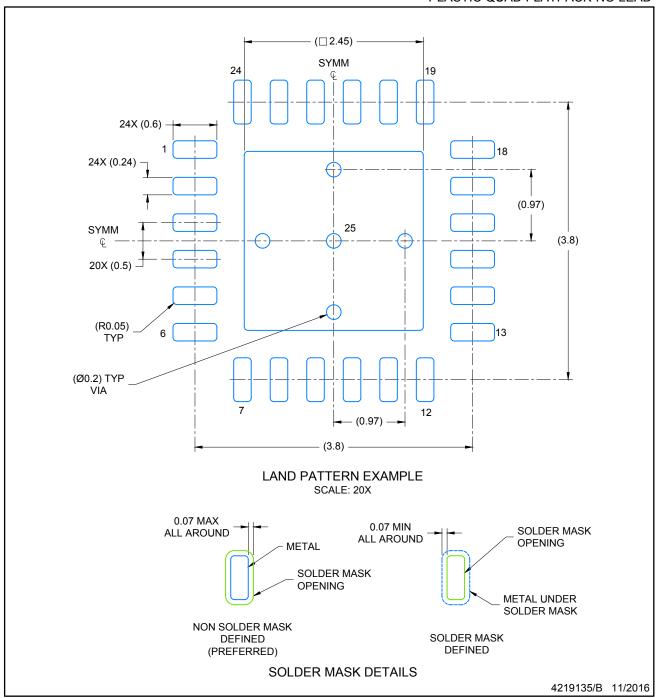

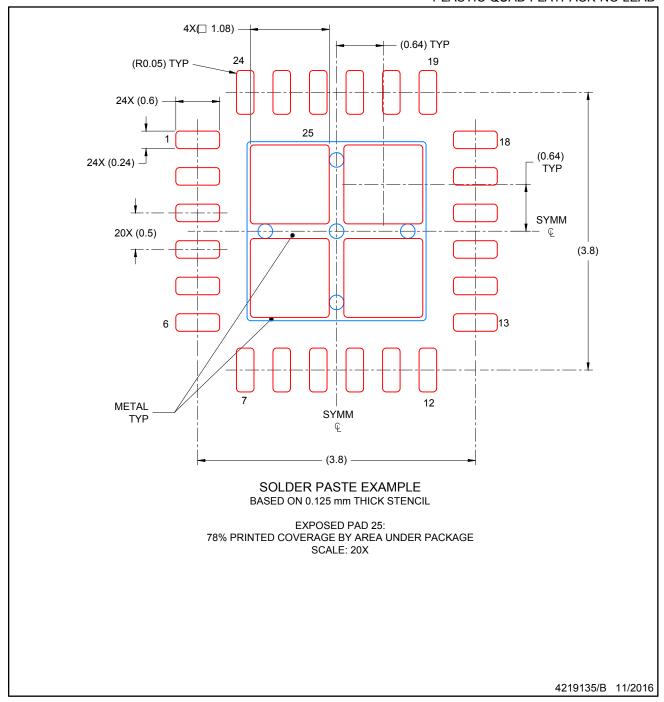

Figure 5-1. RTW Package 24-Pin VQFN With Exposed Thermal Pad Top View

Figure 5-2. PW Package 16-Pin VSSOP Top View

Table 5-1. Pin Functions

| PIN   |                    |    |     |                                                                                              |

|-------|--------------------|----|-----|----------------------------------------------------------------------------------------------|

| NAME  | N                  | 0. | 1/0 | DESCRIPTION                                                                                  |

| NAME  | RTW <sup>(1)</sup> | PW |     |                                                                                              |

| FB1-  | 23                 | _  | 0   | Channel 1, inverting (negative) output feedback                                              |

| FB2-  | 5                  | _  | 0   | Channel 2, inverting (negative) output feedback                                              |

| FB1+  | 2                  | _  | 0   | Channel 1, noninverting (positive) output feedback                                           |

| FB2+  | 8                  | _  | 0   | Channel 2, noninverting (positive) output feedback                                           |

| IN1-  | 1                  | 3  | I   | Channel 1, inverting (negative) amplifier input                                              |

| IN2-  | 7                  | 7  | I   | Channel 2, inverting (negative) amplifier input                                              |

| IN1+  | 24                 | 2  | I   | Channel 1, noninverting (positive) amplifier input                                           |

| IN2+  | 6                  | 6  | I   | Channel 2, noninverting (positive) amplifier input                                           |

| OUT1- | 19                 | 15 | 0   | Channel 1, inverting (negative) amplifier output                                             |

| OUT2- | 13                 | 11 | 0   | Channel 2, inverting (negative) amplifier output                                             |

| OUT1+ | 18                 | 14 | 0   | Channel 1, noninverting (positive) amplifier output                                          |

| OUT2+ | 12                 | 10 | 0   | Channel 2, noninverting (positive) amplifier output                                          |

| PD1   | 20                 | 1  | I   | Channel 1, power-down.  PD = logic low = power off mode; PD = logic high = normal operation. |

| PD2   | 14                 | 5  | I   | Channel 2, power-down.  PD = logic low = power off mode; PD = logic high = normal operation. |

| VOCM1 | 17                 | 4  | I   | Channel 1, common-mode voltage input                                                         |

| VOCM2 | 11                 | 8  | I   | Channel 2, common-mode voltage input                                                         |

| VS1-  | 21, 22             | 16 | I   | Channel 1, negative power-supply input                                                       |

| VS2-  | 15.16              | 12 | I   | Channel 2, negative power-supply input                                                       |

| VS1+  | 3,4                | 13 | I   | Channel 1, positive power-supply input                                                       |

| VS2+  | 9.10               | 9  | I   | Channel 2, positive power-supply input                                                       |

<sup>(1)</sup> Solder the exposed thermal pad (RTW package) to a heat-spreading power or ground plane. This pad is electrically isolated from the die, but must be connected to a power or ground plane and not floated.

Product Folder Links: THS4552

### 6 Specifications

### **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                         | MIN                                                                                                                    | MAX                      | UNIT |

|------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------|------|

| Voltage  Current | Supply voltage, (V <sub>S+</sub> ) – (V <sub>S</sub> –) | '                                                                                                                      | 5.5                      | V    |

|                  | Supply turn-on, turn-off maximum dV/dT <sup>(2)</sup>   |                                                                                                                        | 1                        | V/µs |

|                  | Input/output voltage range                              | (V <sub>S-</sub> ) - 0.5                                                                                               | (V <sub>S+</sub> ) + 0.5 | V    |

|                  | Differential input voltage                              |                                                                                                                        | ±1                       | V    |

|                  | Continuous input current                                |                                                                                                                        | ±10                      | A    |

| Current          | Continuous output current <sup>(3)</sup>                |                                                                                                                        | ±20                      | - mA |

| Odinom           | Continuous power dissipation                            | 5.5  (V <sub>S-</sub> ) - 0.5  (V <sub>S+</sub> ) + 0.5  ±1  ±10  ±20  See Section 6.4 and Section 10.1  150  -40  125 |                          |      |

|                  | Maximum junction                                        |                                                                                                                        | 150                      |      |

| Temperature      | Operating free-air, T <sub>A</sub>                      | -40                                                                                                                    | 125                      | °C   |

|                  | Storage, T <sub>stg</sub>                               | -65                                                                                                                    | 150                      | 1    |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Staying below this ± supply turn-on edge rate ensures that the edge-triggered ESD absorption device across the supply pins remains off

- (3) Long-term continuous current for electro-migration limits.

#### 6.2 ESD Ratings

|                    |                                            |                                                                                                                                                                   | VALUE | UNIT |  |  |  |  |

|--------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--|--|--|--|

| A. THS4            | A. THS4552 in PW Pacakges                  |                                                                                                                                                                   |       |      |  |  |  |  |

| V                  | V <sub>(ESD)</sub> Electrostatic discharge | tatic discharge  Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |       | V    |  |  |  |  |

| V(ESD)             |                                            |                                                                                                                                                                   |       | V    |  |  |  |  |

| B. THS4            | 552 in RTW Package                         |                                                                                                                                                                   |       |      |  |  |  |  |

| V                  | Clastrostatia diasharas                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> (3)                                                                                             | ±1000 | V    |  |  |  |  |

| V <sub>(ESD)</sub> | Electrostatic discharge                    | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup>                                                                                    | ±1250 | V    |  |  |  |  |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (3) ESD limit of ±1000 V for any pin to thermal pad. Pin-to-pin HBM ESD specifications are rated at ±2500 V.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                | MIN | NOM | MAX | UNIT |

|-----------------|--------------------------------|-----|-----|-----|------|

| V <sub>S+</sub> | Single-supply positive voltage | 2.7 | 5   | 5.4 | V    |

| $T_A$           | Ambient temperature            | -40 | 25  | 125 | °C   |

#### **6.4 Thermal Information**

|                        |                                              | THS                          | THS4552       |      |  |  |

|------------------------|----------------------------------------------|------------------------------|---------------|------|--|--|

|                        | THERMAL METRIC <sup>(1)</sup>                | RTW <sup>(2)</sup><br>(VQFN) | PW<br>(TSSOP) | UNIT |  |  |

|                        |                                              | 24 PINS                      | 16 PINS       |      |  |  |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 46.0                         | 117.2         | °C/W |  |  |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 34.6                         | 48.8          | °C/W |  |  |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 19.7                         | 70.2          | °C/W |  |  |

| ΨЈТ                    | Junction-to-top characterization parameter   | 10.0                         | 21.1          | °C/W |  |  |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 19.7                         | 69.8          | °C/W |  |  |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 12.9                         | N/A           | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics: $(V_{S+}) - (V_{S-}) = 5 \text{ V}$

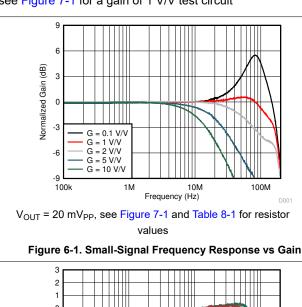

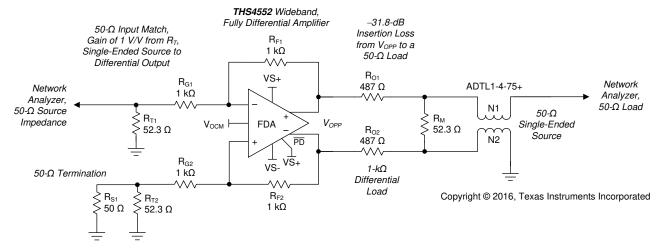

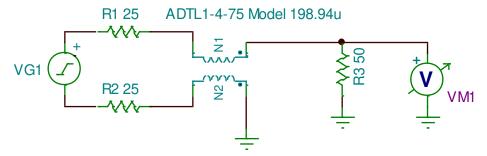

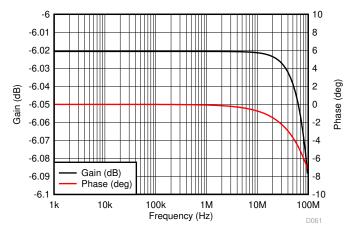

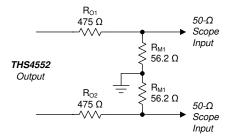

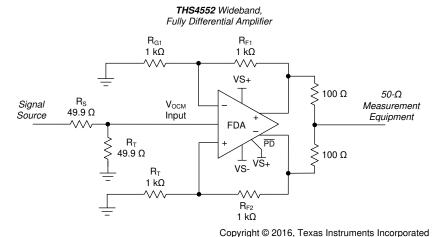

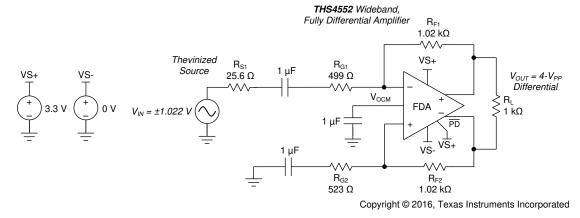

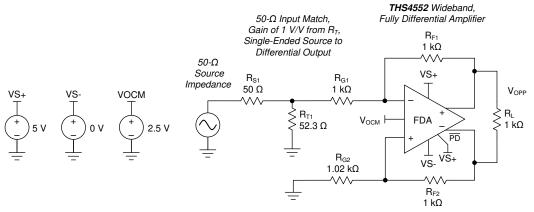

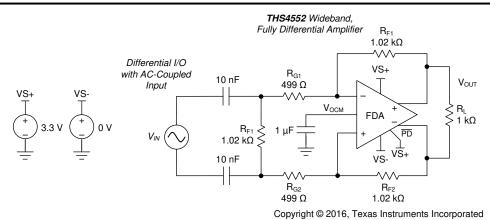

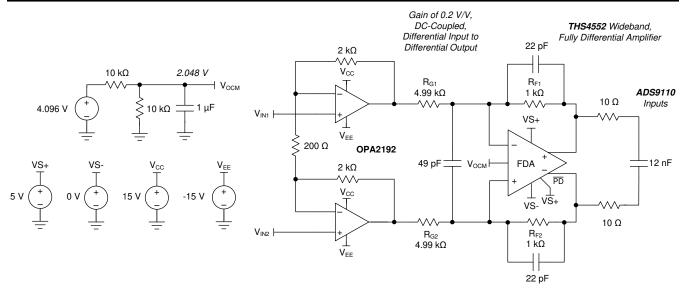

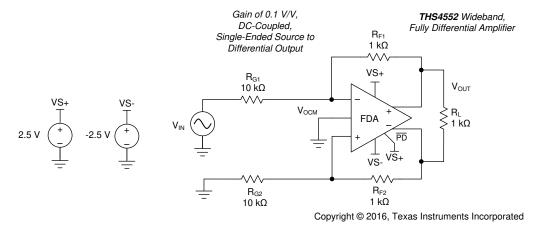

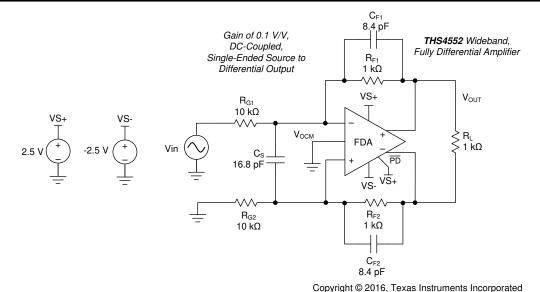

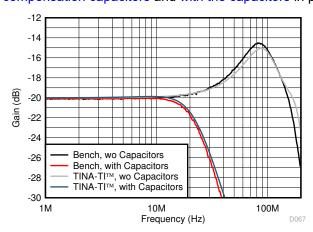

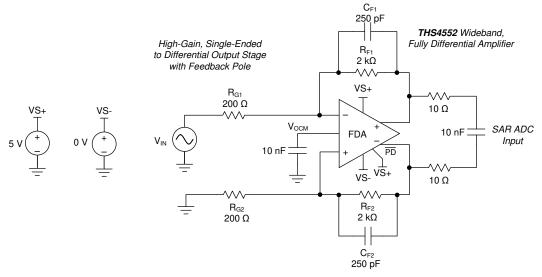

at  $T_A \approx 25^{\circ}$ C, VOCM pin = open,  $R_F = 1 \text{ k}\Omega$ ,  $R_L = 1 \text{ k}\Omega$ ,  $V_{OUT} = 2 \text{ V}_{PP}$ , 50  $\Omega$  input match, G = 1 V/V,  $\overline{PD} = V_{S+}$ , single-ended input, differential output, and input and output referenced to default midsupply for ac-coupled tests (unless otherwise noted); specifications are per channel; see Figure 7-1 for a gain of 1-V/V test circuit

|                                 | PARAMETER                                        | TEST CONDITIONS                                                            | MIN  | TYP   | MAX  | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|---------------------------------|--------------------------------------------------|----------------------------------------------------------------------------|------|-------|------|--------------------|------------------------------|

| AC PEF                          | RFORMANCE                                        |                                                                            |      |       |      |                    |                              |

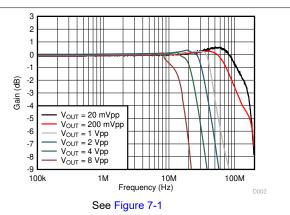

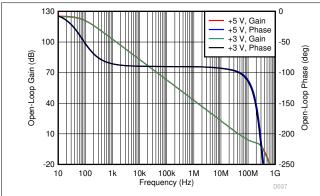

|                                 |                                                  | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 1, peaking (< 1.0 dB)         |      | 150   |      |                    | С                            |

| SSBW                            | Small-signal bandwidth                           | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 2                             |      | 75    |      | MHz                | С                            |

|                                 |                                                  | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 10                            |      | 15    |      |                    | С                            |

| GBP                             | Gain-bandwidth product                           | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 100                           |      | 135   |      | MHz                | С                            |

| LSBW                            | Large-signal bandwidth                           | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1                               |      | 37    |      | MHz                | С                            |

|                                 | Bandwidth for 0.1-dB flatness                    | V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1                               |      | 15    |      | MHz                | С                            |

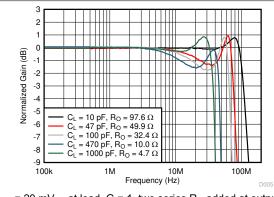

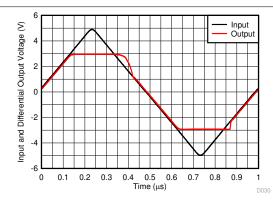

| SR                              | Slew rate <sup>(2)</sup>                         | $V_{OUT}$ = 4 $V_{PP}$ , full-power bandwidth (FPBW), $R_L$ = 1 $k\Omega$  |      | 220   |      | V/µs               | С                            |

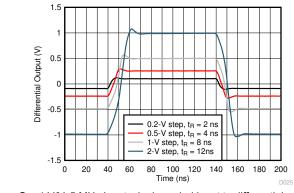

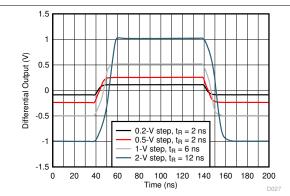

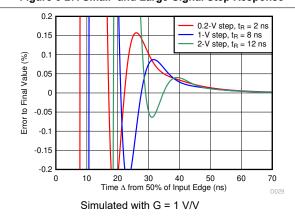

| t <sub>R</sub> , t <sub>F</sub> | Rise and fall time                               | V <sub>OUT</sub> = 0.5 V step, G = 1, input t <sub>R</sub> = 2 ns          |      | 6     |      | ns                 | С                            |

|                                 | 0 - 441: 4:                                      | To 0.1%, V <sub>OUT</sub> = 0.5 V step, input t <sub>R</sub> = 2 ns, G = 1 |      | 30    |      |                    | С                            |

| t <sub>SETTLE</sub>             | Settling time                                    | To 0.01%,V <sub>OUT</sub> = 0.5 V step, input t <sub>R</sub> = 2 ns, G = 1 |      | 50    |      | ns                 | С                            |

|                                 | Overshoot and undershoot                         | V <sub>OUT</sub> = 0.5 V step G = 1, input t <sub>R</sub> = 2 ns           |      | 8%    |      |                    | С                            |

| LIDO                            | Second-order harmonic distortion                 | $f$ = 100 kHz, $V_{OUT}$ = 2 $V_{PP}$ , $G$ = 1, $R_{L}$ = 1 kΩ            | -128 |       | -ID- | С                  |                              |

| HD2                             |                                                  | $f$ = 100 kHz, $V_{OUT}$ = 8 $V_{PP}$ , $G$ = 1, $R_{L}$ = 1 kΩ            |      | -124  |      | dBc                | С                            |

| LIDO                            | T                                                | $f$ = 100 kHz, $V_{OUT}$ = 2 $V_{PP}$ , $G$ = 1, $R_{L}$ = 1 kΩ            | -139 |       |      | -ID-               | С                            |

| HD3                             | Third-order harmonic distortion                  | $f = 100 \text{ kHz}, V_{OUT} = 8 V_{PP}, G = 1, R_L = 1 \text{ k}\Omega$  | -131 |       |      | - dBc              | С                            |

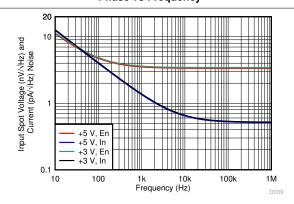

|                                 | Input voltage noise                              | f > 500 Hz, 1/f < 150 Hz                                                   |      | 3.3   |      | nV/√ <del>Hz</del> | С                            |

|                                 | Input current noise                              | f > 20 kHz, 1/f <10 kHz                                                    |      | 0.5   |      | pA/√ <del>Hz</del> | С                            |

|                                 | Overdrive recovery time                          | G = 2, 2X output overdrive, dc coupled                                     |      | 50    |      | ns                 | С                            |

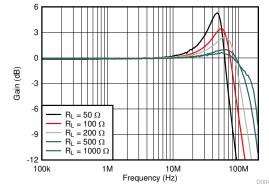

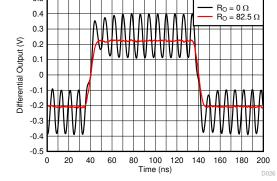

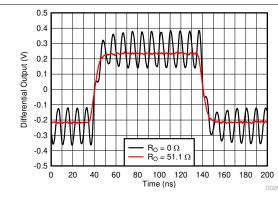

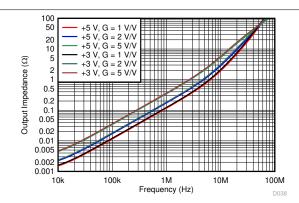

|                                 | Closed-loop output impedance                     | f = 100 kHz (differential), G = 1                                          |      | 0.02  |      | Ω                  | С                            |

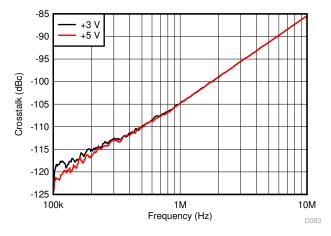

|                                 | Channel-to-channel crosstalk                     | 2 V <sub>PP</sub> output on one channel, 1 MHz                             |      | -80   |      | dBc                | С                            |

| DC PEF                          | RFORMANCE <sup>(5)</sup>                         |                                                                            |      | -     |      |                    |                              |

| A <sub>OL</sub>                 | Open-loop voltage gain                           | ±3 V differential-to-differential, 1 kΩ load                               | 105  | 125   |      | dB                 | А                            |

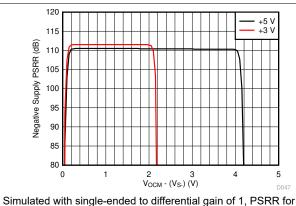

|                                 |                                                  | T <sub>A</sub> = 25°C                                                      | -175 | ±50   | 175  |                    | Α                            |

| .,                              | tt                                               | $T_A = 0$ °C to +70°C                                                      | -225 |       | 265  | μV                 | В                            |

| $V_{IO}$                        | Input-referred offset voltage                    | $T_A = -40$ °C to +85°C                                                    | -295 | ,     | 295  |                    | В                            |

|                                 |                                                  | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                       | -295 | ,     | 375  |                    | В                            |

|                                 | Input offset voltage drift(3)                    | T <sub>A</sub> = -40°C to +125°C (PW package)                              | -2.0 | ±0.45 | 2.0  | μV/°C              | В                            |

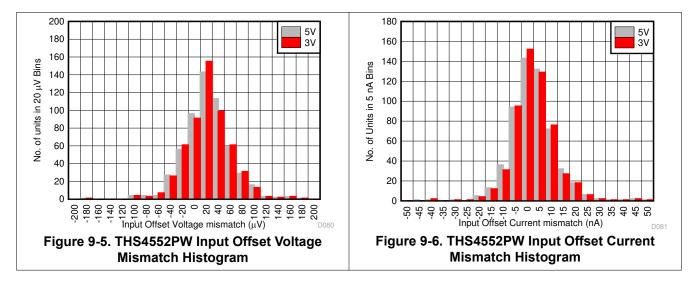

|                                 | Channel-to-channel input offset voltage mismatch | T <sub>A</sub> = 25°C (PW package)                                         | -250 |       | 250  | μV                 | А                            |

Product Folder Links: THS4552

<sup>(2)</sup> Thermal impedance for RTW reported with backside thermal pad soldered to heat spreading plane.

# 6.5 Electrical Characteristics: $(V_{S+}) - (V_{S-}) = 5 \text{ V (continued)}$

at  $T_A \approx 25^{\circ}$ C, VOCM pin = open,  $R_F = 1 \text{ k}\Omega$ ,  $R_L = 1 \text{ k}\Omega$ ,  $V_{OUT} = 2 \text{ V}_{PP}$ , 50  $\Omega$  input match, G = 1 V/V,  $\overline{PD} = V_{S+}$ , single-ended input, differential output, and input and output referenced to default midsupply for ac-coupled tests (unless otherwise noted); specifications are per channel; see Figure 7-1 for a gain of 1-V/V test circuit

|                                       | PARAMETER                                              | TEST CO                                                                          | NDITIONS                                             | MIN                          | TYP                      | MAX                       | UNIT     | TEST<br>LEVEL <sup>(</sup> |

|---------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------|------------------------------|--------------------------|---------------------------|----------|----------------------------|

|                                       | Input offset voltage drift mismatch                    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C (PV)}$                        | V package)                                           | -2.7                         |                          | 2.7                       | μV/°C    | В                          |

|                                       |                                                        | T <sub>A</sub> = 25°C                                                            |                                                      |                              | 1.0                      | 1.5                       |          | Α                          |

|                                       | Input bias current                                     | T <sub>A</sub> = 0°C to +70°C                                                    |                                                      |                              |                          | 1.73                      |          | В                          |

| IB                                    | (positive current out-of-node)                         | T <sub>A</sub> = -40°C to +85°C                                                  |                                                      |                              |                          | 1.80                      | μΑ       | В                          |

|                                       |                                                        | T <sub>A</sub> = -40°C to +125°C                                                 |                                                      |                              | 2.0                      |                           | В        |                            |

|                                       | Input bias current drift <sup>(3)</sup>                | T <sub>A</sub> = -40°C to +125°C                                                 |                                                      | 2                            | 3.3                      | 5.0                       | nA/°C    | В                          |

| C PER                                 | FORMANCE (continued)                                   |                                                                                  |                                                      |                              |                          |                           |          |                            |

|                                       |                                                        | T <sub>A</sub> = 25°C                                                            |                                                      | -50                          | ±10                      | 50                        |          | Α                          |

| os                                    | Input offset current                                   | $T_A = 0$ °C to +70°C                                                            |                                                      | -57                          |                          | 63                        | nA       | В                          |

|                                       | input onset ourrent                                    | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                              |                                                      | -68                          |                          | 67                        | 117 (    | В                          |

|                                       |                                                        | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                             |                                                      | -68                          |                          | 78                        |          | В                          |

|                                       | Input offset current mismatch                          | T <sub>A</sub> = 25°C                                                            |                                                      | -65                          |                          | 65                        | nA       | D                          |

|                                       | Input offset current drift <sup>(3)</sup>              | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C (PV)}$                        | V package)                                           | -240                         | ±20                      | 240                       | pA/°C    | В                          |

|                                       | Offset current drift mismatch                          | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C (PV)}$                        | V package)                                           | -260                         | ±20                      | 260                       | pA/°C    | В                          |

| NPUT                                  |                                                        |                                                                                  |                                                      |                              |                          |                           |          |                            |

|                                       | Common-mode input, low                                 | > 90 dB CMRR at input                                                            | T <sub>A</sub> = 25°C                                |                              | $(V_{S-}) - 0.2$         | $(V_{S-}) - 0.1$          | V        | Α                          |

|                                       |                                                        | range limits                                                                     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                              | $(V_{S-}) - 0.1$         | V <sub>S-</sub>           | •        | В                          |

|                                       | Common-mode input, high                                | > 90-dB CMRR at input                                                            | T <sub>A</sub> = 25°C                                | (V <sub>S+</sub> ) – 1.2     | (V <sub>S+</sub> ) – 1.1 |                           | V        | Α                          |

|                                       |                                                        | range limits                                                                     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | $(V_{S+}) - 1.3$             | (V <sub>S+</sub> ) – 1.2 |                           | •        | В                          |

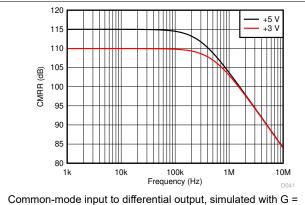

| MRR                                   | Common-mode rejection ratio                            | Input pins at $[(V_{S+}) - (V_{S-})]$                                            | ]/2                                                  | 93                           | 110                      |                           | dB       | Α                          |

|                                       | Input impedance differential mode                      | Input pins at $[(V_{S+}) - (V_{S-})]$                                            | ]/2                                                  |                              | 100    1.2               |                           | kΩ    pF | С                          |

| OUTPU                                 | Т                                                      |                                                                                  |                                                      |                              |                          |                           |          |                            |

|                                       | Output voltage, low                                    | T <sub>A</sub> = 25°C                                                            |                                                      |                              | (V <sub>S-</sub> ) + 0.2 | (V <sub>S-</sub> ) + 0.23 | V        | А                          |

|                                       |                                                        | T <sub>A</sub> = -40°C to +125°C                                                 |                                                      |                              | (V <sub>S-</sub> ) + 0.2 | (V <sub>S</sub> _) + 0.22 |          | В                          |

|                                       | Output voltage, high                                   | T <sub>A</sub> = 25°C                                                            |                                                      | (V <sub>S+</sub> ) –<br>0.23 | (V <sub>S+</sub> ) - 0.2 |                           | V        | А                          |

|                                       | - Capat totage, mg.                                    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                             |                                                      | (V <sub>S+</sub> ) –<br>0.22 | (V <sub>S+</sub> ) - 0.2 |                           |          | В                          |

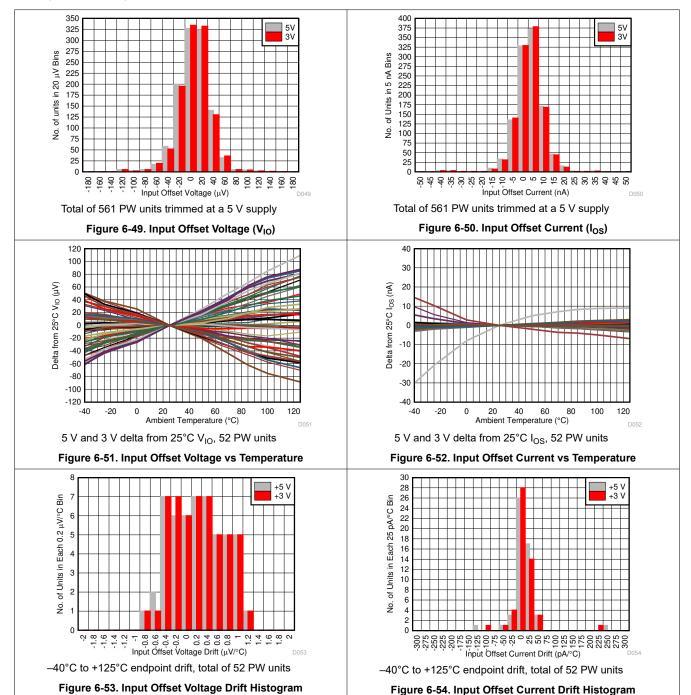

|                                       | Continuous output current                              | $T_A = 25$ °C, ±2.5 V, $R_L = 40$<br>V <sub>OCM</sub> offset < ±20 mV            | •                                                    | ±60                          | ±65                      |                           | mA       | А                          |

|                                       | <u>.</u>                                               | $T_A$ = -40°C to +125°C, ±2.1 V, $R_L$ = 40 $\Omega$ , $V_{OCM}$ offset < ±20 mV |                                                      | ±50                          |                          |                           |          | В                          |

|                                       | Linear output current                                  | $T_A = 25^{\circ}C, \pm 2.1 \text{ V, } R_L = 50$                                |                                                      | ±40                          | ±45                      |                           | m^       | Α                          |

|                                       | Linear output current                                  | $T_A = -40$ °C to +125°C, ±1.<br>$A_{OL} > 80 \text{ dB}$                        | 6 V, R <sub>L</sub> = 50 Ω,                          | ±30                          |                          |                           | mA       | В                          |

| OWER                                  | SUPPLY                                                 |                                                                                  |                                                      |                              |                          |                           |          |                            |

|                                       | Specified operating voltage                            |                                                                                  |                                                      | 2.7                          | 5                        | 5.4                       | V        | В                          |

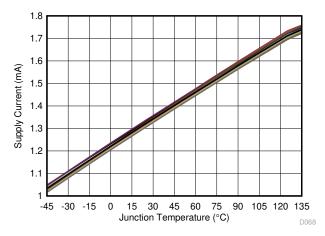

| Q                                     | Quiescent operating current per                        | $T_A \approx 25^{\circ}C^{(6)}, V_{S+} = 5 V$                                    |                                                      | 1.28                         | 1.37                     | 1.44                      | mA       | Α                          |

| · · · · · · · · · · · · · · · · · · · | channel                                                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, V_S$                        | <sub>+</sub> = 5 V                                   | 0.97                         |                          | 1.92                      |          | В                          |

|                                       | Supply current at maximum operating supply per channel | $T_A = 25^{\circ}C, V_{S+} = 5.4 \text{ V}$                                      |                                                      | 1.33                         | 1.36                     | 1.46                      | mA       | D                          |

| II <sub>Q</sub> /dT                   | Quiescent current temperature coefficient per channel  | V <sub>S+</sub> = 5 V                                                            |                                                      | 2.4                          | 3.9                      | 5.4                       | μΑ/°C    | В                          |

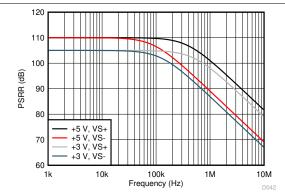

| PSRR                                  | Power-supply rejection ratio                           | Either supply pin to differe                                                     | ntial V <sub>OUT</sub>                               | 93                           | 110                      |                           | dB       | Α                          |

| OWER                                  | R-DOWN                                                 |                                                                                  |                                                      |                              |                          |                           |          |                            |

|                                       | Enable voltage threshold                               | Specified on above (V <sub>S-</sub> ) -                                          | + 1.15 V                                             | (V <sub>S</sub> _) + 1.15    |                          |                           | V        | Α                          |

|                                       | Disable voltage threshold                              | Specified off below (V <sub>S</sub> _) +                                         | 0.55 V                                               |                              |                          | (V <sub>S</sub> _) + 0.55 | V        | Α                          |

## 6.5 Electrical Characteristics: $(V_{S+}) - (V_{S-}) = 5 \text{ V}$ (continued)

at  $T_A \approx 25^{\circ}$ C, VOCM pin = open,  $R_F = 1 \text{ k}\Omega$ ,  $R_L = 1 \text{ k}\Omega$ ,  $V_{OUT} = 2 \text{ V}_{PP}$ , 50  $\Omega$  input match, G = 1 V/V,  $\overline{PD} = V_{S+}$ , single-ended input, differential output, and input and output referenced to default midsupply for ac-coupled tests (unless otherwise noted); specifications are per channel; see Figure 7-1 for a gain of 1-V/V test circuit

|                    | PARAMETER                                                                       |          | TEST CON                                                                 | IDITIONS                                                                | MIN   | TYP      | MAX   | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|--------------------|---------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|-------------------------------------------------------------------------|-------|----------|-------|--------------------|------------------------------|

|                    | Disable pin bias current                                                        |          | $\overline{PD} = V_{S-} \rightarrow V_{S+}$                              |                                                                         | -100  | ±10      | 100   | nA                 | Α                            |

|                    | Power-down guiescent                                                            | ourront  | Disable logic at (V <sub>S</sub> _) + 0.5                                | 5 V                                                                     | -2    | 1        | 5     |                    | Α                            |

|                    | Fower-down quiescent                                                            | Juneni   | Disable logic at (V <sub>S</sub> _)                                      |                                                                         | -2    | 1        | 5     | μA                 | Α                            |

| ton                | Turn-on time delay                                                              |          | Time from PD = low to V <sub>OU</sub>                                    | T = 90% of final value                                                  |       | 700      |       | ns                 | С                            |

| toff               | Turn-off time delay                                                             |          | Time from PD = low to V <sub>OU</sub>                                    | ime from $\overline{PD}$ = low to V <sub>OUT</sub> = 10% of final value |       |          |       | ns                 | С                            |

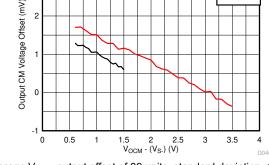

| OUTPU              | COMMON-MODE VOL                                                                 | TAGE (Vo | <sub>CM</sub> ) CONTROL <sup>(4)</sup> (see Figure                       | · 7-5)                                                                  |       |          |       |                    |                              |

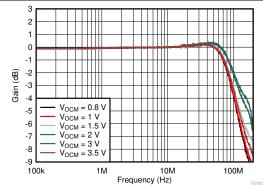

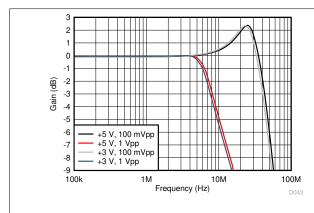

| SSBW               | Small-signal bandwidth                                                          |          | V <sub>OCM</sub> = 100 mV <sub>PP</sub> at the co                        | ontrol pin                                                              |       | 40       |       | MHz                | С                            |

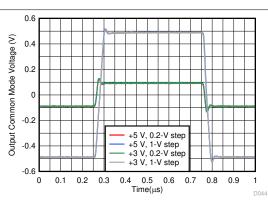

| _SBW               | Large-signal bandwidth                                                          |          | V <sub>OCM</sub> = 1 V <sub>PP</sub> at the contro                       | l pin                                                                   |       | 8        |       | MHz                | С                            |

| SR                 | Slew rate <sup>(2)</sup>                                                        |          | From 1-V <sub>PP</sub> LSBW                                              |                                                                         |       | 18       |       | V/µs               | С                            |

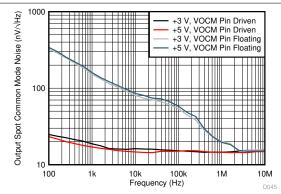

|                    | Output common-mode r<br>(≥ 2 kHz)                                               | ioise    | VOCM pin driven from low                                                 | impedance                                                               |       | 15       |       | nV/√ <del>Hz</del> | С                            |

|                    | Gain                                                                            |          | VOCM control pin input to (see Figure 7-5)                               | output average voltage                                                  | 0.997 | 0.999    | 1.001 | V/V                | А                            |

|                    | Input bias current                                                              |          |                                                                          |                                                                         | -100  | ±10      | 100   | nA                 | Α                            |

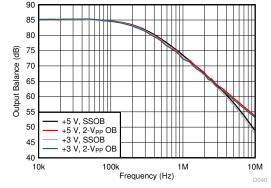

|                    | DC output balance (differential mode to common-mode output)                     |          | V <sub>OUT</sub> = ±1 V                                                  |                                                                         |       | 85       |       | dB                 | С                            |

|                    |                                                                                 | SSBW     | V <sub>OUT</sub> = 100 mV <sub>PP</sub> (output b<br>the 85-dB dc level) | palance drops –3 dB from                                                |       | 300      |       |                    | С                            |

|                    | Output balance                                                                  | LSBW     | V <sub>OUT</sub> = 2 V <sub>PP</sub> (output balan<br>85-dB dc level)    |                                                                         | 300   |          | kHz - | С                  |                              |

|                    | Input impedance<br>(VOCM pin input)                                             |          |                                                                          |                                                                         |       | 150    7 |       | kΩ    pF           | С                            |

|                    | Default voltage offset from $[(V_{S+}) - (V_{S-})] / 2$                         |          | VOCM pin open                                                            |                                                                         | -15   | ±2       | 15    | mV                 | Α                            |

|                    | Default voltage offset drift from $[(V_{S+}) - (V_{S-})] / 2$                   |          | T <sub>A</sub> = -40°C to +125°C                                         |                                                                         | 15    | 35       | 55    | μΑ/°C              | В                            |

|                    |                                                                                 |          |                                                                          | T <sub>A</sub> = 25°C                                                   | -5.0  | ±1       | 5.0   | mV                 | Α                            |

|                    |                                                                                 |          | VOCM pin driven to [(V <sub>S+</sub> ) – (V <sub>S-</sub> )] / 2         | $T_A = 0$ °C to +70°C                                                   | -5.25 |          | 5.5   |                    | В                            |

| CM V <sub>OS</sub> | Common-mode offset vo                                                           | oltage   |                                                                          | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                     | -5.7  |          | 5.6   |                    | В                            |

|                    |                                                                                 |          |                                                                          | T <sub>A</sub> = -40°C to +125°C                                        | -5.7  |          | 6.0   |                    | В                            |

|                    | Common-mode offset vo                                                           | oltage   | T <sub>A</sub> = -40°C to +125°C                                         |                                                                         | -10   | ±2       | 10    | μV/°C              | В                            |

|                    | Common-mode headroo<br>negative supply –PSRR<br>(supply to V <sub>OD</sub> )    |          | -PSRR > 80 dB                                                            |                                                                         |       |          | 0.55  | V                  | D                            |

|                    |                                                                                 |          |                                                                          | T <sub>A</sub> = 25°C                                                   |       |          | 0.55  |                    | А                            |

|                    | Common-mode loop sup                                                            | vlac     | < ±15 mV shift from                                                      | T <sub>A</sub> = 0°C to +70°C                                           |       |          | 0.6   |                    | В                            |

|                    | headroom to negative s                                                          |          | midsupply CM V <sub>OS</sub>                                             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                     |       |          | 0.65  | V                  | В                            |

|                    |                                                                                 |          |                                                                          | T <sub>A</sub> = -40°C to +125°C                                        |       |          | 0.7   |                    | В                            |

|                    | Common-mode headroom to positive supply +PSRR test (supply to V <sub>OD</sub> ) |          | +PSRR > 80 dB                                                            |                                                                         |       |          | 1.2   | ٧                  | D                            |

|                    |                                                                                 |          |                                                                          | T <sub>A</sub> = 25°C                                                   |       |          | 1.2   |                    | А                            |

|                    | Common-mode loop sup                                                            | vlac     | < ±15 mV shift from mid-                                                 | T <sub>A</sub> = 0°C to 70°C                                            |       |          | 1.25  |                    | В                            |

|                    | headroom to positive su                                                         | ' '''    |                                                                          | T <sub>A</sub> = -40°C to +85°C                                         |       |          | 1.3   | V                  | В                            |

|                    |                                                                                 |          |                                                                          | T <sub>A</sub> = -40°C to +125°C                                        |       |          | 1.3   |                    | В                            |

<sup>(1)</sup> Test levels (all values set by characterization and simulation): (A) 100% tested at T<sub>A</sub> ≈ 25°C. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

Product Folder Links: THS4552

<sup>(2)</sup> This slew rate is the average of the rising and falling time estimated from the sinusoidal large-signal bandwidth as: (V<sub>P</sub> / √ 2) × 2π × f<sub>-3dB</sub>.

<sup>(3)</sup> Input offset voltage drift, input bias current drift, and input offset current drift are the mean ±1-sigma values calculated by taking measurements at the maximum-range ambient temperature end points, computing the difference, and dividing by the temperature

www.ti.com

- range. Maximum drift specifications are set by mean ±4 σ on the device distributions tested over a –40°C to +125°C ambient temperature range. Drift is not specified by final ATE testing or QA sample test.

- (4) Specifications are from the input VOCM pin to the differential output average voltage.

- Currents out of pin are treated as a positive polarity (with the exception of the power-supply pins).

- T<sub>A</sub> = 25°C and I<sub>CC</sub> ≈ 1.37 mA. The test limit is expanded for the ATE ambient range of 22°C to 32°C with a 4 μA/°C I<sub>CC</sub> temperature coefficient considered; see Figure 10-1.

### 6.6 Electrical Characteristics: $(V_{S+}) - (V_{S-}) = 3 \text{ V}$

at  $T_A \approx 25^{\circ}\text{C}$ , VOCM pin = open,  $R_F = 1 \text{ k}\Omega$ ,  $R_L = 1 \text{ k}\Omega$ ,  $V_{OUT} = 2 \text{ V}_{PP}$ , 50  $\Omega$  input match, G = 1 V/V,  $\overline{PD} = V_{S+}$ , single-ended input, differential output, and input and output referenced to default midsupply for ac-coupled tests (unless otherwise noted); specifications are per channel; see Figure 7-1 for a gain of 1-V/V test circuit

|                                 | PARAMETER                                         | TEST CONDITIONS                                                                  | MIN  | TYP          | MAX | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|---------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------|------|--------------|-----|--------------------|------------------------------|

| AC PER                          | FORMANCE                                          |                                                                                  |      |              |     |                    |                              |

|                                 |                                                   | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 1, peaking (< 1.0 dB)               |      | 150          |     | MHz                | С                            |

| SSBW                            | Small-signal bandwidth                            | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 2                                   |      | 80           |     |                    | С                            |

|                                 |                                                   | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 10                                  |      | 14           |     |                    | С                            |

| GPB                             | Gain-bandwidth product                            | V <sub>OUT</sub> = 20 mV <sub>PP</sub> , G = 100                                 |      | 130          |     | MHz                | С                            |

| LSBW                            | Large-signal bandwidth                            | V <sub>OUT</sub> = 1 V <sub>PP</sub> , G = 1                                     | 45   |              | MHz | С                  |                              |

|                                 | Bandwidth for 0.1-dB flatness                     | V <sub>OUT</sub> = 1 V <sub>PP</sub> , G = 1                                     |      | 14           |     | MHz                | С                            |

| SR                              | Slew rate <sup>(2)</sup>                          | V <sub>OUT</sub> = 1 V <sub>PP</sub> , FPBW, G = 1                               |      | 110          |     | V/µs               | С                            |

| t <sub>R</sub> , t <sub>F</sub> | Rise and fall time                                | V <sub>OUT</sub> = 0.5 V step, G = 1, input t <sub>R</sub> = 4 ns                |      | 7.0          |     | ns                 | С                            |

|                                 | 0-44:                                             | To 0.1%, V <sub>OUT</sub> = 0.5 V step, input t <sub>R</sub> = 4 ns, G = 1       |      | 35           |     |                    | С                            |

| t <sub>SETTLE</sub>             | Settling time                                     | To 0.01%, V <sub>OUT</sub> = 0.5 V step, input t <sub>R</sub> = 4 ns, G = 1      |      | 55           |     | ns                 | С                            |

|                                 | Overshoot and undershoot                          | V <sub>OUT</sub> = 0.5 V step, G = 1, input t <sub>R</sub> = 4 ns                |      | 7%           |     |                    | С                            |

| HD2                             | 0                                                 | f = 100 kHz, V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1, R <sub>L</sub> = 1 kΩ |      | -128         |     | dBc -              | С                            |

|                                 | Second-order harmonic distortion                  | f = 100 kHz, V <sub>OUT</sub> = 4 V <sub>PP</sub> , G = 1, R <sub>L</sub> = 1 kΩ |      | -127         |     |                    | С                            |

| LIDO                            | Third-order harmonic distortion                   | f = 100 kHz, V <sub>OUT</sub> = 2 V <sub>PP</sub> , G = 1, R <sub>L</sub> = 1 kΩ | -139 |              |     | dBc                | С                            |

| HD3                             |                                                   | f = 100 kHz, V <sub>OUT</sub> = 4 V <sub>PP</sub> , G = 1, R <sub>L</sub> = 1 kΩ |      | -125         |     | ubc                | С                            |

|                                 | Input voltage noise                               | f > 500 Hz, 1/f < 150 Hz                                                         |      | 3.4          |     | nV/√ <del>Hz</del> | С                            |

|                                 | Input current noise                               | f > 20 kHz, 1/f < 10 kHz                                                         |      | 0.5          |     | pA/√ <del>Hz</del> | С                            |

|                                 | Overdrive recovery time                           | G = 2, 2X output overdrive, dc coupled                                           |      | 100          |     | ns                 | С                            |

|                                 | Closed-loop output impedance                      | f = 100 kHz (differential), G = 1                                                |      | 0.02         |     | Ω                  | С                            |

|                                 | Channel-to-channel crosstalk                      | 2-V <sub>PP</sub> output on one channel, 1 MHz                                   |      | -80          |     | dBc                | С                            |

| DC PER                          | FORMANCE <sup>(5)</sup>                           |                                                                                  |      |              |     |                    |                              |

| A <sub>OL</sub>                 | Open-loop voltage gain                            | ±2 V differential to 1 kΩ differential load                                      | 100  | 120          |     | dB                 | А                            |

|                                 | Input-referred offset voltage                     | T <sub>A</sub> = 25°C                                                            | -175 | ±40          | 175 |                    | Α                            |

| V                               |                                                   | $T_A = 0$ °C to +70°C                                                            | -225 |              | 265 | /                  | В                            |

| $V_{IO}$                        |                                                   | $T_A = -40$ °C to +85°C                                                          | -295 |              | 295 | μV                 | В                            |

|                                 |                                                   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                   | -295 |              | 375 |                    | В                            |

|                                 | Input offset voltage drift <sup>(3)</sup>         | T <sub>A</sub> = -40°C to +125°C (PW package)                                    | -2.0 | ±0.45        | 2.0 | μV/°C              | В                            |

|                                 | Channel-to-channel input offset voltage mismatch  | T <sub>A</sub> = 25°C (PW package)                                               | -250 |              | 250 | μV                 | А                            |

|                                 | Input offset voltage drift mismatch               | T <sub>A</sub> = -40°C to +125°C (PW package)                                    | -2.6 |              | 2.6 | μV/°C              | В                            |

|                                 |                                                   | T <sub>A</sub> = 25°C                                                            |      | 1.0          | 1.5 |                    | Α                            |

| L                               | Input bias current (positive current out-of-node) | T <sub>A</sub> = 0°C to +70°C                                                    |      | 1.73<br>1.80 |     |                    | В                            |

| I <sub>IB</sub>                 |                                                   | T <sub>A</sub> = -40°C to +85°C                                                  |      |              |     | μA                 | В                            |

|                                 |                                                   | T <sub>A</sub> = -40°C to +125°C                                                 |      |              | 2.0 |                    | В                            |

|                                 | Input bias current drift <sup>(3)</sup>           | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                             | 2    | 3.3          | 5.5 | nA/°C              | В                            |

Copyright © 2021 Texas Instruments Incorporated

# 6.6 Electrical Characteristics: $(V_{S+}) - (V_{S-}) = 3 \text{ V (continued)}$

at  $T_A \approx 25^{\circ}$ C, VOCM pin = open,  $R_F = 1 \text{ k}\Omega$ ,  $R_L = 1 \text{ k}\Omega$ ,  $V_{OUT} = 2 \text{ V}_{PP}$ , 50  $\Omega$  input match, G = 1 V/V,  $\overline{PD} = V_{S+}$ , single-ended input, differential output, and input and output referenced to default midsupply for ac-coupled tests (unless otherwise noted); specifications are per channel; see Figure 7-1 for a gain of 1-V/V test circuit

|                     | PARAMETER                                              | TEST CONDITIONS                                                                      |                                                      | MIN                          | TYP                      | MAX                       | UNIT     | TEST<br>LEVEL <sup>(1)</sup> |

|---------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------|--------------------------|---------------------------|----------|------------------------------|

| DC PER              | FORMANCE (continued)                                   |                                                                                      |                                                      |                              |                          |                           |          |                              |

|                     |                                                        | T <sub>A</sub> = 25°C                                                                |                                                      | -50                          | ±10                      | 50                        |          | А                            |

|                     |                                                        | T <sub>A</sub> = 0°C to +70°C                                                        |                                                      | -57                          |                          | 63                        |          | В                            |

| los                 | Input offset current                                   | T <sub>A</sub> = -40°C to +85°C                                                      |                                                      | -68                          |                          | 67                        | nA       | В                            |

|                     |                                                        | T <sub>A</sub> = -40°C to +125°C                                                     |                                                      | -68                          |                          | 78                        |          | В                            |

|                     | input offset current mismatch                          | T <sub>A</sub> = 25°C                                                                |                                                      | -65                          |                          | 65                        | nA       | D                            |

|                     | Input offset current drift <sup>(3)</sup>              | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C (PV)}$                            | V package)                                           | -240                         | ±20                      | 240                       | pA/°C    | В                            |

|                     | Offset current drift mismatch                          | $T_A = -40$ °C to +125°C (PW package)                                                |                                                      | -260                         | ±20                      | 260                       | pA/°C    | В                            |

| INPUT               |                                                        |                                                                                      |                                                      |                              |                          |                           |          |                              |

|                     | 0 1: 11                                                | > 87 dB CMRR at input                                                                | T <sub>A</sub> = 25°C                                |                              | (V <sub>S-</sub> ) - 0.2 | (V <sub>S-</sub> ) - 0.1  | V        | А                            |

|                     | Common-mode input, low                                 | range limits                                                                         | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                              | (V <sub>S-</sub> ) - 0.1 | V <sub>S-</sub>           |          | В                            |

|                     |                                                        | > 87 dB CMRR at input                                                                | T <sub>A</sub> = 25°C                                | (V <sub>S+</sub> ) – 1.2     | (V <sub>S+</sub> ) -1.1  |                           | .,       | А                            |

|                     | Common-mode input, high                                | range limits                                                                         | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | (V <sub>S+</sub> ) – 1.3     | (V <sub>S+</sub> ) -1.2  |                           | V        | В                            |

| CMRR                | Common-mode rejection ratio                            | Input pins at [(V <sub>S+</sub> ) – (V <sub>S-</sub> )                               | ] / 2                                                | 90                           | 110                      |                           | dB       | Α                            |

|                     | Input impedance differential mode                      | Input pins at [(V <sub>S+</sub> ) – (V <sub>S-</sub> )                               | ] / 2                                                |                              | 100    1.2               |                           | kΩ    pF | С                            |

| OUTPU               | Г                                                      |                                                                                      |                                                      |                              |                          |                           |          |                              |

| \/                  | Output voltage low                                     | T <sub>A</sub> = 25°C                                                                | T <sub>A</sub> = 25°C                                |                              |                          | (V <sub>S-</sub> ) + 0.21 | - V      | А                            |

| V <sub>OL</sub>     | Output voltage, low                                    | T <sub>A</sub> = -40°C to +125°C                                                     |                                                      |                              | (V <sub>S-</sub> ) + 0.2 | (V <sub>S-</sub> ) + 0.22 | ٧        | В                            |

| .,                  | Output voltage, high                                   | T <sub>A</sub> = 25°C                                                                |                                                      | (V <sub>S+</sub> ) –<br>0.21 | (V <sub>S+</sub> ) - 0.2 |                           | · V      | А                            |

| V <sub>OH</sub>     |                                                        | $T_A = -40$ °C to +125°C                                                             |                                                      | (V <sub>S+</sub> ) –<br>0.22 | (V <sub>S+</sub> ) - 0.2 |                           |          | В                            |

|                     | Continuous output current                              | $\pm 1.5$ V, R <sub>L</sub> = 40 $\Omega$ ,<br>V <sub>OCM</sub> offset < $\pm 20$ mV | T <sub>A</sub> = 25°C                                | ±35                          | ±40                      |                           | mA -     | А                            |

|                     | Continuous Curput Current                              | $\pm 1.3$ V, R <sub>L</sub> = 40 $\Omega$ ,<br>V <sub>OCM</sub> offset < $\pm 20$ mV | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | ±30                          |                          |                           | 110.     | В                            |

|                     | Linear output current                                  | $\pm 1.5$ V, R <sub>L</sub> = 50 Ω,<br>A <sub>OL</sub> > 80 dB                       | T <sub>A</sub> = 25°C                                | ±28                          | ±35                      |                           | mA       | А                            |

|                     |                                                        | $\pm 1.1$ V, R <sub>L</sub> = 50 Ω,<br>A <sub>OL</sub> > 80 dB                       | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | ±20                          |                          |                           |          | В                            |

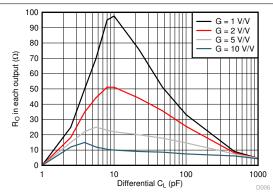

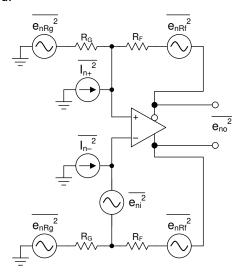

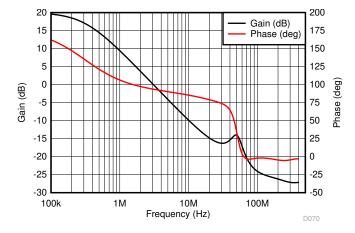

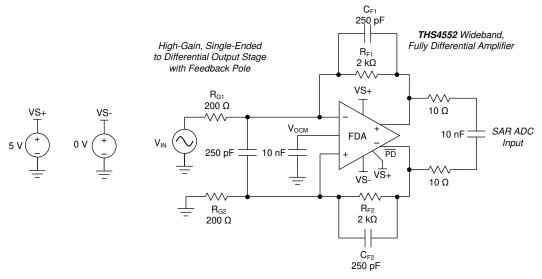

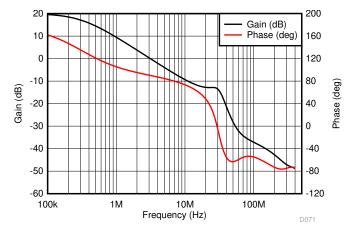

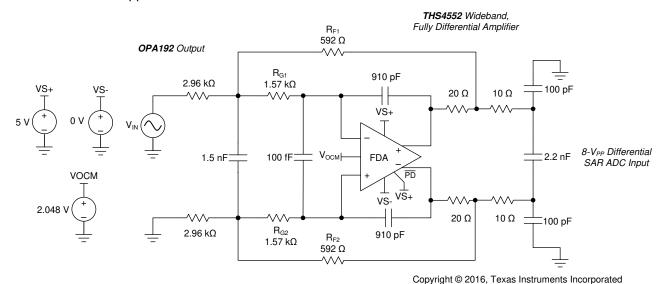

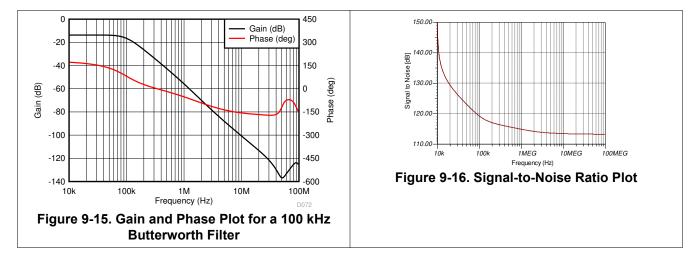

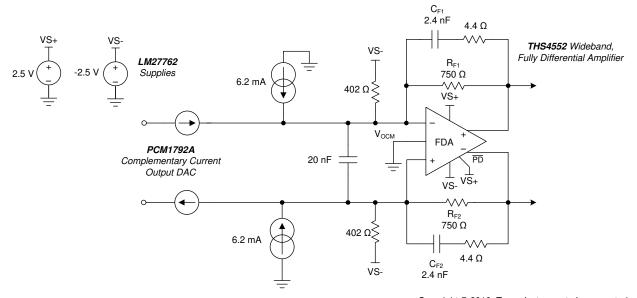

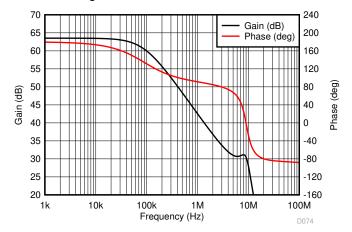

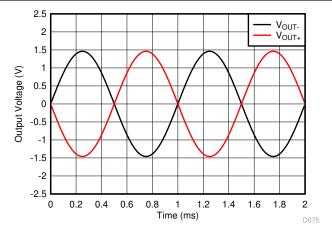

| POWER               | SUPPLY                                                 |                                                                                      |                                                      |                              |                          |                           |          |                              |