**TDES960** SNLS698A - APRIL 2021 - REVISED SEPTEMBER 2023

# TDES960 Quad 4.16-Gbps V<sup>3</sup>Link Deserializer Hub With MIPI CSI-2 Interface for High Speed, High Resolution Cameras, RADAR, and Other Sensors

### 1 Features

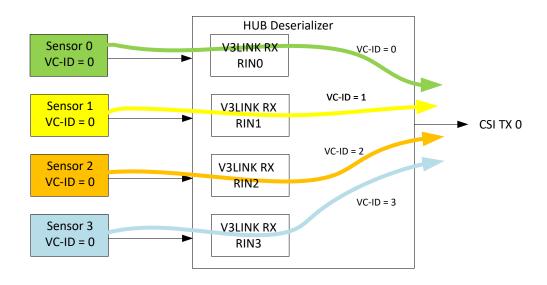

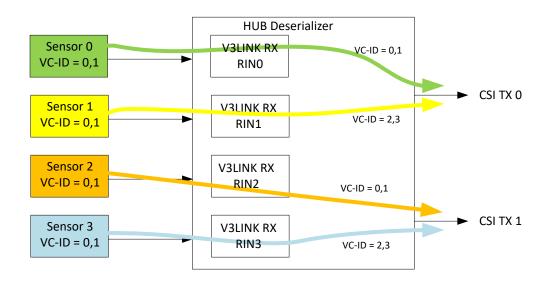

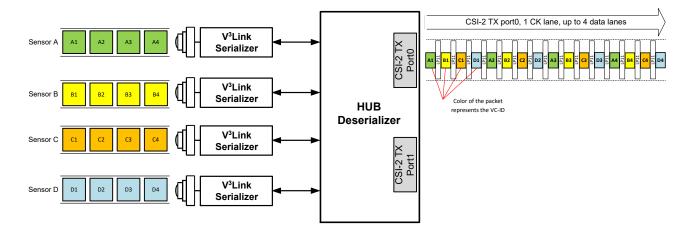

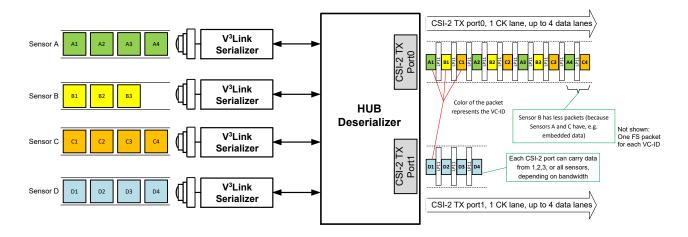

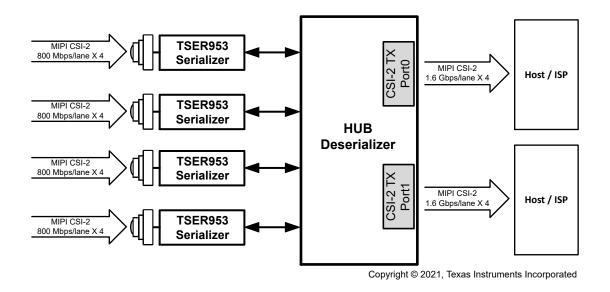

- Quad 4.16-Gbps Deserializer Hub Aggregates Data From up to 4 Sensors Simultaneously

- Supports 2-Megapixel Sensors With Full HD 1080p Resolution at 60-Hz Frame Rate

- Device Temperature Range: -20°C to +85°C Ambient Operating Temperature

- Precise Multi-Camera Synchronization

- MIPI D-PHY Version 1.2 / CSI-2 Version 1.3 Compliant

- 2 × MIPI CSI-2 Output Ports

- Supports 1, 2, 3, 4 Data Lanes per CSI-2 port

- CSI-2 Data Rate Scalable for 400 Mbps / 800 Mbps / 1.2 Gbps / 1.5 Gbps / 1.6 Gbps per Data Lane

- Port Replication Mode

- Ultra-Low Data and Control Path Latency

- Supports Single-Ended Coaxial Including Powerover-Coax (PoC) or Shielded Twisted-Pair (STP) Cable

- Adaptive Receive Equalization

- Dual I2C Ports With Fast-Mode Plus up to 1 Mbps

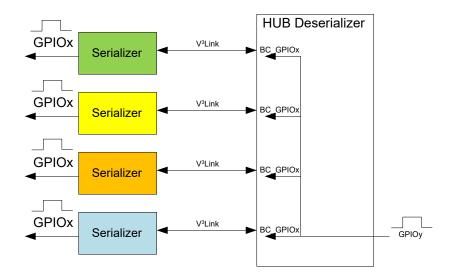

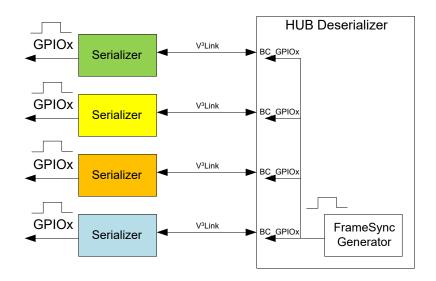

- Flexible GPIOs for Sensor Synchronization and Diagnostics

- Compatible With TSER953 Serializer

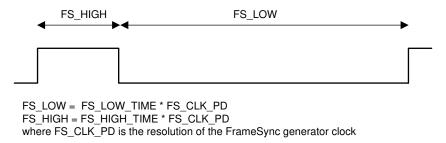

- Internal Programmable Precision Frame Sync

- Line Fault Detection and Advanced Diagnostics

# 2 Applications

- **Appliances**

- Video Surveillance

- **Elevators and Escalators**

- **Industrial Robots**

- **Machine Vision**

- **Patient Monitoring and Diagnostics**

- **Imaging**

## 3 Description

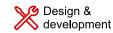

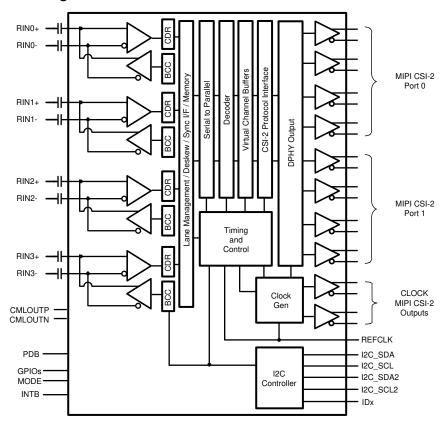

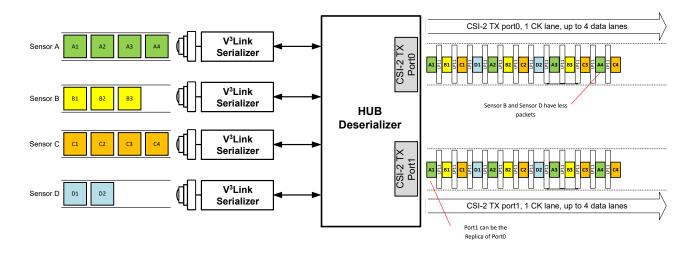

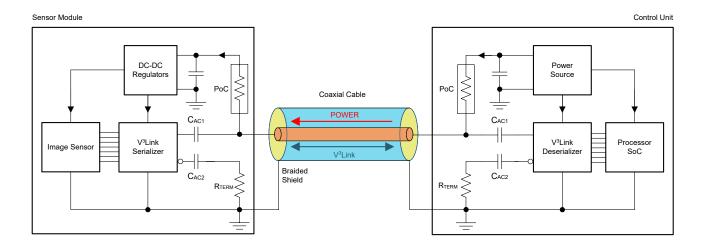

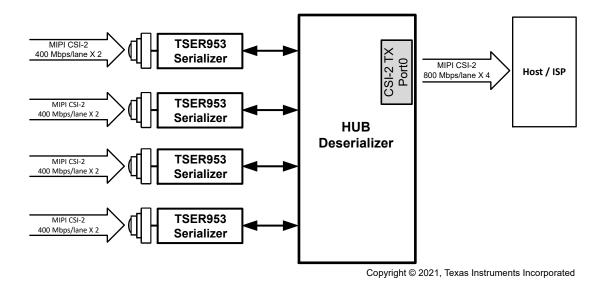

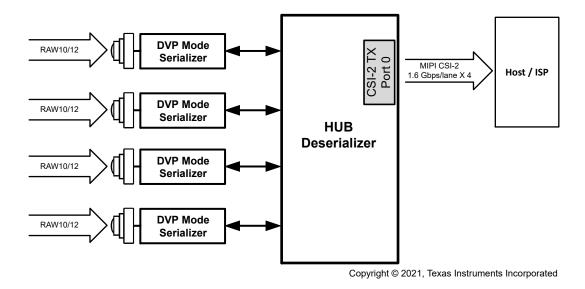

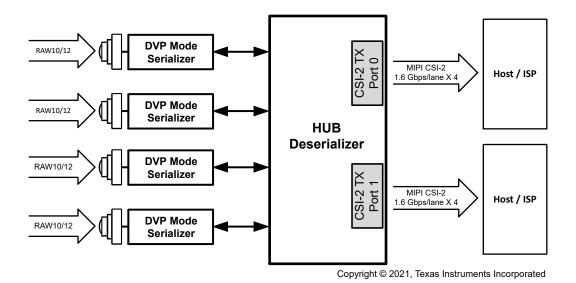

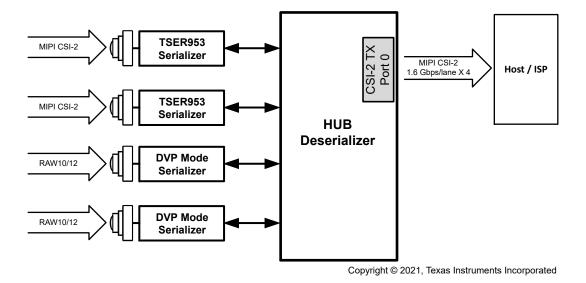

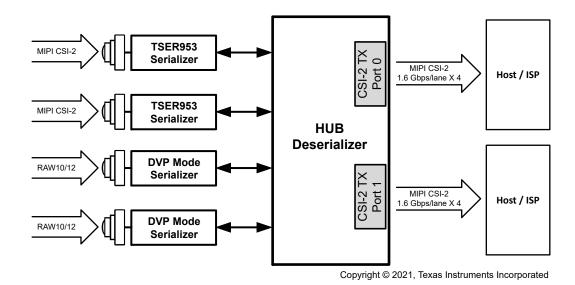

The TDES960 is a versatile sensor hub capable of connecting serialized sensor data received from four independent video data streams through a V<sup>3</sup>Link interface. When paired with a TSER953 serializer, the TDES960 receives data from sensors such as imagers supporting full HD 1080p/2MP resolution at 60-Hz frame rates. Data is received and aggregated into a MIPI CSI-2 compliant output for interconnect to a downstream processor. A second MIPI CSI-2 output port is available to provide additional bandwidth, or offers a second replicated output for data-logging and parallel processing.

The TDES960 includes four V<sup>3</sup>Link deserializers. each enabling a connection through cost-effective 50-Ω single-ended coaxial or 100-Ω differential STP cables. The receive equalizers automatically adapt to compensate for cable loss characteristics, including degradation over time.

Each of the V<sup>3</sup>Link interfaces also includes a separate low latency bidirectional control channel that continuously conveys I2C, GPIOs, and other control information. General-purpose I/O signals such as those required for camera synchronization and diagnostics features also make use of this bidirectional control channel.

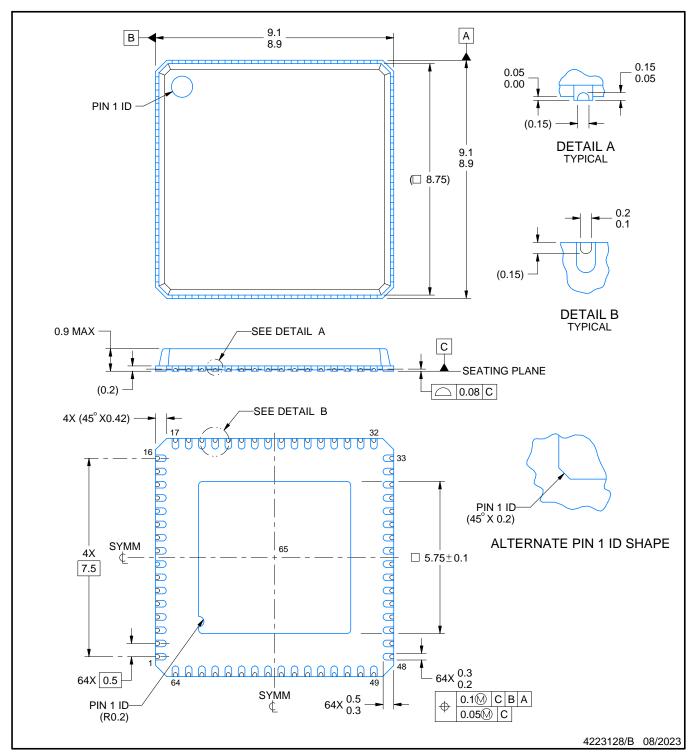

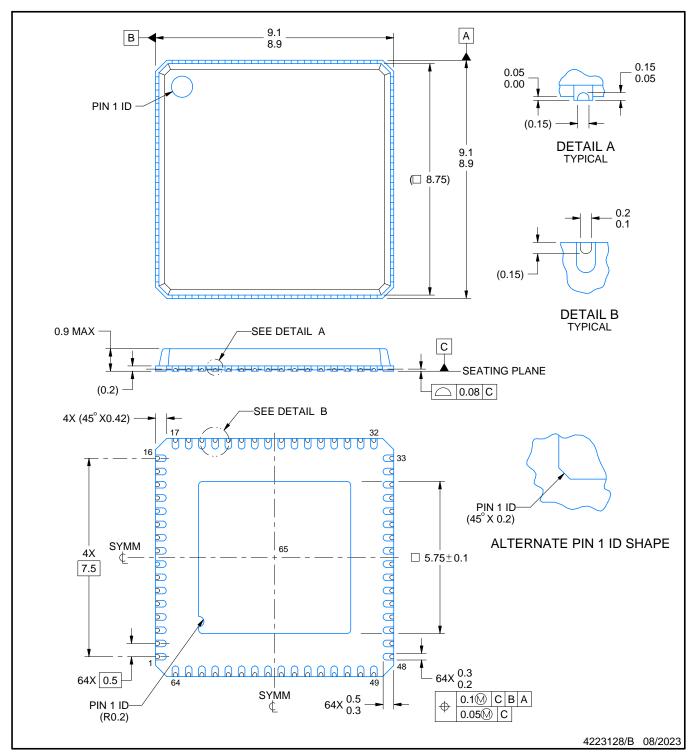

The TDES960 is offered in a cost-effective and spacesaving 64-pin VQFN package.

## **Device Information**

| PART NUMBER(1) | PACKAGE   | BODY SIZE (NOM)   |

|----------------|-----------|-------------------|

| TDES960        | VQFN (64) | 9.00 mm × 9.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

Typical Application Schematic

# **Table of Contents**

| 1 Features1                                         | 7.3 Feature Description27                               |

|-----------------------------------------------------|---------------------------------------------------------|

| 2 Applications1                                     | 7.4 Device Functional Modes27                           |

| 3 Description1                                      | 7.5 Programming56                                       |

| 4 Revision History2                                 | 7.6 Register Maps71                                     |

| 5 Pin Configuration and Functions4                  | 8 Application and Implementation162                     |

| 6 Specifications8                                   | 8.1 Application Information162                          |

| 6.1 Absolute Maximum Ratings8                       | 8.2 Typical Application166                              |

| 6.2 ESD Ratings8                                    | 8.3 System Examples169                                  |

| 6.3 Recommended Operating Conditions9               | 8.4 Power Supply Recommendations172                     |

| 6.4 Thermal Information9                            | 8.5 Layout175                                           |

| 6.5 DC Electrical Characteristics10                 | 9 Device and Documentation Support181                   |

| 6.6 AC Electrical Characteristics13                 | 9.1 Documentation Support181                            |

| 6.7 CSI-2 Timing Specifications14                   | 9.2 Receiving Notification of Documentation Updates 181 |

| 6.8 Recommended Timing for the Serial Control Bus19 | 9.3 Support Resources181                                |

| 6.9 Timing Diagrams20                               | 9.4 Trademarks181                                       |

| 6.10 Typical Characteristics25                      | 9.5 Electrostatic Discharge Caution181                  |

| 7 Detailed Description26                            | 9.6 Glossary181                                         |

| 7.1 Overview26                                      | 10 Mechanical, Packaging, and Orderable                 |

| 7.2 Functional Block Diagram27                      | Information187                                          |

|                                                     |                                                         |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | lianges from Revision (April 2021) to Revision A (September 2023)                                     | Fage             |

|---|-------------------------------------------------------------------------------------------------------|------------------|

| • | Fixed spelling errors and minor format issues throughout the document                                 | 1                |

| • | Updated I2C pull-up Resistor Recommendations                                                          | 4                |

| • | Updated Legend for Pin Functions Table                                                                |                  |

| • | Removed the t <sub>CLK-MISS</sub> specification from the CSI-2 Timing Specifications table            |                  |

| • | Removed obstructions in CSI-2 General Frame Format figure to make text clearer                        |                  |

| • | Clarified the clock speed and the configuration settings of non-synchronous clock mode                |                  |

| • | Added clarification that MODE pin option 0 straps the device to CSI-2 Non-Synchronous back channel    |                  |

|   | MODE pin option 4 straps the device to CSI-2 Synchronous back channel                                 |                  |

| • | Changed I2C terminology to "Controller" and "Target"                                                  |                  |

| • | Updated the transmission channel requirements for Coaxial and STP/STQ Cable Applications              |                  |

| • | Removed mention of older silicon.                                                                     |                  |

| • | Clarified that CSI-2 forwarding should be disabled before CSI-2 replicate mode is enabled             |                  |

| • | Added a sentence to clarify that V <sub>I2C</sub> must match the voltage applied to VDDIO             |                  |

| • | Reworded the Serial Control Bus section to reference V <sub>I2C</sub> instead of VDDIO                |                  |

| • | Added register addresses for the RX Port ID registers                                                 |                  |

| • | Removed information suggesting that the Rx Port intended for messaging must always be selected wit    |                  |

|   | Register 0x4C when communicating with a remote target device                                          |                  |

| • | Corrected the total number of TargetID and TargetAlias pairs of registers for the device              |                  |

| • | Clarified that the write enable bit in register 0x4C needs to be set before configuring remote target |                  |

|   | addresses                                                                                             | <mark>5</mark> 9 |

| • | Added additional information about how to configure a broadcast write to remote devices               | 59               |

| • | Updated the I2C Controller Proxy description                                                          |                  |

| • | Fixed register address errors in the Typical I2C Timing Register Settings table                       |                  |

| • | Removed details about the internal reference clock                                                    |                  |

| • | Clarified instructions for how to configure Pattern Generation on the CSI-2 Ports                     | 67               |

| • | Removed all RESERVED registers from the datasheet                                                     |                  |

| • | Made register bits 0x34[5:4] public and updated the description of register bit 0x34[1]               |                  |

| • | Corrected a bit description typo for bit 4 of register 0x4A                                           |                  |

| • | Updated description of register 0x4E[1] to clarify functionality                                      |                  |

|   |                                                                                                       |                  |

## www.ti.com

| • | Updated the description sections of registers 0x51-0x54                                        | 71               |

|---|------------------------------------------------------------------------------------------------|------------------|

|   | Fixed typos in the description for registers 0x90-0x9F                                         |                  |

| • | Removed RESERVED indirect register pages in the description of register bits 0xB0[5:2]         | <mark>7</mark> 1 |

| • | Made register 0xB6 public                                                                      | <mark>7</mark> 1 |

|   | Updated the bit description of 0xB9[3:0]                                                       |                  |

|   | Updated the name of Indirect Register Page 0 to PATGEN_AND_CSI-2                               |                  |

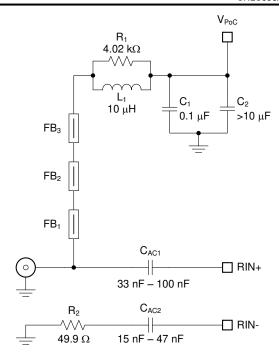

| • | Updated the PoC description                                                                    | 162              |

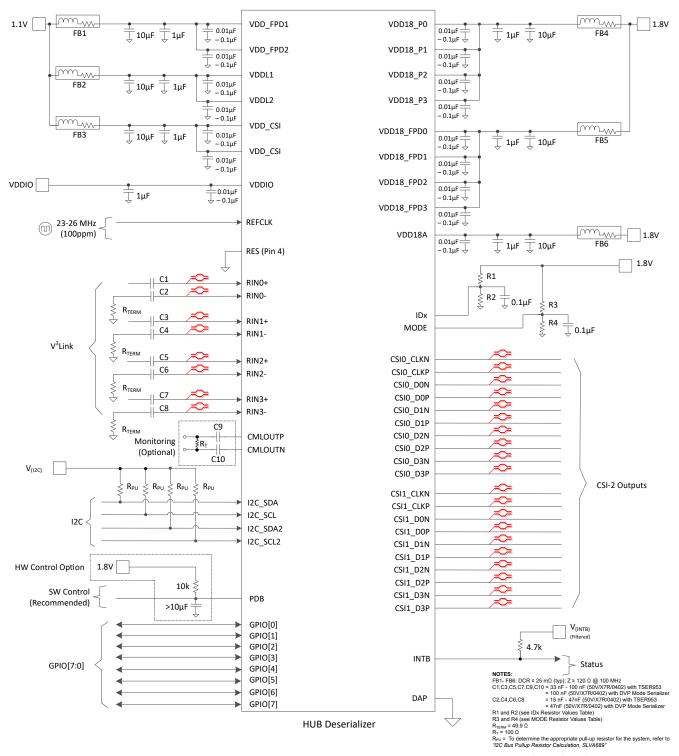

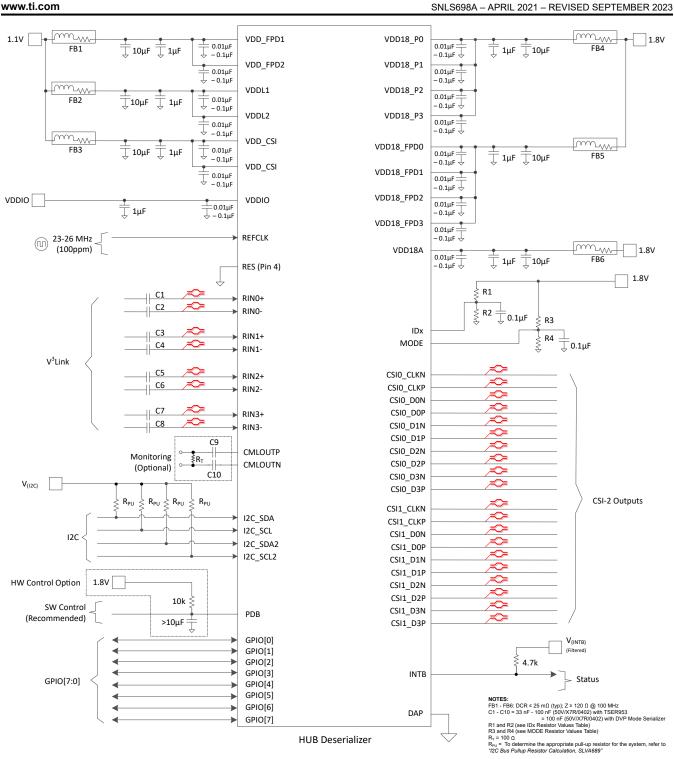

| • | Updated both typical connection diagrams to include a reference to App Note SLVA689            | 166              |

| • | Added clarification for the recommended ferrite bead characteristics on the power supply rails | 166              |

| • | Removed optional 10 kΩ pulldown resistor on Pin 4 in the Typical Connection Diagram            | 166              |

| • | Fixed part number typo in the Power-Up Sequencing With Non-Synchronous Clocking Mode figure    | 173              |

|   | Updated MIPI CSI-2 D-PHY layout recommendations                                                |                  |

|   |                                                                                                |                  |

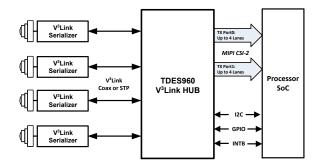

# 5 Pin Configuration and Functions

Figure 5-1. RTD Package 64-Pin VQFN (Top View)

## Table 5-1 Pin Functions

|                             | IN          | I/O  | Table 5-1. Pin Functions                                                                                                                                                                                                                                                                                                          |

|-----------------------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | 1           | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |

| NAME                        | NO.         |      |                                                                                                                                                                                                                                                                                                                                   |

| MIPI CSI-2 TX IN            | I           | 0    | CSL 2 TV Part 0 differential cleak output nine                                                                                                                                                                                                                                                                                    |

| CSIO_CLKN                   | 22          | 0    | CSI-2 TX Port 0 differential clock output pins. Leave unused pins as No Connect.                                                                                                                                                                                                                                                  |

| CSIO_CLKP                   | 23          | _    |                                                                                                                                                                                                                                                                                                                                   |

| CSIO_DON                    | 24          | _    | CSI-2 TX Port 0 differential data output pins. Use CSI_PORT_SEL, CSI_CTL, and CSI_CTL2 registers for the CSI-2 TX control.                                                                                                                                                                                                        |

| CSI0_D0P                    | 25          |      | Leave unused pins as No Connect.                                                                                                                                                                                                                                                                                                  |

| CSI0_D1N                    | 26          | _    |                                                                                                                                                                                                                                                                                                                                   |

| CSI0_D1P                    | 27          | _    |                                                                                                                                                                                                                                                                                                                                   |

| CSI0_D2N                    | 28          | _    |                                                                                                                                                                                                                                                                                                                                   |

| CSI0_D2P                    | 29          |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI0_D3N                    | 30          |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI0_D3P                    | 31          |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI1_CLKN                   | 34          | 0    | CSI-2 TX Port 1 differential clock output pins. Leave unused pins as No Connect.                                                                                                                                                                                                                                                  |

| CSI1_CLKP                   | 35          |      | ·                                                                                                                                                                                                                                                                                                                                 |

| CSI1_D0N                    | 36          |      | CSI-2 TX Port 1 differential data output pins. Use CSI_PORT_SEL, CSI_CTL, and CSI_CTL2 registers for the CSI-2 TX control.                                                                                                                                                                                                        |

| CSI1_D0P                    | CSI1_D1N 38 |      | Leave unused pins as No Connect.                                                                                                                                                                                                                                                                                                  |

| CSI1_D1N                    |             |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI1_D1P                    |             |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI1_D2N                    | 40          |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI1_D2P                    | 41          |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI1_D3N                    | 42          |      |                                                                                                                                                                                                                                                                                                                                   |

| CSI1_D3P                    | 43          |      |                                                                                                                                                                                                                                                                                                                                   |

| V <sup>3</sup> Link RX INTE | RFACE       |      |                                                                                                                                                                                                                                                                                                                                   |

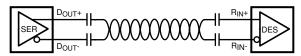

| RIN0+                       | 50          | I/O  | V <sup>3</sup> Link RX Port 0 pins. The port receives V <sup>3</sup> Link high-speed forward channel video and                                                                                                                                                                                                                    |

| RIN0-                       | 51          |      | control data and transmits back channel control data. It can interface with a compatible V³Link serializer TX through a STP or coaxial cable (see Figure 8-6 and Figure 8-7). It must be AC-coupled per Table 8-4. If port is unused, set RX_PORT_CTL register bit 0 to 0 to disable RX Port 0 and leave the pins as No Connect.  |

| RIN1+                       | 53          |      | V <sup>3</sup> Link RX Port 1 pins. The port receives V <sup>3</sup> Link high-speed forward channel video and                                                                                                                                                                                                                    |

| RIN1-                       | 54          |      | control data and transmits back channel control data. It can interface with a compatible V³Link serializer TX through a STP or coaxial cable (see Figure 8-6 and Figure 8-7). It must be AC-coupled per Table 8-4.  If port is unused, set RX_PORT_CTL register bit 1 to 0 to disable RX Port 1 and leave the pins as No Connect. |

| RIN2+                       | 59          |      | V <sup>3</sup> Link RX Port 2 pins. The port receives V <sup>3</sup> Link high-speed forward channel video and                                                                                                                                                                                                                    |

| RIN2-                       | 60          |      | control data and transmits back channel control data. It can interface with a compatible V³Link serializer TX through a STP or coaxial cable (see Figure 8-6 and Figure 8-7). It must be AC-coupled per Table 8-4. If port is unused, set RX_PORT_CTL register bit 2 to 0 to disable RX Port 2 and leave the pins as No Connect.  |

| RIN3+                       | 62          |      | V <sup>3</sup> Link RX Port 3 pins. The port receives V <sup>3</sup> Link high-speed forward channel video and                                                                                                                                                                                                                    |

| RIN3-                       | 63          |      | control data and transmits back channel control data. It can interface with a compatible V³Link serializer TX through a STP or coaxial cable (see Figure 8-6 and Figure 8-7). It must be AC-coupled per Table 8-4. If port is unused, set RX_PORT_CTL register bit 3 to 0 to disable RX Port 3 and leave the pins as No Connect.  |

## **Table 5-1. Pin Functions (continued)**

| P                    | PIN           | I/O         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO.           | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SYNCHRONIZA          | TION AND GENE | RAL-PURPOSE | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIO0                | 9             | I/O, PD     | General-Purpose Input/Output pins. The pins can be used to control and respond to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GPIO1                | 10            |             | various commands. They may be configured to be input signals for the corresponding GPIOs on the serializer or they may be configured to be outputs to follow local register                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GPIO2                | 14            |             | settings. At power up, the GPIO pins are disabled and by default include a pulldown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIO3                | 15            |             | resistor (25-kΩ typ). See Section 7.4.11. for programmability. If unused, leave the pin as No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO4                | 17            |             | See Section 7.4. 17. for programmability. If unused, leave the pin as No Conflect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GPIO5                | 18            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO6                | 19            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO7                | 20            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INTB                 | 6             | O, OD       | Interrupt Output pin. INTB is an active-low open drain and controlled by the status registers. See <i>Section</i> 7.5.9. Recommend a 4.7-kΩ Pullup to 1.8 V or 3.3 V. If unused, leave the pin as No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SERIAL CONTR         | ROL BUS (I2C) |             | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

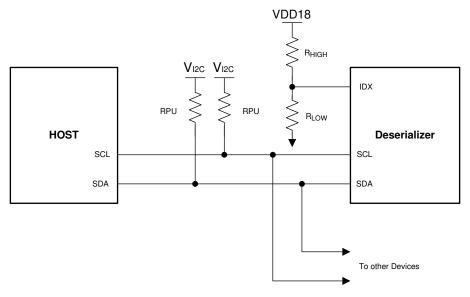

| I2C_SCL              | 12            | I/O, OD     | Primary I2C Clock Input / Output interface pin. See Section 7.5.1. Refer to "I2C Bus Pullup Resistor Calculation" (SLVA689) to determine the pull-up resistor value to VDDIO. If unused, leave this pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I2C_SDA              | 11            | I/O, OD     | Primary I2C Data Input / Output interface pin. See Section 7.5.1.  Refer to "I2C Bus Pullup Resistor Calculation" (SLVA689) to determine the pull-up resistor value to VDDIO. If unused, leave this pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I2C_SCL2             | 8             | I/O, OD     | Secondary I2C Clock Input / Output interface pin. See Section 7.5.2.  Refer to "I2C Bus Pullup Resistor Calculation" (SLVA689) to determine the pull-up resistor value to VDDIO. If unused, leave this pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I2C_SDA2             | 7             | I/O, OD     | Secondary I2C Data Input / Output interface pin. See Section 7.5.2.  Refer to "I2C Bus Pullup Resistor Calculation" (SLVA689) to determine the pull-up resistor value to VDDIO. If unused, leave this pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CONFIGURATION        | ON AND CONTRO | OL          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

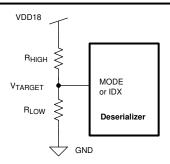

| IDX                  | 46            | S           | I2C Serial Control Bus Device ID Address Select configuration pin. Connect to an external pullup to VDD18 and a pulldown to GND to create a voltage divider. See Table 7-17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MODE                 | 45            | S           | Mode Select configuration pin. Connect to external pullup to VDD18 and a pulldown to GND to create a voltage divider. See Table 7-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

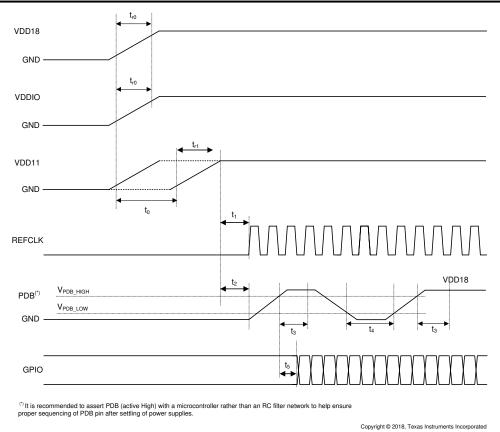

| PDB                  | 3             | I, PD       | Inverted Power-Down input pin. Typically connected to a processor GPIO with a pulldown. When PDB input is brought HIGH, the device is enabled and internal registers and state machines are reset to default values. Asserting PDB signal low will power down the device and consume minimum power. The default function of this pin is PDB = LOW; POWER DOWN with an internal 50-kΩ internal pulldown enabled. PDB must remain low until after power supplies are applied and reach minimum required levels. See <i>Section 8.4.1</i> .  INPUT IS 3.3-V TOLERANT PDB = 1.8 V, device is enabled (normal operation) PDB = 0 V, device is powered down. |

| POWER AND G          | POLIND        |             | ן טע - טע א, device is powered down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDDIO                | 16            | Р           | 1.8-V (±5%) OR 3.3-V (±10%) LVCMOS I/O Power<br>Requires 1-µF and 0.1-µF or 0.01-µF capacitors to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VDD_CSI0<br>VDD_CSI1 | 21<br>33      | Р           | 1.1-V (±5%) Power Supplies Requires 0.1-μF or 0.01-μF capacitors to GND at each VDD pin. Additional 1-μF and 10-μF decoupling is recommended for the pin group.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDDL1<br>VDDL2       | 13<br>44      | Р           | 1.1-V (±5%) Power Supplies Requires 0.1-μF or 0.01-μF capacitors to GND at each VDD pin. Additional 1-μF and 10-μF decoupling is recommended for the pin group.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

**Table 5-1. Pin Functions (continued)**

| PI                                                   | N                         | I/O                                                                                                                                                               | DECORIDATION                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                 | NO.                       | TYPE                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                    |  |  |  |

| VDD_FPD1 52<br>VDD_FPD2 61                           |                           | Р                                                                                                                                                                 | 1.1-V (±5%) Power Supplies Requires 0.1-μF or 0.01-μF capacitors to GND at each VDD pin. Additional 1-μF and 10-μF decoupling is recommended for the pin group.                                                                                                                                                |  |  |  |

| VDD18_P3<br>VDD18_P2<br>VDD18_P1<br>VDD18_P0         | VDD18_P2 2<br>VDD18_P1 47 |                                                                                                                                                                   | 1.8-V (±5%) Power Supplies Requires 0.1-μF or 0.01-μF capacitors to GND at each VDD pin. Additional 1-μF, and 10-μF decoupling is recommended for the pin group.                                                                                                                                               |  |  |  |

| VDD18A                                               | 32                        | P 1.8-V (±5%) Power Supplies Requires 0.1-μF or 0.01-μF capacitors to GND at each VDD pin. Additional 1-μF, an 10-μF decoupling is recommended for the pin group. |                                                                                                                                                                                                                                                                                                                |  |  |  |

| VDD18_FPD0<br>VDD18_FPD1<br>VDD18_FPD2<br>VDD18_FPD3 | 49<br>55<br>58<br>64      | P 1.8-V (±5%) Power Supplies Requires 0.1-μF or 0.01-μF capacitors to GND at each VDD pin. Additional 1-μF, an 10-μF decoupling is recommended for the pin group. |                                                                                                                                                                                                                                                                                                                |  |  |  |

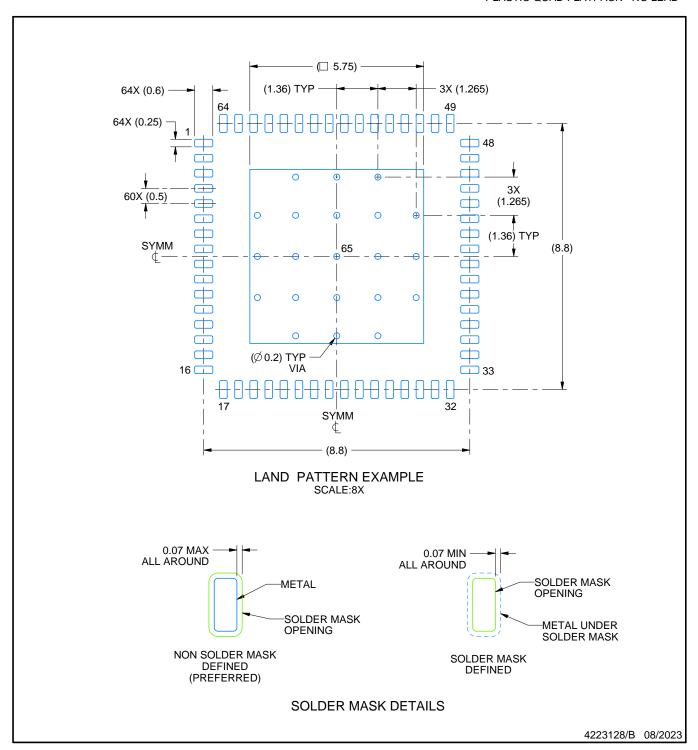

| GND                                                  | DAP                       | G                                                                                                                                                                 | DAP is the large metal contact at the bottom side, located at the center of the VQFN package. Connect to the ground plane (GND).                                                                                                                                                                               |  |  |  |

| OTHERS                                               |                           | 1                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                |  |  |  |

| REFCLK 5                                             |                           | I                                                                                                                                                                 | Reference clock oscillator input. Typically connected to a 23-MHz to 26-MHz LVCMOS-level oscillator (100 ppm). For 400-Mbps, 800-Mbps, 1.2-Gbps or 1.6-Gbps CSI-2 data rates, use 25-MHz frequency. For the oscillator requirements, see Section 7.4.4. For other common CSI-2 data rates, see Section 7.4.19. |  |  |  |

| RES                                                  | 4                         | -                                                                                                                                                                 | This pin must be tied to GND for normal operation.                                                                                                                                                                                                                                                             |  |  |  |

| CMLOUTP                                              | 56                        | 0                                                                                                                                                                 | Channel Monitor Loop-through Driver differential output.                                                                                                                                                                                                                                                       |  |  |  |

| CMLOUTN                                              | 57                        | 1                                                                                                                                                                 | Route to a test point or a pad with $100-\Omega$ termination resistor between pins for channel monitoring (recommended). See <i>Section 7.4.8</i> .                                                                                                                                                            |  |  |  |

The definitions below define the functionality of the I/O cells for each pin. TYPE:

- I = Input

- O = Output

- I/O = Input/Output

- S = Strap Input

- PD = Internal Pulldown

- OD = Open Drain

- P = Power Supply

- G = Ground

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1) (2)

|                                                               |                                                                                                                                                                                                                           |                                                                          | MIN                        | MAX                                | UNIT |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|------------------------------------|------|

|                                                               | VDD11 (VDD_CSI, VDDL                                                                                                                                                                                                      | VDD11 (VDD_CSI, VDDL1, VDDL2, VDD_FPD1, VDD_FPD2)                        |                            | 1.32 and<br><v<sub>(VDD18)</v<sub> | V    |

| Supply voltage                                                | VDD18 (VDD18_P0, VDD<br>VDD18_FPD1, VDD18_F                                                                                                                                                                               | 018_P1, VDD18_P2, VDD18_P3, VDD18A, VDD18_FPD0,<br>:PD2, VDD18_FPD3)     | -0.3                       | 2.16                               | V    |

|                                                               | VDDIO                                                                                                                                                                                                                     |                                                                          | -0.3                       | 3.96                               | V    |

|                                                               | RIN0+, RIN0-, RIN1+,                                                                                                                                                                                                      | Device powered up (All supplies within recommended operating conditions) | -0.3                       | 2.75                               | V    |

| V <sup>3</sup> Link input voltage                             | RIN1-, RIN2+, RIN2-,<br>RIN3+, RIN3-                                                                                                                                                                                      | Device powered down, Transient voltage                                   | -0.3                       | 1.45                               | V    |

|                                                               |                                                                                                                                                                                                                           | Device powered down, DC voltage                                          | -0.3                       | 1.35                               | V    |

| CSI-2 voltage                                                 | CSI0_D0P, CSI0_D0N, CSI0_D1P, CSI0_D1N, CSI0_D2P, CSI0_D2N, CSI0_D3N, CSI-2 voltage  CSI0_CLKP, CSI0_CLKN, CSI1_D0P, CSI1_D0N, CSI1_D1P, CSI1_D1N, CSI1_D2P, CSI1_D2N, CSI1_D2N, CSI1_D3P, CSI1_D3N, CSI1_CLKP, CSI1_CLKN |                                                                          |                            | 1.32                               | V    |

| LVCMOS IO veltere                                             | PDB                                                                                                                                                                                                                       |                                                                          | -0.3                       | 3.96                               | V    |

| LVCMOS IO voltage                                             | GPIO[7:0], REFCLK, RE                                                                                                                                                                                                     | GPIO[7:0], REFCLK, RES, CMLOUTP, CMLOUTN                                 |                            | V <sub>(VDDIO)</sub> + 0.3         | V    |

| Configuration input voltage MODE, IDX                         |                                                                                                                                                                                                                           | -0.3                                                                     | V <sub>(VDD18)</sub> + 0.3 | V                                  |      |

| Open-Drain voltage I2C_SDA, I2C_SCL, I2C_SDA2, I2C_SCL2, INTB |                                                                                                                                                                                                                           |                                                                          | -0.3                       | 3.96                               | V    |

| Junction temperature                                          |                                                                                                                                                                                                                           |                                                                          |                            | 150                                | °C   |

| Storage temperature, T <sub>stg</sub>                         |                                                                                                                                                                                                                           |                                                                          | -65                        | 150                                | °C   |

- (1) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office or Distributors for availability and specifications.

- (2) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                                            |                                                                                   |                                                                                                                     |                                                                                  | VALUE   | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------|------|

|                                            |                                                                                   |                                                                                                                     | RIN0+, RIN0-, RIN1+, RIN1-, RIN2+,<br>RIN2-, RIN3+, RIN3-                        | ±6000   | V    |

|                                            |                                                                                   | Other pins                                                                                                          | ±3000                                                                            | V       |      |

|                                            |                                                                                   | Charged device model (CDM)                                                                                          |                                                                                  | ±1000   | V    |

| V <sub>(ESD)</sub> Electrostatic discharge |                                                                                   | ESD Rating (IEC 61000-4-2)<br>$R_D$ = 330 $\Omega$ , $C_S$ = 150 pF                                                 | Contact Discharge<br>(RIN0+, RIN0-, RIN1+, RIN1-, RIN2+,<br>RIN2-, RIN3+, RIN3-) | ±10 000 | V    |

|                                            | Electrostatic discharge                                                           |                                                                                                                     | Air Discharge<br>(RIN0+, RIN0-, RIN1+, RIN1-, RIN2+,<br>RIN2-, RIN3+, RIN3-)     | ±21 000 | V    |

|                                            | ESD Rating (ISO 10605) R <sub>D</sub> = 330 Ω, C <sub>S</sub> = 150 pF and 330 pF | Contact Discharge<br>(RIN0+, RIN0-, RIN1+, RIN1-, RIN2+,<br>RIN2-, RIN3+, RIN3-)                                    | ±10 000                                                                          | V       |      |

|                                            |                                                                                   | $R_D = 350  \Omega$ , $C_S = 150  \text{pF}$ and 330 pF<br>$R_D = 2  \text{kΩ}$ , $C_S = 150  \text{pF}$ and 330 pF | Air Discharge<br>(RIN0+, RIN0-, RIN1+, RIN1-, RIN2+,<br>RIN2-, RIN3+, RIN3-)     | ±21 000 | V    |

(1) HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# **6.3 Recommended Operating Conditions**

Over operating free-air temperature range (unless otherwise noted)

|                                                    | ·                                                          | MIN   | NOM | MAX   | UNIT              |

|----------------------------------------------------|------------------------------------------------------------|-------|-----|-------|-------------------|

| Supply voltage                                     | V <sub>(VDD11)</sub>                                       | 1.045 | 1.1 | 1.155 | V                 |

| Supply voltage                                     | V <sub>(VDD18)</sub>                                       | 1.71  | 1.8 | 1.89  | V                 |

| LVCMOS I/O supply voltage                          | V <sub>(VDDIO)</sub> = 1.8 V                               | 1.71  | 1.8 | 1.89  | V                 |

| velvies ite supply voltage                         | OR V <sub>(VDDIO)</sub> = 3.3 V                            | 3.0   | 3.3 | 3.6   | V                 |

| Open-drain voltage                                 | INTB = V <sub>(INTB)</sub> , I2C pins = V <sub>(I2C)</sub> | 1.71  |     | 3.6   | V                 |

| Operating free-air temperature, T <sub>A</sub>     |                                                            | -20   | 25  | 85    | °C                |

| MIPI data rate (per CSI-2 lane)                    |                                                            | 368   | 800 | 1664  | Mbps              |

| MIPI CSI-2 HS clock frequency                      |                                                            | 184   | 400 | 832   | MHz               |

| Reference clock frequency                          |                                                            | 23    | 25  | 26    | MHz               |

| Spread-spectrum reference clock modulation         | REFCLK, Center spread                                      | -0.5  |     | 0.5   | %                 |

| percentage                                         | REFCLK, Down spread                                        | -1    |     | 0     | %                 |

| Local I <sup>2</sup> C frequency, f <sub>I2C</sub> |                                                            |       |     | 1     | MHz               |

|                                                    | V <sub>(VDD11)</sub>                                       |       |     | 25    | mV <sub>P-P</sub> |

|                                                    | $V_{(VDD18)}$                                              |       |     | 50    | $mV_{P-P}$        |

| Supply noise <sup>(1)</sup>                        | V <sub>(VDDIO)</sub> = 1.8 V                               |       |     | 50    | $mV_{P-P}$        |

|                                                    | V <sub>(VDDIO)</sub> = 3.3 V                               |       |     | 100   | $mV_{P-P}$        |

|                                                    | RIN0+, RIN1+, RIN2+, RIN3+                                 |       | 10  |       | mV <sub>P-P</sub> |

<sup>(1)</sup> DC to 50 MHz.

## **6.4 Thermal Information**

|                        |                                              | TDES960    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RTD (VQFN) | UNIT |

|                        |                                              | 64 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 23.8       | °C/W |

| R <sub>0JC(TOP)</sub>  | Junction-to-case (top) thermal resistance    | 10.4       | °C/W |

| R <sub>0</sub> JC(BOT) | Junction-to-case (bottom) thermal resistance | 0.4        | °C/W |

| R <sub>0JB</sub>       | Junction-to-board thermal resistance         | 7.6        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.1        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 7.5        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## **6.5 DC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

|                   | PARAMETER                                  | TEST CONDITIONS                                                                                                                                                                                                   | PIN OR<br>FREQUENCY    | MIN                            | TYP | MAX           | UNIT |

|-------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|-----|---------------|------|

| POWER             | CONSUMPTION                                |                                                                                                                                                                                                                   |                        |                                |     |               |      |

| P <sub>T</sub>    | Total power consumption in operation mode  | CSI-2 TX = 4 data lanes + 1 CLK lane<br>CSI-2 TX line rate = 1.664 Gbps<br>4 × V <sup>3</sup> Link RX inputs<br>V <sup>3</sup> Link line rate = 4.16 Gbps<br>CSI-2 mode, Non-replicate mode,<br>Default registers | VDD18, VDD11,<br>VDDIO |                                | 800 | 999           | mW   |

| SUPPLY            | CURRENT                                    |                                                                                                                                                                                                                   |                        |                                |     |               |      |

|                   |                                            | CSI-2 TX = 4 data lanes + 1 CLK lane                                                                                                                                                                              | VDD11                  |                                | 165 | 310           |      |

|                   |                                            | CSI-2 TX line rate = 1.664 Gbps<br>4 × V <sup>3</sup> Link RX inputs                                                                                                                                              | VDD18                  |                                | 295 | 340           | A    |

| ı                 | Deserializer supply current (includes load | V <sup>3</sup> Link line rate = 4.16 Gbps<br>CSI-2 mode, Non-replicate mode<br>Default registers                                                                                                                  | VDDIO                  |                                | 2   | 3             | mA   |

| I <sub>DDT1</sub> | current)                                   | CSI-2 TX = 4 data lanes + 1 CLK lane                                                                                                                                                                              | VDD11                  |                                | 150 | 290           |      |

|                   |                                            | CSI-2 TX line rate = 832 Mbps<br>4 × V <sup>3</sup> Link RX inputs                                                                                                                                                | VDD18                  |                                | 295 | 340           |      |

|                   |                                            | V <sup>3</sup> Link line rate = 4.16 Gbps<br>CSI-2 mode, Non-replicate mode<br>Default registers                                                                                                                  | VDDIO                  |                                | 2   | 3             | mA   |

|                   |                                            | CSI-2 TX = 2 x (4 data lanes + 1 CLK lane) CSI-2 TX line rate = 1.664 Gbps 4 × V <sup>3</sup> Link RX inputs V <sup>3</sup> Link line rate = 4.16 Gbps CSI-2 mode, Replicate mode Default registers               | VDD11                  |                                | 174 | 360           |      |

|                   |                                            |                                                                                                                                                                                                                   | VDD18                  |                                | 312 | 370           |      |

|                   | Deserializer supply                        |                                                                                                                                                                                                                   | VDDIO                  |                                | 2   | 3             |      |

| I <sub>DDT2</sub> | current (includes load current)            | CSI-2 TX = 2 x (4 data lanes + 1 CLK lane) CSI-2 TX line rate = 832 Mbps 4 × V³Link RX inputs V³Link line rate = 4.16 Gbps CSI-2 mode, Replicate mode Default registers                                           | VDD11                  |                                | 127 | 305           | mA   |

|                   | ,                                          |                                                                                                                                                                                                                   | VDD18                  |                                | 369 | 415           |      |

|                   |                                            |                                                                                                                                                                                                                   | VDDIO                  |                                | 2   | 3             |      |

|                   |                                            | CSI-2 TX = 4 data lanes + 1 CLK lane                                                                                                                                                                              | VDD11                  |                                | 122 | 300           | _    |

|                   |                                            | CSI-2 TX line rate = 1.664 Gbps  4 × V³Link RX inputs  V³Link line rate = 1.867 Gbps  RAW12 HF mode, Non-replicate mode  Default registers                                                                        | VDD18                  |                                | 263 | 305           |      |

|                   | Deserializer supply                        |                                                                                                                                                                                                                   | VDDIO                  |                                | 2   | 3             | mA   |

| $I_{DDT3}$        | current (includes load                     | CSI-2 TX = 2 x (4 data lanes + 1 CLK                                                                                                                                                                              | VDD11                  |                                | 120 | 330           |      |

|                   | current)                                   | lane)<br>CSI-2 TX line rate = 832 Mbps                                                                                                                                                                            | VDD18                  |                                | 315 | 365           |      |

|                   |                                            | 4 × V <sup>3</sup> Link RX inputs V <sup>3</sup> Link line rate = 1.867 Gbps RAW12 HF mode, Replicate mode Default registers                                                                                      | VDDIO                  |                                | 2   | 3             | mA   |

|                   |                                            |                                                                                                                                                                                                                   | VDD11                  |                                |     | 160           |      |

| $I_{DDZ}$         | Deserializer shutdown current              | PDB = LOW                                                                                                                                                                                                         | VDD18                  |                                |     | 4             | mA   |

|                   |                                            |                                                                                                                                                                                                                   | VDDIO                  |                                |     | 3             |      |

| 1.8-V LV          | CMOS I/O                                   | I                                                                                                                                                                                                                 | 1                      |                                |     | 1             |      |

| V <sub>OH</sub>   | High level output voltage                  | $I_{OH} = -2 \text{ mA}, V_{(VDDIO)} = 1.71 \text{ to } 1.89 \text{ V}$                                                                                                                                           | GPIO[7:0]              | V <sub>(VDDIO)</sub><br>- 0.45 |     | $V_{(VDDIO)}$ | V    |

| V <sub>OL</sub>   | Low level output voltage                   | I <sub>OL</sub> = 2 mA, V <sub>(VDDIO)</sub> = 1.71 to 1.89 V                                                                                                                                                     | GPIO[7:0], INTB        | GND                            |     | 0.45          | V    |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# **6.5 DC Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified.

|                        | PARAMETER                    | TEST COND                                                               | ITIONS                      | PIN OR<br>FREQUENCY                  | MIN                            | TYP MAX                        | UNIT  |

|------------------------|------------------------------|-------------------------------------------------------------------------|-----------------------------|--------------------------------------|--------------------------------|--------------------------------|-------|

| V <sub>IH</sub>        | High level input voltage     |                                                                         |                             | GPIO[7:0], PDB,                      | 0.65 ×<br>V <sub>(VDDIO)</sub> | V <sub>(VDDIO)</sub>           |       |

| V <sub>IL</sub>        | Low level input voltage      | $V_{\text{(VDDIO)}} = 1.71 \text{ to } 1.89^{\circ}$                    | V                           | REFCLK                               | GND                            | 0.35 ×<br>V <sub>(VDDIO)</sub> | V     |

|                        |                              | V <sub>IN</sub> = V <sub>(VDDIO)</sub> = 1.71 to<br>pulldown enabled    | 1.89 V, internal            | GPIO[7:0], PDB                       | 45                             | 115                            | μΑ    |

| I <sub>IH</sub>        | Input high current           | V <sub>IN</sub> = V <sub>(VDDIO)</sub> = 1.71 to pulldown disabled      | 1.89 V, internal            | GPIO[7:0],<br>REFCLK                 |                                | 20                             | μA    |

| I <sub>IL</sub>        | Input low current            | V <sub>IN</sub> = 0 V                                                   |                             | GPIO[7:0], PDB,<br>REFCLK            | -20                            | 3.5                            | μΑ    |

| I <sub>IN-STRAP</sub>  | Strap pin input current      | $V_{IN} = 0 \text{ V to } V_{(VDD18)}$                                  |                             | MODE, IDX                            | -1                             | 1                              | μA    |

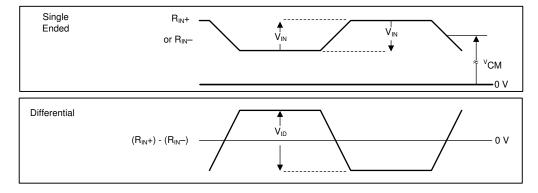

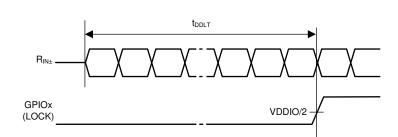

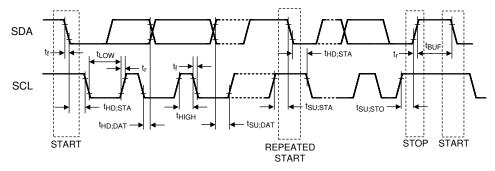

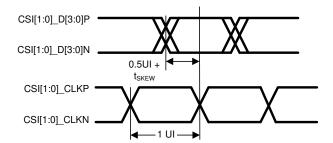

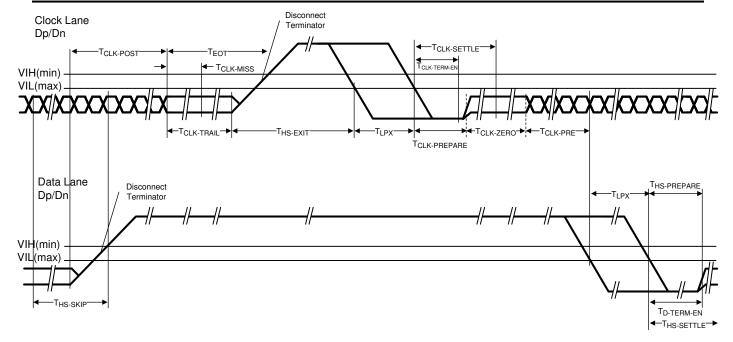

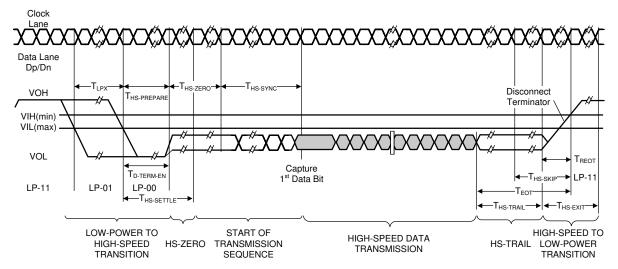

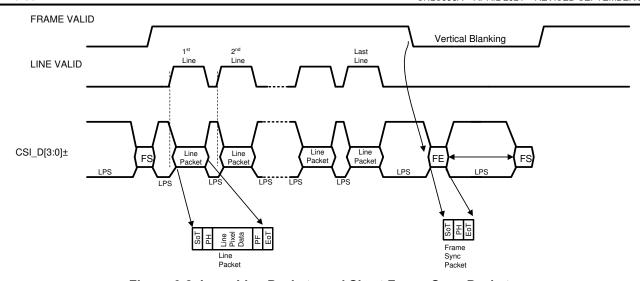

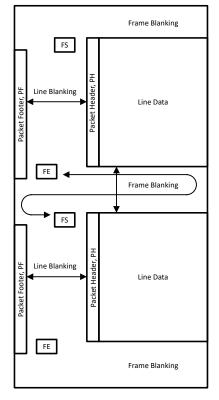

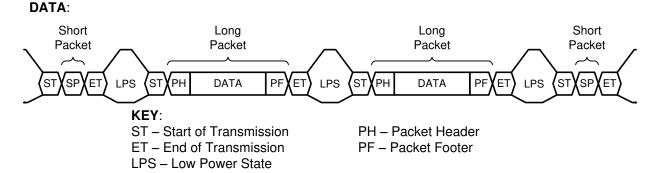

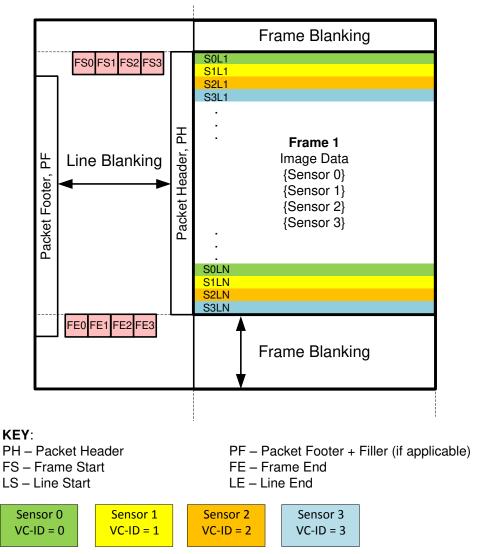

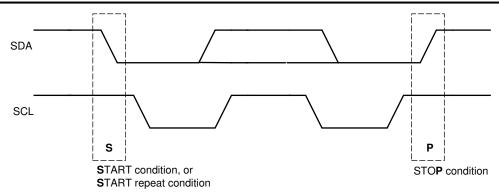

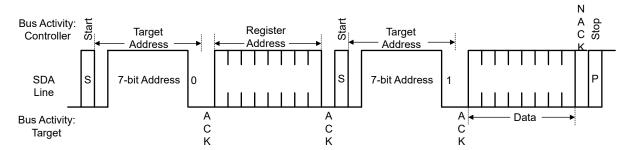

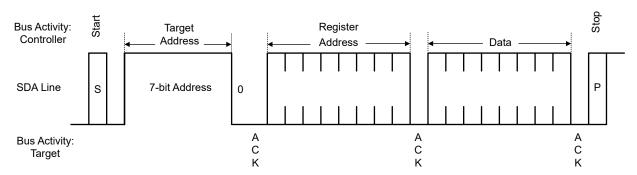

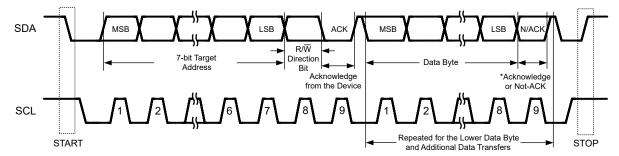

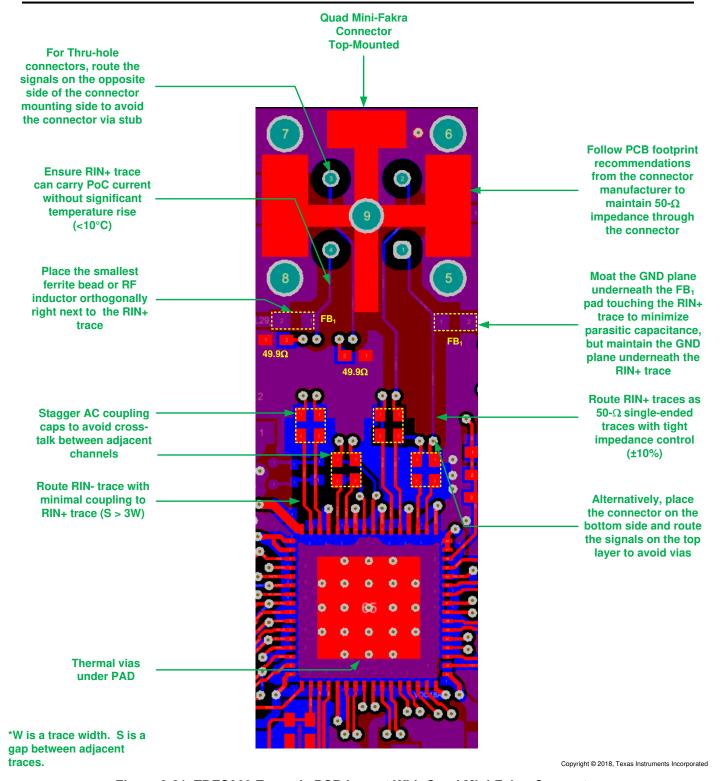

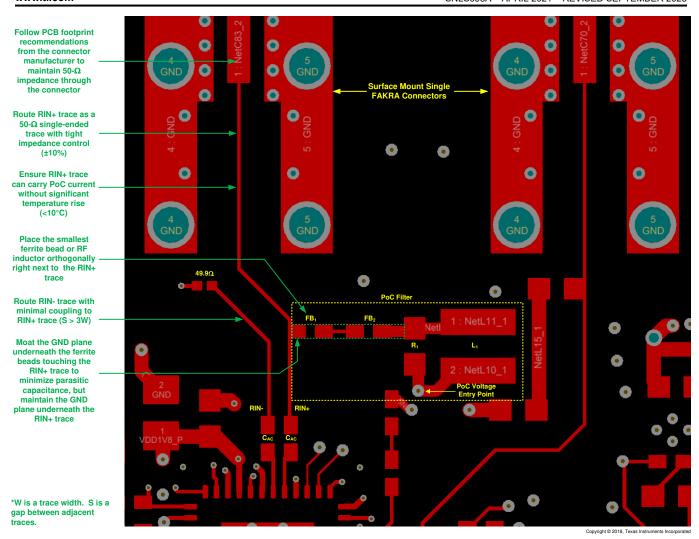

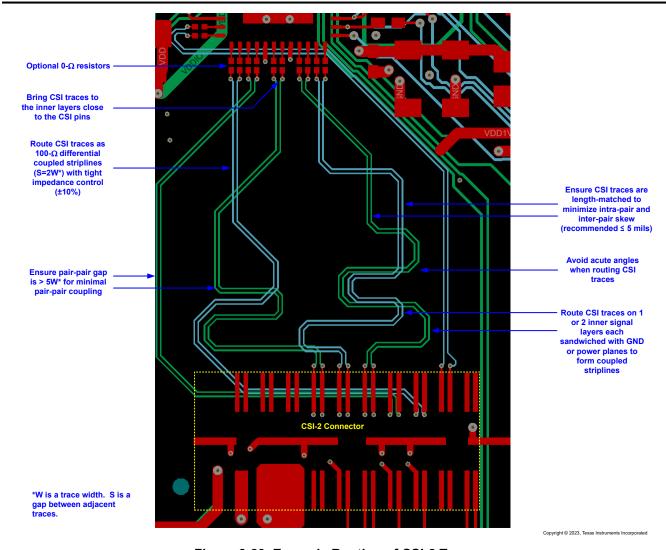

| I <sub>OS</sub>        | Output short circuit current | V <sub>OUT</sub> = 0 V                                                  |                             | GPIO[7:0]                            |                                | -40                            | mA    |