**TAS2781** SLOSE86B - JULY 2022 - REVISED JULY 2023

# TAS2781 24-V Class-D Amplifier with Real Time Integrated Speaker Protection and **Audio Processing**

### 1 Features

## **Key Features**

- Integrated DSP for audio processing

- 24-V Supply for class-d output stage

- Y-Bridge multi-level supply architecture

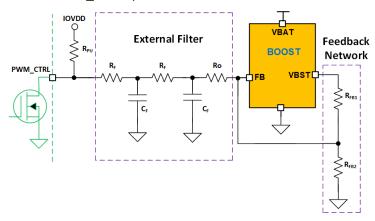

- Hybrid-pro external boost control algorithm

- Ultrasonic output support up to 40 kHz

## Output power:

- 25 W, 1% THD+N (4 Ω, 18 V)

- 30 W Maximum output power, 10% THD+N

## Efficiency (1% THDN) and power consumption

- 82% at 1W, 4  $\Omega$ , PVDDH = 12 V, PVDDL = 3.8 V

- 83% at 1W. 8  $\Omega$ . PVDDH = 18 V. PVDDL = 5 V

- 84% at 1W, 4  $\Omega$ , PVDDH = 18 V, PVDDL = 5 V

- 90% at 15W, 4  $\Omega$ , PVDDH = 18 V, PVDDL = 5 V

- 93% at 15W , 8  $\Omega$ , PVDDH = 18 V, PVDDL = 5 V

- <0.5 µA in Hardware Shutdown Mode

## Power supplies and management:

AVDD: 1.8 V

IOVDD: 1.8 V/ 3.3 V PVDDL: 2.7 V to 5.5 V PVDDH: 3 V to 24 V

### Interfaces and Control:

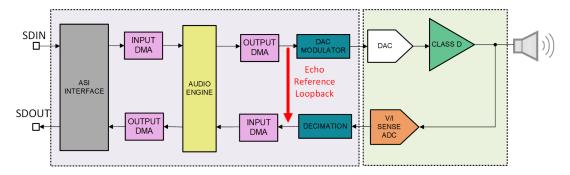

- SDOUT for echo cancellation

- I<sup>2</sup>S/TDM: 8 channels of 32 bits up to 192 KSPS

- I<sup>2</sup>C with fast mode+ or SPI

- Inter-chip communication bus

- 16 kHz to 192 kHz sample rates

## Advanced DSP audio processing:

- Real-time IV-sense for speaker protection

- Dynamic range compressor

- Brownout protection with power limiter

- Multi-channel balancing communication

#### Protection and EMI:

- Over power and low battery protection

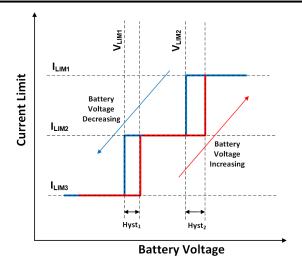

- PVDDH/ PVDDL supply tracking limiters

- Thermal and over current protections

- Thermal foldback

- Post filter feedback and slew rate control

## 2 Applications

- **Laptop and Desktop Computers**

- **Smart Speakers**

- **Tablets and Handhelds**

- Wireless Speakers

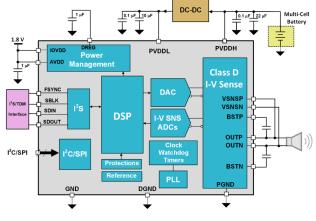

## 3 Description

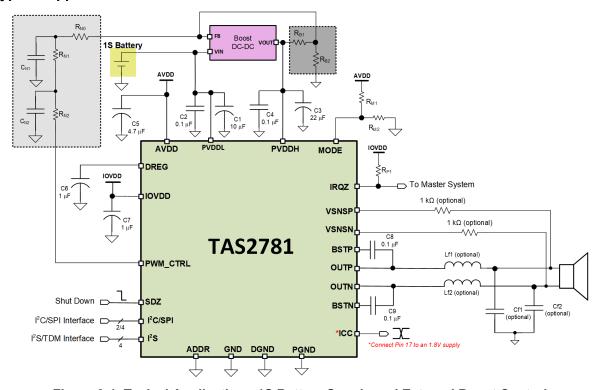

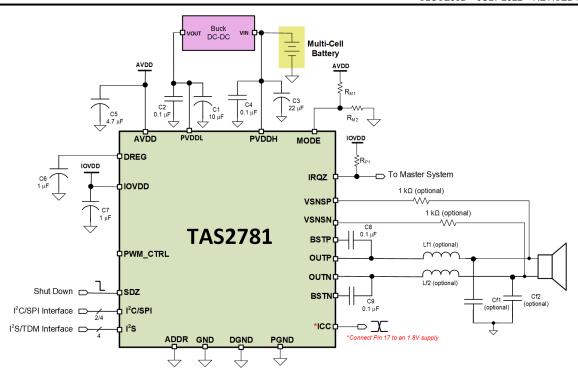

The TAS2781 is a mono, digital input Class-D audio amplifier optimized for efficiently driving high peak power into loudspeakers. The Class-D amplifier is capable of delivering 25 W of continuous power into a 4  $\Omega$  load with less than 1% THD+N at a supply voltage of 18 V. The broad voltage input range and the high output power makes this amplifier versatile enough to work with battery or line powered systems.

An on-chip DSP supports Texas Instruments Smart Amp speaker protection algorithm. The integrated speaker voltage and current sense provides for realtime monitoring of loudspeakers.

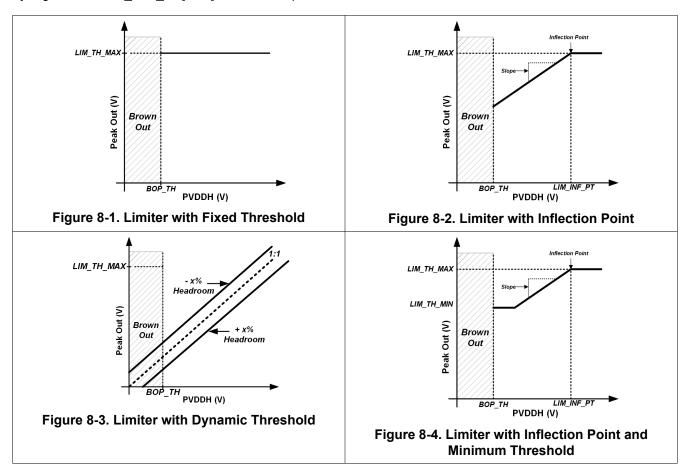

Y-Bridge power architecture improves amplifier efficiency by internally selecting the supplies for optimal headroom. Brownout prevention scheme with adjustable threshold allows reducing the gain in signal path when the supply drops.

The Hybrid-Pro algorithm allows user to optimize efficiency and improve battery life by controlling the external power supply.

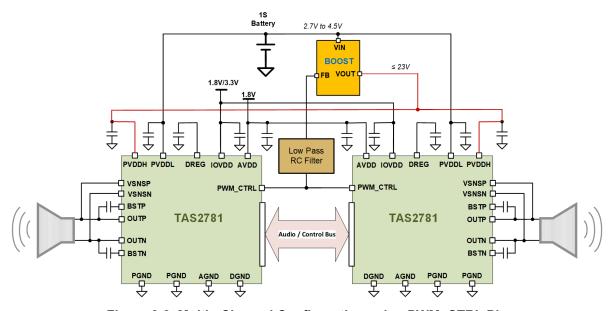

Up to eight TAS2781 devices can share a common bus via I<sup>2</sup>S/TDM and I<sup>2</sup>C/SPI interfaces.

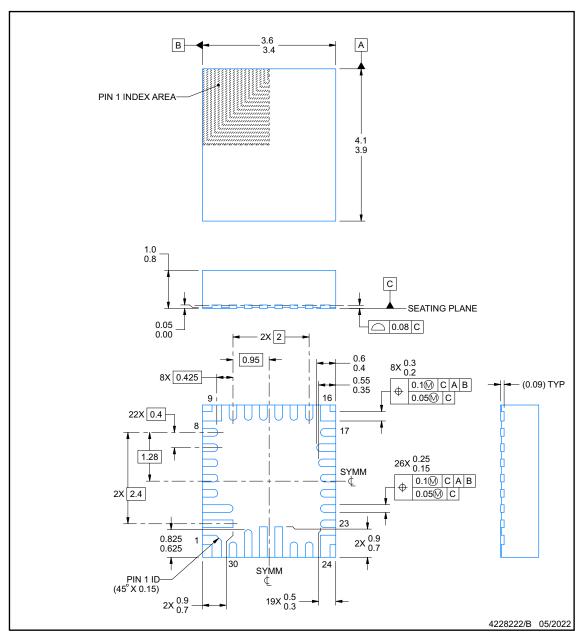

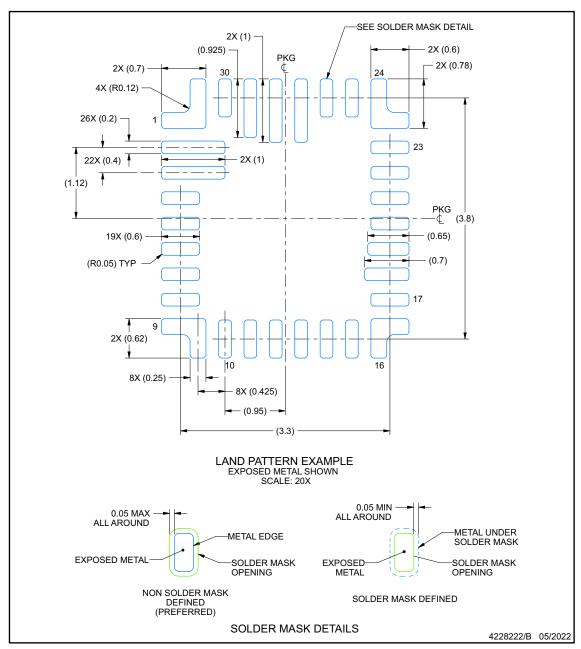

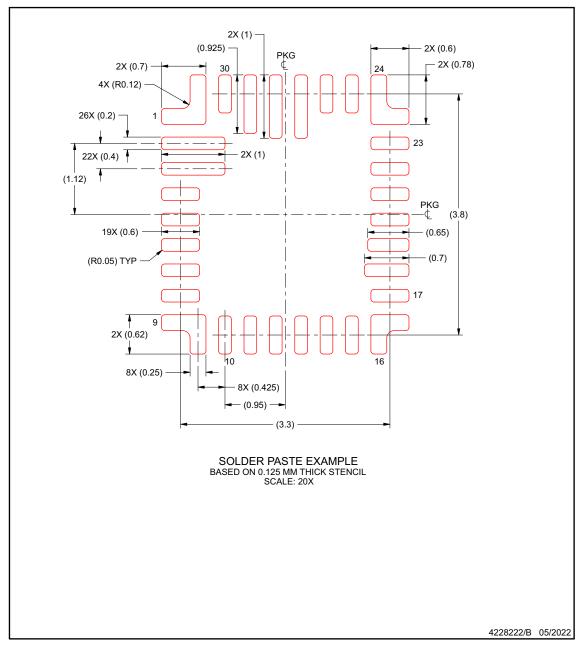

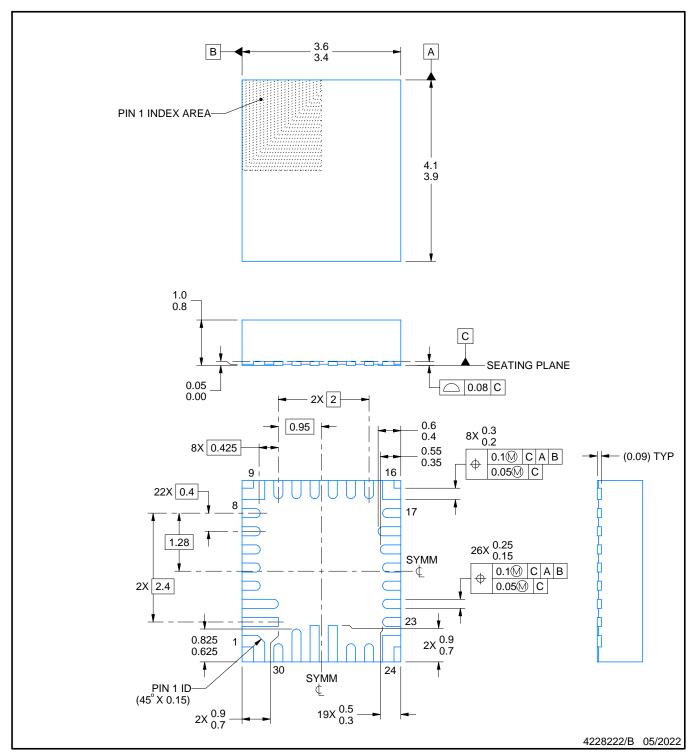

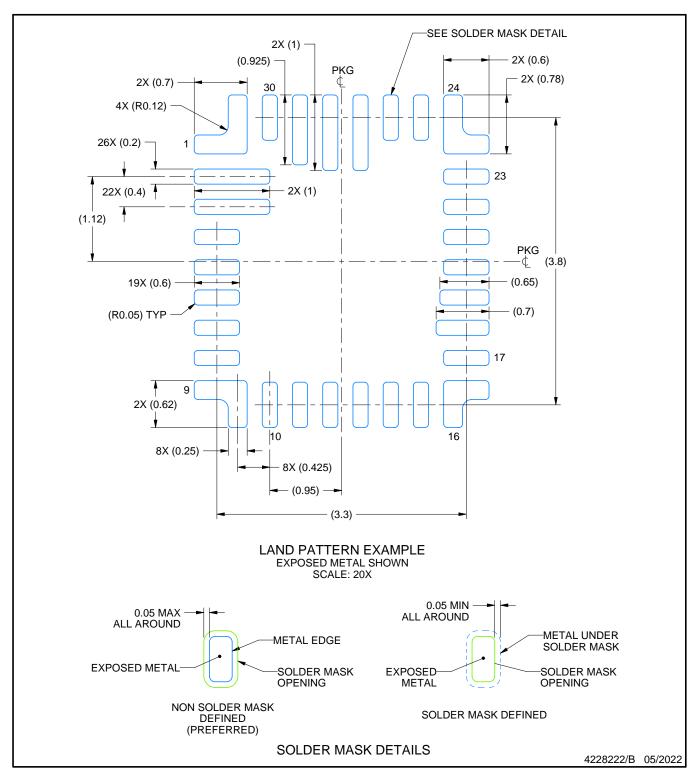

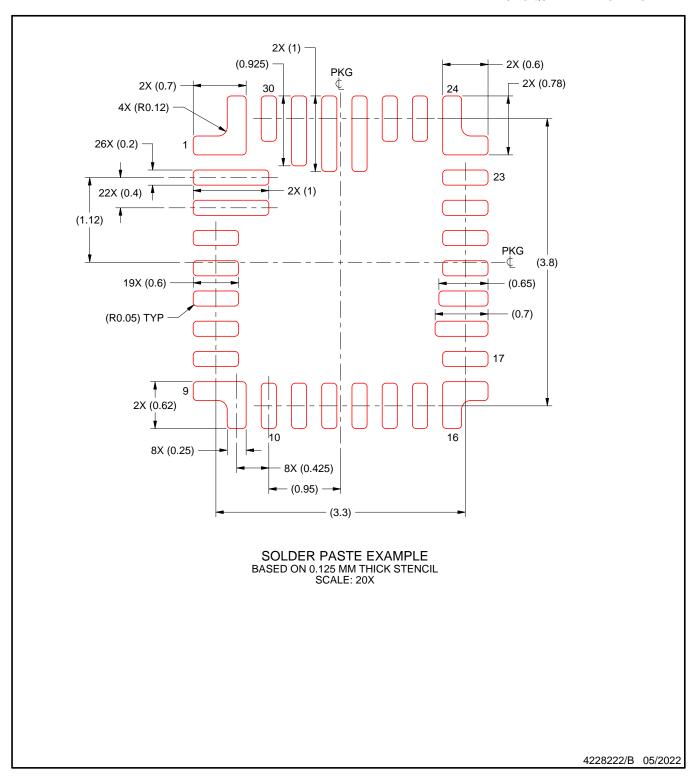

The TAS2781 is available in a 30 pin HR-QFN package for a compact PCB footprint.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|-------------|---------|-----------------|

| TAS2781     | HR QFN  | 4 mm x 3.5 mm   |

For all available packages, see the orderable addendum at the end of the data sheet.

**Schematic**

## **Table of Contents**

| 1 Features                               | 1              | 9 Application and Implementation                      | 68   |

|------------------------------------------|----------------|-------------------------------------------------------|------|

| 2 Applications                           | 1              | 9.1 Application Information                           | . 68 |

| 3 Description                            | 1              | 9.2 Typical Application                               | . 68 |

| 4 Revision History                       | <mark>2</mark> | 9.3 Design Requirements                               | . 70 |

| 5 Pin Configuration and Functions        | 3              | 9.4 Detailed Design Procedure                         | 70   |

| 6 Specifications                         | 4              | 9.5 Application Curves                                |      |

| 6.1 Absolute Maximum Ratings             | 4              | 10 Initialization Set Up                              | . 72 |

| 6.2 ESD Ratings                          | <del>5</del>   | 10.1 Initial Device Configuration - Power Up and      |      |

| 6.3 Recommended Operating Conditions     | 5              | Software Reset                                        | 72   |

| 6.4 Thermal Information                  |                | 10.2 Initial Device Configuration - PWR_MODE0         | 72   |

| 6.5 Electrical Characteristics           | 5              | 10.3 Initial Device Configuration - PWR_MODE1         | 73   |

| 6.6 I <sup>2</sup> C Timing Requirements | 11             | 10.4 Initial Device Configuration - PWR_MODE2         | 73   |

| 6.7 TDM Port Timing Requirements         | 12             | 10.5 Initial Device Configuration - PWR_MODE3         | 74   |

| 6.8 SPI Timing Requirements              | 13             | 11 Power Supply Recommendations                       | 75   |

| 6.9 Typical Characteristics              |                | 11.1 Power Supply Modes                               | . 75 |

| 7 Parameter Measurement Information      |                | 12 Layout                                             | 76   |

| 8 Detailed Description                   | 18             | 12.1 Layout Guidelines                                | . 76 |

| 8.1 Overview                             | 18             | 12.2 Layout Example                                   | . 76 |

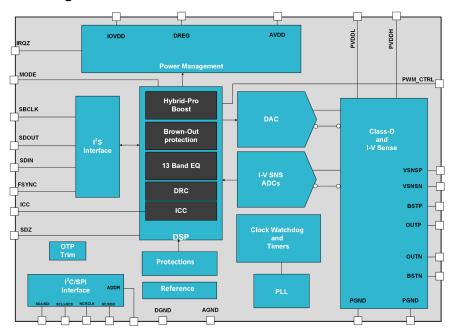

| 8.2 Functional Block Diagram             | 19             | 13 Device and Documentation Support                   | 78   |

| 8.3 Feature Description                  | 19             | 13.1 Receiving Notification of Documentation Updates. | 78   |

| 8.4 Device Functional Modes              | 20             | 13.2 Community Resources                              | 78   |

| 8.5 Operational Modes                    | 31             | 13.3 Trademarks                                       | 78   |

| 8.6 Faults and Status in TAS2781         | 32             | 14 Mechanical, Packaging, and Orderable               |      |

| 8.7 Power Sequencing Requirements        | 34             | Information                                           | . 79 |

| 8.8 Digital Input Pull Downs             | 34             | 14.1 Package Option Addendum                          | 80   |

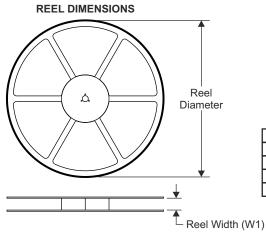

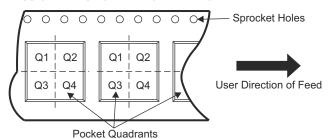

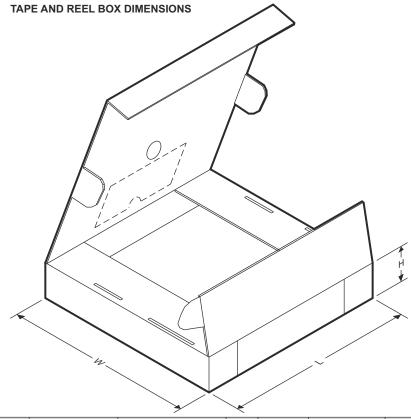

| 8.9 Register Map                         | 34             | 14.2 Tape and Reel Information                        | 81   |

| 8.10 SDOUT Equations                     | 67             |                                                       |      |

|                                          |                |                                                       |      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (November 2022) to Revision B (July 2023)                                            | Page |

|--------------------------------------------------------------------------------------------------------------|------|

| Updated PVDD to 24 V with -20° C temp condition footnote in Absolute Maximu Recommended Operating Conditions |      |

| Clarifications to edge rate register description                                                             | 34   |

| PFFB feature recommendation for ferrite bead filters                                                         |      |

| Startup configuration script added to fix power-up pop issue                                                 | 72   |

| Changes from Revision * (July 2022) to Revision A (November 2022)                                            | Page |

| Change device status from "Advanced Information" to "Production Data."                                       | 1    |

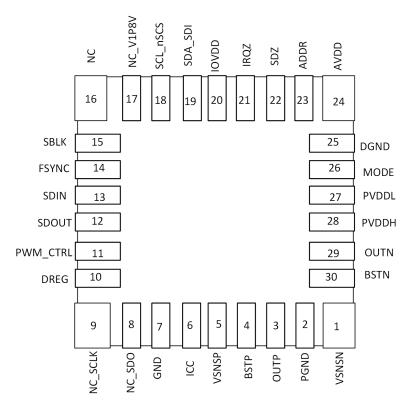

# **5 Pin Configuration and Functions**

Figure 5-1. Package 30-Pin HR-QFN Bottom View

**Table 5-1. Pin Functions**

| PI      | IN  | 1/0   | DESCRIPTION                                                                                                             |  |  |

|---------|-----|-------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO. | _ 1/0 | DESCRIPTION                                                                                                             |  |  |

| ADDR    | 23  | I     | Address detect pin. Resistor value at this pin selects the I <sup>2</sup> C address. See Section 8.3.2.                 |  |  |

| AVDD    | 24  | Р     | Analog power input. Connect to 1.8 V supply and decouple to GND with capacitor.                                         |  |  |

| BSTN    | 30  | Р     | Class-D negative bootstrap. Connect a capacitor between BSTN and OUTN.                                                  |  |  |

| BSTP    | 4   | Р     | Class-D positive bootstrap. Connect a capacitor between BSTP and OUTP.                                                  |  |  |

| DGND    | 25  | Р     | Device substrate ground. Connect to PCB ground plane. Avoid any common routing inductance between this pin and GND pin. |  |  |

| DREG    | 10  | Р     | Digital core voltage regulator output. Bypass to GND with a capacitor. Do not connect to external load.                 |  |  |

| FSYNC   | 14  | I     | Frame Synchronization Clock.                                                                                            |  |  |

| GND     | 7   | Р     | Analog ground. Connect to PCB ground plane.                                                                             |  |  |

| ICC     | 6   | Ю     | Inter-chip communication pin used to transmit gain alignment. Connect to GND if not used.                               |  |  |

| IOVDD   | 20  | Р     | Digital IO Supply. Connect to 1.8 V or 3.3 V IO supply and decouple with a capacitor to GND.                            |  |  |

| IRQZ    | 21  | 0     | Open drain, active low interrupt pin. Pull up to IOVDD with resistor if optional internal pull up is not used.          |  |  |

| MODE    | 26  | I     | External configuration defines the mode of operation.                                                                   |  |  |

| NC      | 16  | -     | Tied to GND.                                                                                                            |  |  |

| NC_SCLK | 9   | I     | I <sup>2</sup> C Mode: NC = Tied to GND,<br>SPI Mode: Clock pin.                                                        |  |  |

| NC_SDO  | 8   | 0     | I <sup>2</sup> C Mode: NC = Tied to GND,<br>SPI Mode: Serial data output pin.                                           |  |  |

## **Table 5-1. Pin Functions (continued)**

| PII      | N   | 1/0   | DESCRIPTION                                                                                                                                                              |

|----------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | - I/O | DESCRIPTION                                                                                                                                                              |

| NC_V1P8V | 17  | Р     | NC_V1P8V = Tied to GND when ICC is not used and when SPI interface is not required, NC_V1P8V = Tied to 1.8 V supply when ICC is used and when SPI interface is required, |

| OUTN     | 29  | 0     | Class-D negative output.                                                                                                                                                 |

| OUTP     | 3   | 0     | Class-D positive output.                                                                                                                                                 |

| PGND     | 2   | Р     | Class-D ground. Connect to PCB ground plane.                                                                                                                             |

| PVDDH    | 28  | Р     | Class-D power supply input. Decouple with a capacitor.                                                                                                                   |

| PVDDL    | 27  | Р     | Single-cell battery supply input. Decouple with a capacitor.                                                                                                             |

| PWM_CTRL | 11  | 0     | Control pin for external boost converter.                                                                                                                                |

| SBCLK    | 15  | I     | TDM Serial Bit Clock.                                                                                                                                                    |

| SCL_nSCS | 18  | 1     | I <sup>2</sup> C Mode: Clock pin; pull up to IOVDD with a resistor. SPI Mode: Active low chip select pin.                                                                |

| SDA_SDI  | 19  | Ю     | I <sup>2</sup> C Mode: Data Pin; pull up to IOVDD with a resistor.<br>SPI Mode: Serial data input pin.                                                                   |

| SDIN     | 13  | I     | TDM Serial Data Input.                                                                                                                                                   |

| SDOUT    | 12  | Ю     | TDM Serial Data Output.                                                                                                                                                  |

| SDZ      | 22  | I     | Active low hardware shutdown.                                                                                                                                            |

| VSNSN    | 1   | I     | Voltage Sense negative input. Connect to Class-D negative output or after a ferrite bead filter.                                                                         |

| VSNSP    | 5   | I     | Voltage Sense positive input. Connect to Class-D positive output or after a ferrite bead filter.                                                                         |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

|                                                                                          |                                                                           | MIN  | MAX | UNIT |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|-----|------|

| Supply Voltage                                                                           | AVDD                                                                      | -0.3 | 2   | V    |

|                                                                                          | IOVDD                                                                     | -0.3 | 5   | V    |

|                                                                                          | NC_V1P8V                                                                  | -0.3 | 2   | V    |

|                                                                                          | PVDDH                                                                     | -0.3 | 26  | V    |

|                                                                                          | PVDDL                                                                     | -0.3 | 6   | V    |

|                                                                                          | PVDDH - PVDDL                                                             | -0.3 | 22  | V    |

| Internal Supply Voltage                                                                  | DREG                                                                      | -0.3 | 1.5 | V    |

| IO Voltage <sup>(1)</sup>                                                                | SBLK, FSYNK,<br>SDIN, SDOUT, IRQZ,<br>SDA_SDI, SCL_nSCS,<br>PWM_CTRL, SDZ | -0.3 | 5   | V    |

| IO Voltage <sup>(1)</sup>                                                                | NC_SCLK, NC_SDO, ICC, ADDR                                                | -0.3 | 2   | V    |

| Operating free-air temperature, T <sub>A</sub> ; Device is functional and reliable, some | PVDD is 23 V or below                                                     | -40  | 85  | °C   |

| performance characteristics may be degraded.                                             | PVDD higher than 23 V                                                     | -20  | 85  | °C   |

| Performance free-air temperature, T <sub>P</sub> ; All performance characteristics are m | net.                                                                      | -20  | 70  | °C   |

| Operating junction temperature, T <sub>J</sub>                                           | PVDD is 23 V or below                                                     | -40  | 150 | °C   |

|                                                                                          | PVDD higher than 23 V                                                     | -20  | 150 | °C   |

| Storage temperature, T <sub>stg</sub>                                                    |                                                                           | -65  | 150 | °C   |

(1) All digital inputs and IOs are failsafe.

## 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | v    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                      | ·                                                                                                                                                                                                                                                                                             |                                                                        | MIN  | NOM | MAX  | UNIT |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|-----|------|------|--|

| AVDD                 | Supply voltage                                                                                                                                                                                                                                                                                |                                                                        | 1.65 | 1.8 | 1.95 | V    |  |

| IOVDD                | Supply voltage                                                                                                                                                                                                                                                                                |                                                                        | 3    | 3.3 | 3.6  | V    |  |

| IOVDD                | Supply voltage  Supply voltage for log supply voltage (functional)(1)  Supply voltage (performance)  Supply voltage (functional)(1)  Supply voltage (functional)(1)  Supply voltage (functional)(1)  Supply voltage (performance)  Supply voltage (performance)  Supply voltage (performance) |                                                                        | 1.65 | 1.8 | 1.95 | ] v  |  |

| NC_V1P8V             | Supply voltage for I                                                                                                                                                                                                                                                                          | CC Pin                                                                 | 1.65 | 1.8 | 1.95 | V    |  |

| PVDDH <sup>(2)</sup> | (functional)(1)  Supply voltage                                                                                                                                                                                                                                                               | Min operating free-air and Min operating junction temperature of -20°C | 3    |     | 24   |      |  |

|                      |                                                                                                                                                                                                                                                                                               | Min operating free-air and Min operating junction temperature of -40°C | 3    |     | 23   | V    |  |

|                      |                                                                                                                                                                                                                                                                                               | Min operating free-air and Min operating junction temperature of -20°C | 4.5  |     | 24   |      |  |

|                      |                                                                                                                                                                                                                                                                                               | Min operating free-air and Min operating junction temperature of -40°C | 4.5  |     | 23   |      |  |

|                      | Supply voltage (fun-                                                                                                                                                                                                                                                                          | ctional) <sup>(1)</sup>                                                | 2.7  |     | 5.5  |      |  |

| PVDDL                | C_V1P8V  Supply voltage for Supply voltage (functional)(1)  VDDH(2)  Supply voltage (performance)  Supply voltage (performance)  VDDL  Supply voltage (performance)  Supply voltage (performance)  Supply voltage (performance)                                                               | formance with Y-bridge disabled)                                       | 3.5  |     | 5.5  | V    |  |

|                      | Supply voltage (per                                                                                                                                                                                                                                                                           | 2.7                                                                    |      | 5.5 | 1    |      |  |

| R <sub>SPK</sub>     | Speaker impedance                                                                                                                                                                                                                                                                             | Speaker impedance                                                      |      |     |      | Ω    |  |

| L <sub>SPK</sub>     | Speaker inductance                                                                                                                                                                                                                                                                            |                                                                        | 5    |     |      | μH   |  |

- (1) Device will remain functional but performance may degrade.

- (2) PVDDH supply voltage should be greater than PVDDL-0.7 V.

#### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | HR_QFN  | UNIT       |

|-----------------------|----------------------------------------------|---------|------------|

|                       | · · · · · · · · · · · · · · · · · · ·        | 30 PINS | <b>5</b> 1 |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 44.2    | °C/W       |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 22.4    | °C/W       |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 12.3    | °C/W       |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.6     | °C/W       |

| ΨЈВ                   | Junction-to-board characterization parameter | 12.1    | °C/W       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

|                      | PARAMETER                                        | TEST CONDITIONS                      | MIN       | TYP | MAX            | UNIT |

|----------------------|--------------------------------------------------|--------------------------------------|-----------|-----|----------------|------|

| DIGITAL II           | NPUT and OUTPUT                                  |                                      |           |     |                |      |

| V <sub>IH</sub>      | High-level digital input logic voltage threshold | SBLK, FSYNC, SDIN, SCL_nSCS, SDA_SDI | 0.7xIOVDD |     |                | V    |

| V <sub>IL</sub>      | Low-level digital input logic voltage threshold  | SBLK, FSYNC, SDIN, SCL_nSCS, SDA_SDI |           |     | 0.3 x<br>IOVDD | V    |

| V <sub>IH(SDZ)</sub> | High-level digital input logic voltage threshold | SDZ                                  | 0.7xAVDD  |     |                | V    |

|                                 | PARAMETER                                                                        | TEST CONDITIONS                                                                                      | MIN              | TYP   | MAX                   | UNIT |  |

|---------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|-------|-----------------------|------|--|

| V <sub>IL(SDZ)</sub>            | Low-level digital input logic voltage threshold                                  | SDZ                                                                                                  |                  |       | 0.3 x<br>AVDD         | V    |  |

| / <sub>IH(1P8V)</sub>           | High-level digital input logic voltage threshold                                 | ICC, NC_SCLK                                                                                         | 0.7xNC_V1P<br>8V |       |                       | V    |  |

| V <sub>IL(1P8V)</sub>           | Low-level digital input logic voltage threshold                                  | ICC, NC_SCLK                                                                                         |                  |       | 0.3 x<br>NC_V1P8<br>V | ٧    |  |

| V <sub>OH</sub>                 | High-level digital output voltage                                                | SDOUT; I <sub>OH</sub> = 100 μA.                                                                     | IOVDD-0.2 V      |       |                       | V    |  |

| V <sub>OL</sub>                 | Low-level digital output voltage                                                 | SDOUT; I <sub>OH</sub> = 100 μA.                                                                     |                  |       | 0.2                   | V    |  |

| V <sub>OL(I<sup>2</sup>C)</sub> | Low-level digital output voltage                                                 | SDA_SDI; I <sub>OL</sub> = -1 mA.                                                                    |                  |       | 0.2 x<br>IOVDD        | V    |  |

| V <sub>OH(1P8V)</sub>           | High-level digital output voltage                                                | NC_SDO                                                                                               | 0.8xNC_V1P<br>8V |       |                       | V    |  |

| V <sub>OL(1P8V)</sub>           | Low-level digital output voltage                                                 | NC_SDO                                                                                               |                  |       | 0.2xNC_<br>V1P8V      | V    |  |

| lıн                             | Input logic-high leakage for digital inputs                                      | All digital pins; Input = Supply Rail.                                                               | <b>–1</b>        |       | 1                     | μΑ   |  |

| lıL                             | Input logic-low leakage for digital inputs                                       | All digital pins; Input = GND.                                                                       | <b>–1</b>        |       | 1                     | μΑ   |  |

| C <sub>IN</sub>                 | Input capacitance for digital inputs                                             | All digital pins                                                                                     |                  | 5     |                       | pF   |  |

| R <sub>PD</sub>                 | Pull down resistance for IO pins when asserted on                                |                                                                                                      |                  | 18    |                       | kΩ   |  |

| Ros                             | OUT to VSNS resistors                                                            | Load disconnected                                                                                    |                  | 10    |                       | kΩ   |  |

| Ю                               | Output Current Strength                                                          | Measured at 0.4 V below supply and 0.4 V above GND.                                                  |                  | 8     |                       | mA   |  |

| AMPLIFIEF                       | RPERFORMANCE                                                                     |                                                                                                      |                  |       | '                     |      |  |

|                                 | Peak Output Power                                                                | THD+N = 10 %, PWR_MODE0 <sup>(1)</sup> , PWR_MODE1 <sup>(2)</sup>                                    |                  | 30    |                       |      |  |

| P <sub>OUT</sub>                | Maximum Continuous Output Power                                                  | THD+N = 1 %, PVDDL = 5 V, PWR_MODE0, PWR_MODE1                                                       |                  | 25    |                       | W    |  |

|                                 |                                                                                  | P <sub>OUT</sub> = 1W, PVDDL = 5 V, PWR_MODE1                                                        |                  | 84    |                       |      |  |

|                                 |                                                                                  | P <sub>OUT</sub> = 1 W, PVDDL = 5 V, PWR_MODE0                                                       |                  | 79    |                       |      |  |

|                                 | System Efficiency                                                                | P <sub>OUT</sub> = 3 W, PVDDL = 5 V, PWR_MODE0 and PWR_MODE1                                         |                  | 85    |                       | %    |  |

|                                 |                                                                                  | P <sub>OUT</sub> = 8 W, PVDDL = 5 V, PWR_MODE0 and<br>PWR_MODE1                                      |                  | 88    |                       |      |  |

| THD+N                           | Total Harmonic Distortion and                                                    | $P_{OUT} = 1 \text{ W}, f_{in} = 1 \text{ kHz}$                                                      |                  | -84   |                       | dB   |  |

| 1110.11                         | Noise                                                                            | $P_{OUT} = 1 \text{ W}, f_{in} = 6.667 \text{ kHz}$                                                  |                  | -84   |                       | ub   |  |

| MD                              | Inter-Modulation Distortion                                                      | ITU-R, 19 kHz / 20 kHz, 1:1: 12.5 W                                                                  |                  | -83   |                       | dB   |  |

|                                 |                                                                                  | A-Weighted, 20 Hz - 20 kHz, PWR_MODE0                                                                |                  | 42    |                       |      |  |

|                                 | Idle Channel Noise                                                               | A-Weighted, 20 Hz - 20 kHz, PWR_MODE2 (3)                                                            |                  | 34    |                       |      |  |

| √ <sub>N</sub>                  |                                                                                  | A-Weghted, 20 Hz - 20 kHz, PWR_MODE1                                                                 |                  | 32    |                       | μV   |  |

|                                 | Idle Channel Noise with<br>Ultrasonic Chirp (100 us duty<br>cycle, 25 ms period) | A-Weghted, 20 Hz - 20 kHz, PWR_MODE3 <sup>(4)</sup> , 1 V <sub>Peak</sub> , Register 0x73 set to E0h |                  | 34    |                       | μν   |  |

|                                 |                                                                                  | Average frequency in Spread Spectrum Mode,<br>CLASSD_SYNC=0                                          |                  | 384   |                       |      |  |

|                                 | Class-D PWM Switching                                                            | Fixed Frequency Mode, CLASSD_SYNC=0                                                                  |                  | 384   |                       |      |  |

| F <sub>PWM</sub>                | Frequency                                                                        | Fixed Frequency Mode, CLASSD_SYNC=1, f <sub>s</sub> = 44.1 kHz and 88.2 kHz                          |                  | 352.8 |                       | kHz  |  |

|                                 |                                                                                  | Fixed Frequency Mode, CLASSD_SYNC=1, $f_s$ = 48 kHz and 96 kHz                                       |                  | 384   |                       |      |  |

| V <sub>os</sub>                 | Output Offset Voltage                                                            | Idle Mode                                                                                            | -1.3             | ±0.3  | 1.3                   | mV   |  |

|                   | PARAMETER                                                  | TEST CONDITIONS                                                                                    | MIN | TYP  | MAX  | UNIT |

|-------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|------|------|------|

|                   |                                                            | A-Weighted, -60 dBFS                                                                               |     | 110  |      |      |

| NR                | Dynamic Range                                              | A-Weighted, -60 dBFS, PWR_MODE2                                                                    |     | 109  |      | dB   |

|                   |                                                            | A-Weighted, -60 dBFS, PWR_MODE0                                                                    |     | 109  |      | -    |

|                   |                                                            | A-Weighted, Referenced to 1 % THD+N Output Level                                                   |     | 110  |      |      |

| SNR               | Signal to Noise Ratio                                      | A-Weighted, Referenced to 1 % THD+N Output Level, PWR_MODE2 <sup>(1)</sup>                         |     | 110  |      | dB   |

|                   |                                                            | A-Weighted, Referenced to 1 % THD+N Output Level, PWR_MODE0                                        |     | 109  |      |      |

| ·CP               | Click and Pop Performance                                  | Idle mode, into and out of Shutdown mode, A-weighted                                               |     | 0.8  |      | mV   |

|                   | Full Scale Output Voltage                                  | f <sub>s</sub> ≤ 48 kHz                                                                            |     | 21   |      | dB\  |

|                   | Minimum Programmable Gain                                  | f <sub>s</sub> ≤ 48 kHz                                                                            |     | 11   |      |      |

|                   | Maximum Programmable Gain                                  | f <sub>s</sub> ≤ 48 kHz                                                                            |     | 21   |      | dB∖  |

|                   | Programmable Output Level<br>Step Size                     |                                                                                                    |     | 0.5  |      | dB   |

|                   | Mute attenuation                                           | Device in Software Shutdown or Muted in normal operation                                           |     | 108  |      | dB   |

|                   | Chip to Chip Group Delay                                   |                                                                                                    | -1  |      | 1    | μs   |

|                   |                                                            | PVDDH = 18 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                 |     | 118  |      |      |

|                   | PVDDH Power Supply<br>Rejection Ratio                      | PVDDH = 18 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 1 kHz                                  |     | 110  |      | dB   |

|                   | . tojosion riduo                                           | PVDDH = $18 \text{ V} + 200 \text{ mV}_{pp}$ , $f_{ripple} = 20 \text{ kHz}$                       |     | 98   |      |      |

|                   |                                                            | PVDDL = 5 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                  |     | 114  |      | dB   |

|                   | PVDDL Power Supply<br>Rejection Ratio                      | PVDDL = 5 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 1 kHz                                   |     | 109  |      |      |

|                   | rejocion redio                                             | PVDDL = 5 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                                  |     | 93   |      |      |

|                   |                                                            | AVDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                 |     | 105  |      |      |

|                   | AVDD Power Supply<br>Rejection Ratio                       | AVDD = 1.8 V + 200 mV <sub>pp</sub> , $f_{ripple}$ = 1 kHz                                         |     | 103  |      | dB   |

|                   |                                                            | AVDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                                 |     | 88   |      |      |

|                   |                                                            | PVDDH, 217 Hz, 100-mVpp, Input f = 1 kHz @ 400 mW                                                  |     | -120 |      |      |

|                   | Power Supply Inter-                                        | PVDDL,217 Hz, 100-mVpp, Input f = 1 kHz @ 400 mW                                                   |     | -120 |      |      |

|                   | modulation                                                 | AVDD, 217 Hz, 100-mVpp, Input f = 1 kHz @ 400 mW                                                   |     | -80  |      | - dB |

|                   |                                                            | IOVDD 217 Hz, 100-mVpp, Input f = 1 kHz @ 400 mW                                                   |     | -117 |      |      |

|                   | Turn ON Time from Release                                  | No Volume Ramping                                                                                  |     | 1.13 |      |      |

|                   | of Software Shutdown                                       | Volume Ramping                                                                                     |     | 6.73 |      | ms   |

|                   | Turn OFF Time From                                         | No Volume Ramping                                                                                  |     | 0.56 |      |      |

|                   | Assertion of Software<br>Shutdown to Amp Hi-Z              | Volume Ramping                                                                                     |     | 6    |      | ms   |

|                   | Out of Hardware Shutdown to first I <sup>2</sup> C command |                                                                                                    | 1   |      |      | ms   |

|                   | SDZ timeout                                                | Exiting HW Shutdown                                                                                | 2   | 6    | 23.8 | ms   |

|                   | Turn OFF Time when                                         | $f_s$ = 48 ksps, DVC_RMP_RT[3:2] = 3h (disabled). Multiply by $48/f_s$ for differet sampling rate. |     | 1    |      |      |

|                   | Software Shutdow                                           | $f_s$ = 48 ksps, DVC_RMP_RT[3:2] = 0h (enabled). Multiply by $48/f_s$ for different sampling rate. |     | 12.5 |      | ms   |

| DIE TEN<br>SENSOF | IPERATURE<br>R                                             |                                                                                                    |     |      |      | 1    |

|                   | Resolution                                                 |                                                                                                    |     | 8    |      | bits |

|                   | Minimum Temperature<br>Measurement Range                   |                                                                                                    |     | -40  |      | °C   |

|                   | Maximum Temperature<br>Measurement Range                   |                                                                                                    |     | 150  |      | °C   |

|                   | Die Temperature Resolution                                 |                                                                                                    |     | 1    |      | °C   |

|                   | Die Temperature Accuracy                                   |                                                                                                    | -5  |      | 5    | °C   |

|       | PARAMETER                                                              | TEST CONDITIONS                                                                       | MIN TYP             | MAX | UNIT           |

|-------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------|-----|----------------|

|       | Resolution                                                             |                                                                                       | 12                  |     | bits           |

|       | D) (DD)   1 D                                                          | Minimum Level                                                                         | 2                   |     | ,,             |

|       | PVDDH Measurement Range                                                | Maximum Level                                                                         | 23                  |     | \ \ \ \        |

|       | PVDDH Resolution                                                       |                                                                                       | 22.5                |     | mV             |

|       | PVDDH Accuracy                                                         | 2 V ≤ PVDDHV ≤ 23 V                                                                   | ±60                 |     | mV             |

|       |                                                                        | Minimum Level                                                                         | 2.3                 |     |                |

|       | PVDDL Measurement Range                                                | Maximum Level                                                                         | 6                   |     | \  \ \ \ \     |

|       | PVDDL Resolution                                                       |                                                                                       | 20                  |     | mV             |

|       | PVDDL Accuracy                                                         | 2.3 V≤ PVDDL ≤ 6 V                                                                    | ±20                 |     | mV             |

| DM SE | ERIAL AUDIO PORT                                                       |                                                                                       |                     |     |                |

|       | Minimum PCM Sample Rates                                               |                                                                                       |                     |     |                |

|       | and FSYNC Input Frequency                                              |                                                                                       | 14.7                |     |                |

|       | Maximum PCM Sample<br>Rates and FSYNC Input<br>Frequency               |                                                                                       | 192                 |     | kHz            |

|       | Minimum SBCLK Input Frequency                                          | I <sup>2</sup> S/TDM Operation                                                        | 0.512               |     | NALL           |

|       | Maximum SBCLK Input Frequency                                          | I <sup>2</sup> S/TDM Operation                                                        | 24.576              |     | ⊢ MH           |

|       | SPCI // Movimum Immut litter                                           | RMS Jitter below 40 kHz that can be tolerated without performance degradation         |                     | 0.5 |                |

|       | SBCLK Maximum Input Jitter                                             | RMS Jitter above 40 kHz that can be tolerated without performance degradation         |                     | 1   | ns             |

|       | Minimum SBCLK Cycles per<br>FSYNC in I <sup>2</sup> S and TDM<br>Modes | Other Values: 24, 32, 48, 64, 96, 125, 128, 192, 250, 256, 384, 500                   | 16                  | 16  |                |

|       | Maximum SBCLK Cycles per<br>FSYNC in I <sup>2</sup> S and TDM<br>Modes | Other Values: 24, 32, 48, 64, 96, 125, 128, 192, 250, 256, 384, 500                   | 512                 |     | - Cycl         |

|       | LAYBACK<br>ACTERISTICS f <sub>s</sub> ≤ 48 kHz                         |                                                                                       |                     |     | 1              |

|       | Minimum Sample Rate                                                    |                                                                                       | 14.7                |     |                |

| 3     | Maximum Sample Rate                                                    |                                                                                       | 48                  |     | ⊢ kH:          |

|       | Passband Frequency Meeting Ripple                                      |                                                                                       | 0.454               |     | f <sub>s</sub> |

|       | Passband Ripple                                                        | 20 Hz to LPF cutoff frequency                                                         | -0.5                | 0.5 | dB             |

|       |                                                                        | ≥ 0.55 f <sub>s</sub>                                                                 | 60                  |     |                |

|       | Stop Band Attenuation                                                  | ≥ 1 f <sub>s</sub>                                                                    | 65                  |     | ⊢ dB           |

|       | Group Delay (Including Noise                                           | DC to 0.454 f <sub>s</sub> , DC blocker disabled, Class-H disabled                    | 31                  |     |                |

|       | Gate)                                                                  | DC to 0.454 f <sub>s</sub> , DC blocker disabled, Class-H enabled                     | 221                 |     | 1/f            |

| CM PI | LAYBACK                                                                |                                                                                       |                     |     |                |

|       | ACTERISTICS f <sub>s</sub> > 48 kHz                                    |                                                                                       |                     |     |                |

| •     | Minimum Sample Rates                                                   |                                                                                       | 88.2                |     | I-1 1-         |

| 3     | Maximum Sample Rate                                                    |                                                                                       | 192                 |     | - kH:          |

|       | Frequency for Passband<br>Ripple                                       | f <sub>s</sub> = 96 kHz                                                               | 0.437               |     | fs             |

|       | Passband 3db Frequency                                                 | f <sub>s</sub> = 96 kHz                                                               | 0.459               |     | f <sub>s</sub> |

|       | Passband Ripple                                                        | DC to LPF cutoff frequency                                                            | -0.5                | 0.5 | dB             |

|       | rassuariu Mppie                                                        |                                                                                       | $\geq 0.56  f_s$ 60 |     | +              |

|       |                                                                        | ≥ 0.56 f <sub>s</sub>                                                                 | 60                  |     |                |

|       | Stop Band Attenuation                                                  | -                                                                                     |                     |     | dB             |

|       | Stop Band Attenuation                                                  | ≥ 1 f <sub>s</sub>                                                                    | 65                  |     | dE             |

|       |                                                                        | ≥ 1 f <sub>s</sub> DC to 0.375 f <sub>s</sub> , DC blocker disabled, Class-H disabled | 65<br>51            |     | dE             |

| PEAK  | Stop Band Attenuation  Group Delay (Including Noise                    | ≥ 1 f <sub>s</sub>                                                                    | 65                  |     |                |

www.ti.com

|                 | PARAMETER                                               | TEST CONDITIONS                                                          | MIN  | TYP  | MAX  | UNIT             |

|-----------------|---------------------------------------------------------|--------------------------------------------------------------------------|------|------|------|------------------|

| ONR             | Dynamic Range                                           | Un-weighted, relative to 0 dBFS                                          |      | 70   |      | dB               |

| THD+N           | Total Harmonic Distortion and Noise                     | Pout = 15 W                                                              |      | -61  |      | dB               |

|                 | Full Scale Input Current                                | Measured at -6 dBFS. Re-scaled at 0 dBFS.                                |      | 5    |      | Α                |

|                 | Differential Mode Gain                                  | Pout = 1W, using a 40Hz - 40dBFS pilot tone                              | 0.98 |      | 1.02 |                  |

|                 | Frequency Response                                      | 20 Hz - 20 kHz                                                           | -0.1 |      | 0.1  | dB               |

|                 | Group Delay                                             |                                                                          |      | 22   |      | 1/f <sub>s</sub> |

| SPEAKER         | VOLTAGE SENSE                                           |                                                                          |      |      |      | ı                |

|                 | Resolution                                              |                                                                          |      | 16   |      | bits             |

| DNR             | Dynamic Range                                           | Un-weighted, relative 0 dBFS                                             |      | 73   |      | dB               |

| THD+N           | Total Harmonic Distortion and Noise                     | Pout = 15 W                                                              |      | -68  |      | dB               |

|                 | Full Scale Input Voltage                                |                                                                          |      | 16   |      | V <sub>PK</sub>  |

|                 | Differential Mode Gain                                  | Pout = 1W, using a 40Hz - 40dBFS pilot tone                              | 0.98 |      | 1.02 |                  |

|                 | Frequency Response                                      | 20 Hz - 20 kHz                                                           | -0.1 |      | 0.1  | dB               |

|                 | Group Delay                                             |                                                                          |      | 22   |      | 1/f <sub>s</sub> |

| SPEAKER         | R VOLTAGE/CURRENT SENSE F                               | RATIO                                                                    |      |      |      | -                |

|                 | Gain Linearity                                          | Pout ≥ 40 mW to 0.1% THD+N, using a 40 Hz -40 dBFS pilot tone, PWR_MODE0 | -1   |      | 1    | %                |

|                 | Gain Linearity                                          | Pout ≥ 80 mW to 0.1% THD+N, using a 40 Hz -40 dBFS pilot tone, PWR_MODE1 | -1   |      | 1    | %                |

|                 | Gain error over temperature                             | -20 °C to 70 °C, Pout = 1 W                                              |      | ±0.6 |      | %                |

|                 | Phase Error between V and I                             |                                                                          |      | 300  |      | ns               |

| PROTECT         | TION CIRCUITRY                                          |                                                                          |      |      |      |                  |

|                 | Brownout Prevention Latency to First Attack             | BOP_SRC=1                                                                |      | 400  |      | μs               |

|                 | Thermal Shutdown<br>Temperature                         |                                                                          |      | 145  |      | °C               |

|                 | Thermal Shutdown Retry                                  | OTE_RETRY=1                                                              |      | 1.5  |      | s                |

|                 | Output Over Current Limit on PVDDH                      | Output to Output, Output to GND or Output to PVDDH Short                 | 5.5  | 6.7  |      | А                |

|                 | Output Over Current Limit on PVDDL                      | Output to Output, Output to GND or Output to PVDDL Short                 | 2    | 2.6  |      | А                |

|                 | PVDDL Undervoltage Lockout                              | UVLO is asserted                                                         |      | 2    |      | V                |

|                 | Threshold                                               | UVLO is de-asserted                                                      |      | 2.16 |      | v                |

|                 | AVDD Undervoltage Lockout                               | UVLO is asserted                                                         |      | 1.45 |      | V                |

|                 | Threshold                                               | UVLO is de-asserted                                                      |      | 1.51 |      | v                |

|                 | IOVDD Undervoltage Lockout                              | UVLO is asserted                                                         |      | 1.13 |      | V                |

|                 | Threshold                                               | UVLO is de-asserted                                                      |      | 1.25 |      |                  |

|                 | PVDDL Internal LDO<br>Undervoltage Lockout<br>Threshold | UVLO is asserted                                                         |      | 4.1  |      | V                |

| CLASS-H         | CONTROLLER                                              |                                                                          |      |      |      | <u> </u>         |

|                 | Look Ahead Time                                         | Sampling Rates 48 kHz and 96 kHz                                         |      |      | 4.8  | ms               |

| BEEP PIN        | GENERATOR                                               |                                                                          |      |      |      |                  |

| f <sub>IN</sub> | SDZ Pin                                                 | Input PWM signal frequency                                               | 25.6 |      | 192  | kHz              |

| f <sub>IN</sub> | NC_SCLK Pin                                             | Input PWM signal frequency                                               | 1.6  |      | 12   | kHz              |

|                 | CURRENT CONSUMPTION                                     | 13 4                                                                     |      |      |      |                  |

|                 |                                                         | SDZ = 0, PVDDH                                                           |      | 0.05 |      |                  |

|                 |                                                         |                                                                          |      |      |      |                  |

|                 |                                                         |                                                                          |      |      |      |                  |

|                 | Hardware Shutdown                                       | SDZ = 0, PVDDL SDZ = 0, AVDD                                             |      | 0.01 |      | μA               |

| PARAMETER              | TEST CONDITIONS                                    | MIN | TYP   | MAX | UNIT |

|------------------------|----------------------------------------------------|-----|-------|-----|------|

|                        | All Clocks Stopped, PVDDH                          |     | 0.05  |     |      |

|                        | All Clocks Stopped, PVDDL                          |     | 0.5   |     |      |

| Software Shutdown      | All Clocks Stopped, AVDD                           |     | 10    |     | μA   |

|                        | All Clocks Stopped, IOVDD                          |     | 0.52  |     |      |

|                        | f <sub>s</sub> = 48 kHz, PVDDH                     |     | 0.012 |     |      |

| N . O . M .            | f <sub>s</sub> = 48 kHz, PVDDL                     |     | 0.13  |     | 1    |

| Noise Gate Mode        | f <sub>s</sub> = 48 kHz, AVDD                      |     | 8.2   |     | - mA |

|                        | f <sub>s</sub> = 48 kHz, IOVDD                     |     | 0.01  |     |      |

|                        | f <sub>s</sub> = 48 kHz, PVDDH                     |     | 0.04  |     |      |

|                        | f <sub>s</sub> = 48 kHz, PVDDL                     |     | 2.2   |     |      |

| Idle Mode - PWR_MODE1  | f <sub>s</sub> = 48 kHz, AVDD, IV Sense = Enabled  |     | 15.5  |     | mA   |

|                        | f <sub>s</sub> = 48 kHz, AVDD, IV Sense = Disabled |     | 11.8  |     |      |

|                        | $f_s = 48 \text{ kHz}, IOVDD$                      |     | 0.02  |     |      |

|                        | f <sub>s</sub> = 48 kHz, PVDDH                     |     | 3     |     |      |

| Idle Mode - PWR MODE2  | f <sub>s</sub> = 48 kHz, AVDD, IV Sense = Enabled  |     | 15.5  |     | mA   |

| Idle Mode - FWIN_MODE2 | f <sub>s</sub> = 48 kHz, AVDD, IV Sense = Disabled |     | 11.8  |     | ""   |

|                        | $f_s = 48 \text{ kHz}, IOVDD$                      |     | 0.02  |     |      |

|                        | f <sub>s</sub> = 48 kHz, PVDDH                     |     | 2.3   |     |      |

|                        | f <sub>s</sub> = 48 kHz, PVDDL                     |     | 2.1   |     |      |

| Idle Mode - PWR_MODE0  | f <sub>s</sub> = 48 kHz, AVDD, IV Sense = Enabled  |     | 15.5  |     | mA   |

|                        | f <sub>s</sub> = 48 kHz, AVDD, IV Sense = Disabled |     | 11.8  |     |      |

|                        | f <sub>s</sub> = 48 kHz, IOVDD                     |     | 0.02  |     |      |

PWR\_MODE0: CDS\_MODE=10, PVDDL\_MODE=0

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> PWR\_MODE1: CDS\_MODE=00, PVDDL\_MODE=0

<sup>(3)</sup> **PWR\_MODE2**: CDS\_MODE=11, PVDDL\_MODE=1 (4) **PWR\_MODE3**: CDS\_MODE=01, PVDDL\_MODE=0

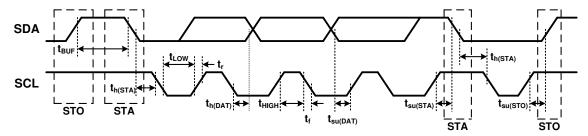

# 6.6 I<sup>2</sup>C Timing Requirements

T<sub>A</sub> = 25 °C, IOVDD = 1.8 V (unless otherwise noted)

|                     |                                                                                              | MIN                               | MAX  | UNIT |

|---------------------|----------------------------------------------------------------------------------------------|-----------------------------------|------|------|

| Standard-Mo         | ode                                                                                          |                                   |      |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0                                 | 100  | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4                                 |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 4.7                               |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 4                                 |      | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 4.7                               |      | μs   |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             |                                   | 3.45 | μs   |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             | 250                               |      | ns   |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        |                                   | 1000 | ns   |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        |                                   | 300  | ns   |

| t <sub>su;sto</sub> | Set-up time for STOP condition                                                               | 4                                 |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 4.7                               |      | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |                                   | 400  | pF   |

| Fast-Mode           |                                                                                              |                                   |      |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0                                 | 400  | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.6                               |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 1.3                               |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 0.6                               |      | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 0.6                               |      | μs   |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                                 | 0.9  | μs   |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             | 100                               |      | ns   |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        | 20 + 0.1 ×<br>C <sub>b</sub> [pF] | 300  | ns   |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        | 20 + 0.1 ×<br>C <sub>b</sub> [pF] | 300  | ns   |

| t <sub>SU;STO</sub> | Set-up time for STOP condition                                                               | 0.6                               |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 1.3                               |      | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line (10pF to 400pF)                                            |                                   | 400  | pF   |

| Fast-Mode F         | Plus                                                                                         |                                   |      |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          |                                   | 1000 | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.26                              |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 0.5                               |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 0.26                              |      | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 0.26                              |      | μs   |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                                 |      | μs   |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             | 50                                |      | ns   |

| t <sub>r</sub>      | SDA and SCL Rise Time                                                                        |                                   | 120  | ns   |

| t <sub>f</sub>      | SDA and SCL Fall Time                                                                        |                                   | 120  | ns   |

| t <sub>su;sto</sub> | Set-up time for STOP condition                                                               | 0.26                              |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 0.5                               |      | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |                                   | 550  | pF   |

Figure 6-1. I<sup>2</sup>C Timing Diagram

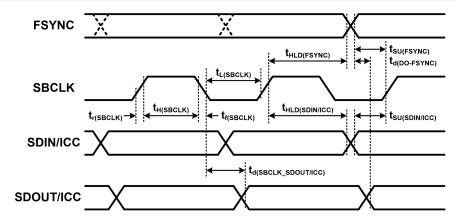

## **6.7 TDM Port Timing Requirements**

T<sub>A</sub> = 25 °C, IOVDD = NC\_V1P8V = 1.8 V, 20 pF load on all outputs(unless otherwise noted)

|                                  |                          |                                                 | MIN | MAX | UNIT |

|----------------------------------|--------------------------|-------------------------------------------------|-----|-----|------|

| t <sub>H</sub> (SBCLK)           | SBCLK high period        |                                                 | 20  |     | ns   |

| t <sub>L</sub> (SBCLK)           | SBCLK low period         |                                                 | 20  |     | ns   |

| t <sub>SU</sub> (FSYNC)          | FSYNC setup time         |                                                 | 8   |     | ns   |

| t <sub>HLD</sub> (FSYNC)         | FSYNC hold time          | FSYNC hold time                                 |     |     | ns   |

| t <sub>SU</sub> (SDIN/ICC)       | SDIN/ICC setup time      | SDIN/ICC setup time                             |     |     | ns   |

| t <sub>HLD</sub> (SDIN/ICC)      | SDIN/ICC hold time       | SDIN/ICC hold time                              |     |     | ns   |

| t <sub>d</sub> (SBCLK_SDOUT/ICC) | SBCLK to SDOUT/ICC delay | 50% of SBCLK to 50% of SDOUT/ICC, IOVDD = 1.8 V |     | 30  | ns   |

| t <sub>r</sub> (SBCLK)           | SBCLK rise time          | 10 % - 90 % Rise Time                           |     | 8   | ns   |

| t <sub>f</sub> (SBCLK)           | SBCLK fall time          | 90 % - 10 % Fall Time                           |     | 8   | ns   |

Figure 6-2. TDM and ICC Timing Diagram

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

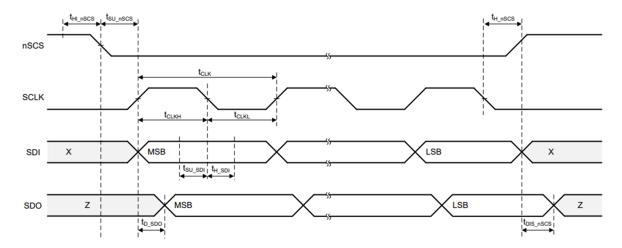

# **6.8 SPI Timing Requirements**

$T_A$  = 25 °C, NC\_V1P8V = IOVDD = 1.8 V

|                       |                                         | MIN  | NOM | MAX | UNIT |

|-----------------------|-----------------------------------------|------|-----|-----|------|

| t <sub>HI_nSCS</sub>  | nSCS Minimum High Time efore Active Low | 200  |     |     | ns   |

| t <sub>SU_nSCS</sub>  | nSCS Input Setup Time                   | 60   |     |     | ns   |

| t <sub>H_nSCS</sub>   | nSCS Input Hold Tie                     | 60   |     |     | ns   |

| t <sub>CLK</sub>      | SCLK Period                             | 60   |     |     | ns   |

| t <sub>CLKH</sub>     | SCL Pulse Width High                    | 30   |     |     | ns   |

| t <sub>CLKL</sub>     | SCLK Pulse Width Low                    | 30   |     |     | ns   |

| t <sub>SU_SDI</sub>   | SDI Input Data Setup Time               | 10.5 |     |     | ns   |

| t <sub>H_SDI</sub>    | SDI Input Data Hold Time                | 8    |     |     | ns   |

| t <sub>D_SDO</sub>    | SDO Data Output Delay                   |      |     | 25  | ns   |

| t <sub>DIS_nSCS</sub> | nSCS Disable Delay                      |      |     | 25  | ns   |

Figure 6-3. SPI Timing Diagram

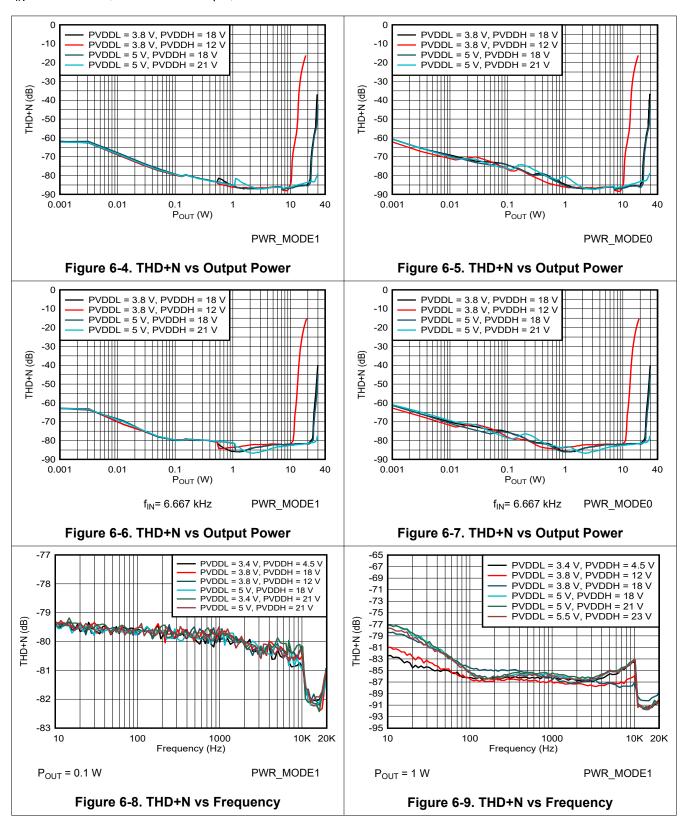

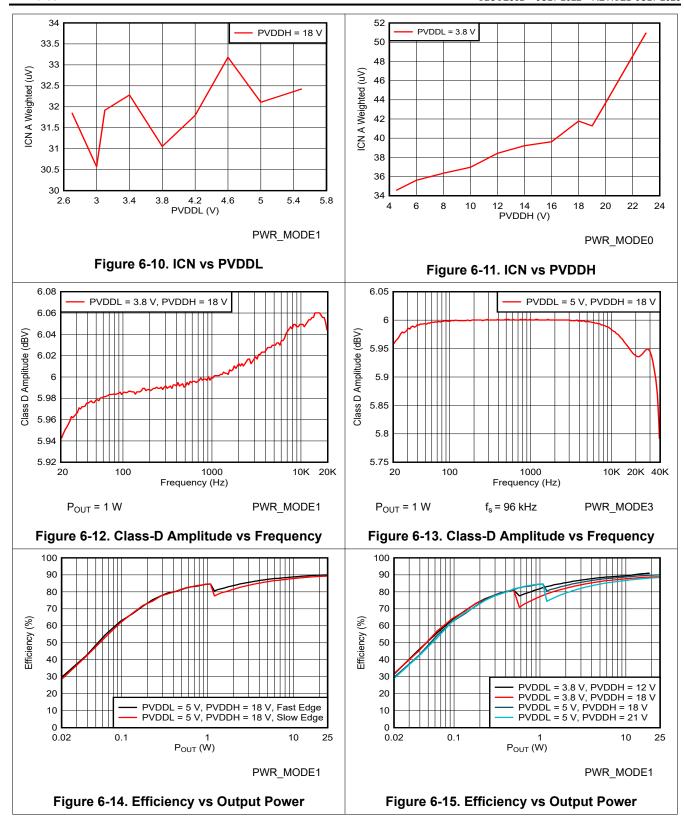

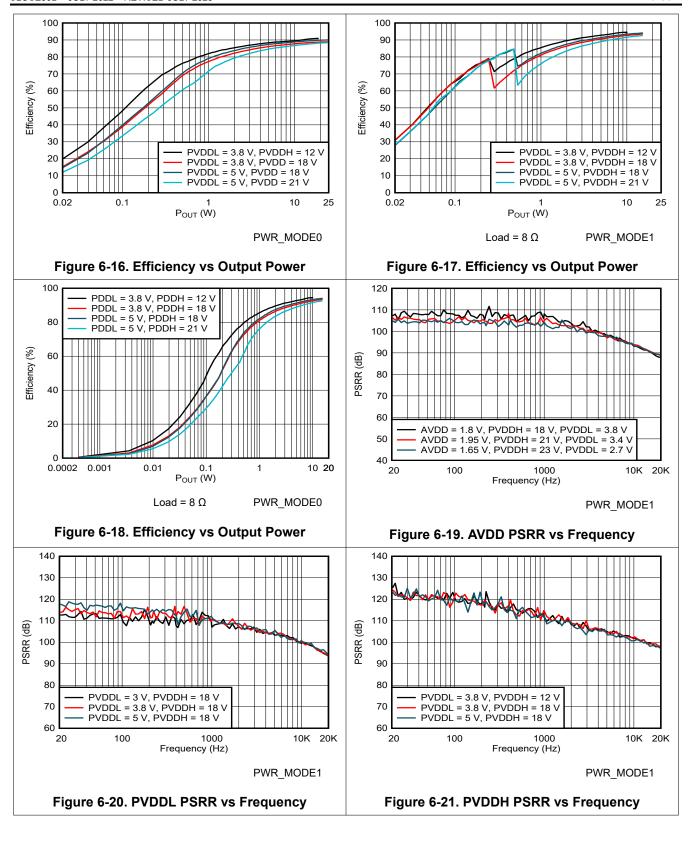

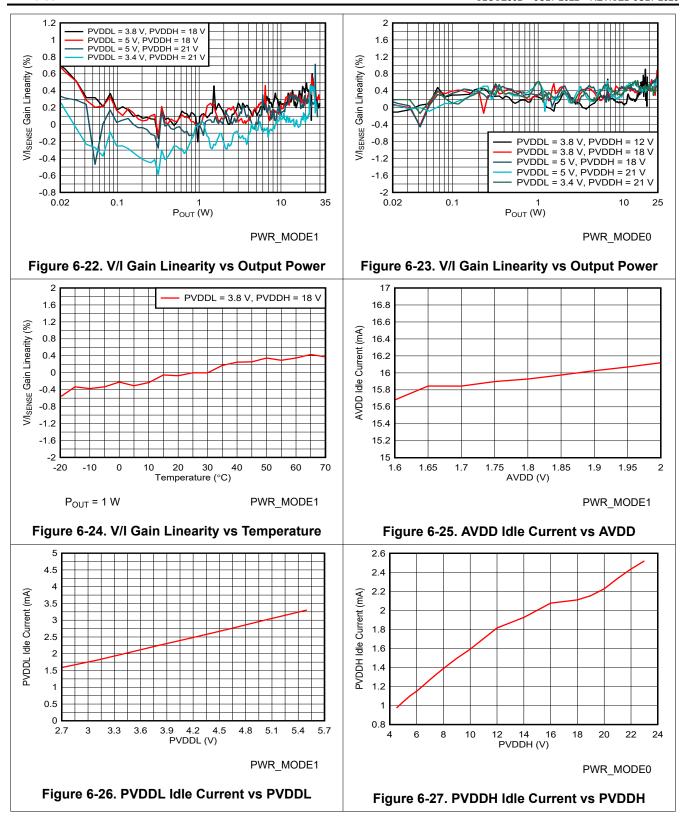

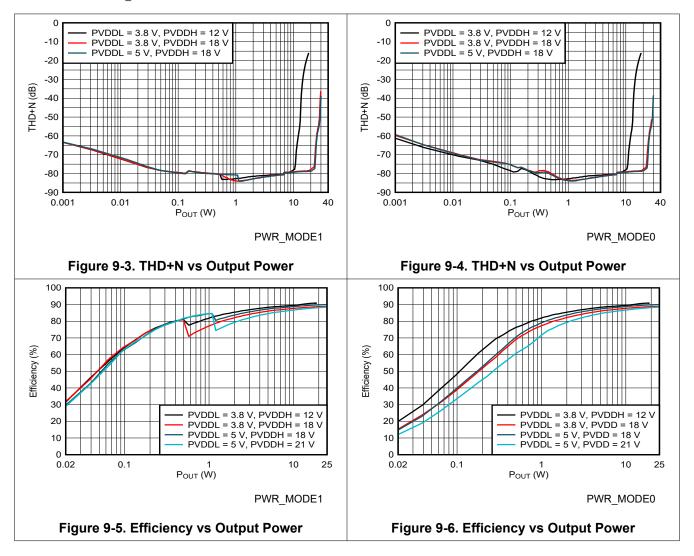

## 6.9 Typical Characteristics

At  $T_A$  = 25  $^0$ C, AVDD = 1.8 V, IOVDD = 1.8 V,  $f_s$  = 48 kHz, Class-D Switching Frequency = 384 kHz, input signal  $f_{IN}$  = 1kHz - Sine, Load = 4  $\Omega$  +15  $\mu$ H, unless otherwise noted.

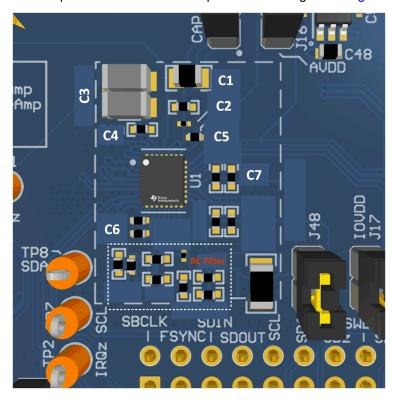

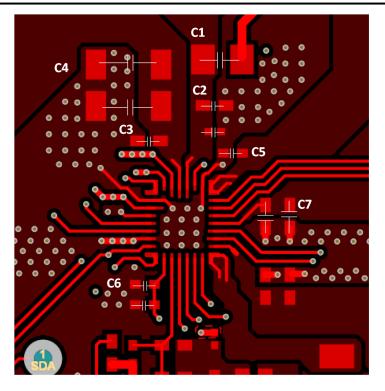

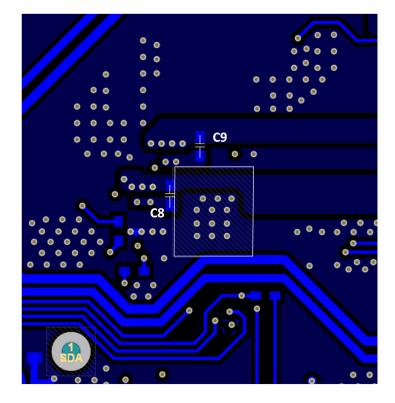

## 7 Parameter Measurement Information

The typical characteristics for the device are measured using the Bench Evaluation Module (EVM) and an Audio Precision Analyzer. A PSIA interface is used to allow the I<sup>2</sup>S interface to be driven directly into the Audio Precision Analyzer.