PGA460-Q1 SLASEC8C - FEBRUARY 2017 - REVISED FEBRUARY 2023

## PGA460-Q1 Automotive Ultrasonic Signal Processor and Transducer Driver

#### 1 Features

- Fully integrated solution for ultrasonic sensing

- AEC-Q100 qualified with the following results:

- Device temperature grade 2: -40°C to +105°C ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- Complimentary low-side drivers with configurable current limit supporting both transformer based and direct drive topology for transducer excitation

- Single transducer for both burst/listen or a transducer pair, one for burst and the other for listen operation

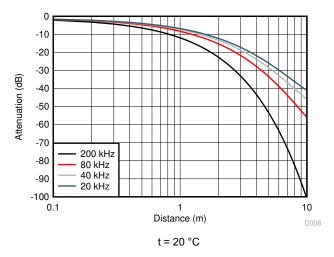

- Low-noise receiver with programmable 6-point time-varying gain (32 to 90 dB) with DSP (BPF, demodulation) for echo envelope detection

- Two presets of 12-point time-varying threshold for object detection

- Timers to measure multiple echo distance and duration

- Integrated temperature sensor

- Record time for object detection up to 11 m

- 128 bytes of RAM for echo recording

- 42 bytes of user EEPROM to store configuration for fast initialization

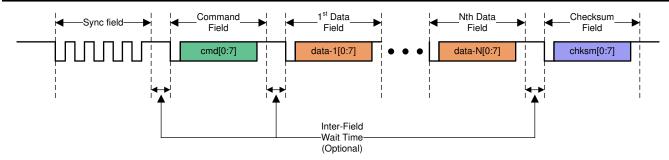

- One-wire high-voltage time-command interface or USART asynchronous interface

- CMOS level USART interface

- Sensor diagnostics (decay frequency and time, excitation voltage), supply, and transceiver diagnostics

## 2 Applications

- Ultrasonic radar

- Automotive park assist

- Lane-departure and collision warning

- Object distance and position sensing

- Presence and proximity detection

- Drone and robotics landing assist and obstacle detection

- Automotive and industrial door-opening sensing

- Automotive motion sensor for intrusion detection

- Occupancy and motion sensors

### 3 Description

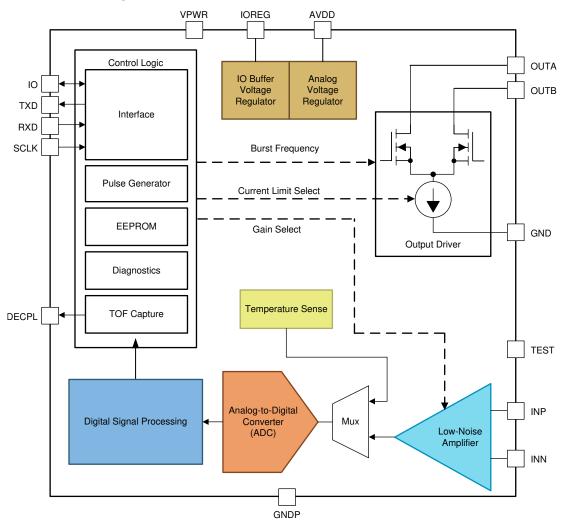

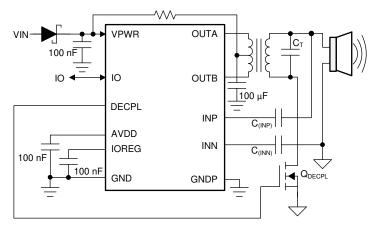

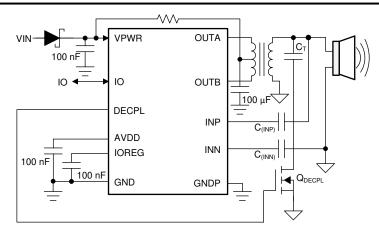

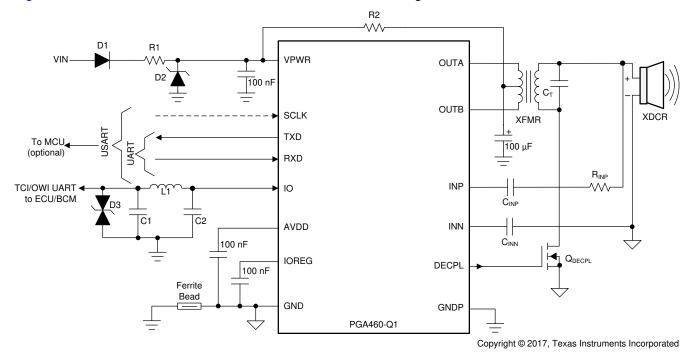

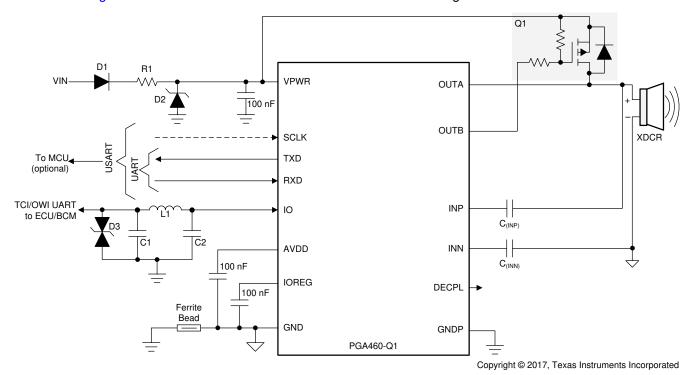

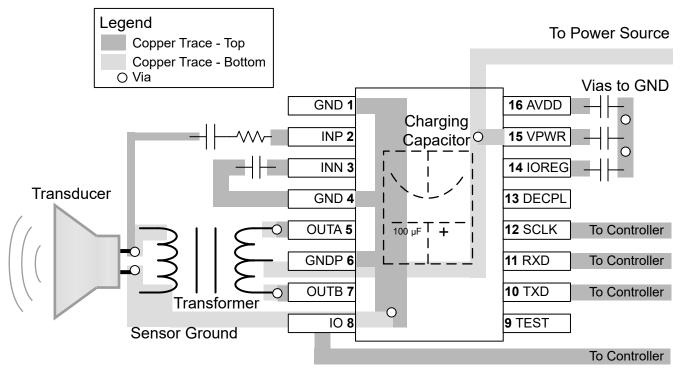

The PGA460-Q1 device is a highly-integrated system on-chip ultrasonic transducer driver and signal conditioner with an advanced DSP core. The device has a complimentary low-side driver pair that can drive a transducer either in a transformer based topology using a step-up transformer or in a directdrive topology using external high-side FETs. The device can receive and condition the reflected echo signal for reliable object detection. This feature is accomplished using an analog front-end (AFE) consisting of a low-noise amplifier followed by a programmable time-varying gain stage feeding into an ADC. The digitized signal is processed in the DSP core for both near-field and far-field object detection using time-varying thresholds.

The main communication with an external controller is achieved by either a time-command interface (TCI) or a one-wire USART asynchronous interface on the IO pin, or a CMOS-level USART interface on the RXD and TXD pins. The PGA460-Q1 can be put in ultra-low quiescent current low-power mode to reduce power consumption when not in use and can be woken up by commands on the communication interfaces.

The PGA460-Q1 also includes on-chip system diagnostics which monitor transducer voltage during burst, frequency and decay time of transducer to provide information about the integrity of the excitation as well as supply-side and transceiver-side diagnostics for overvoltage, undervoltage, overcurrent and short-circuit scenarios.

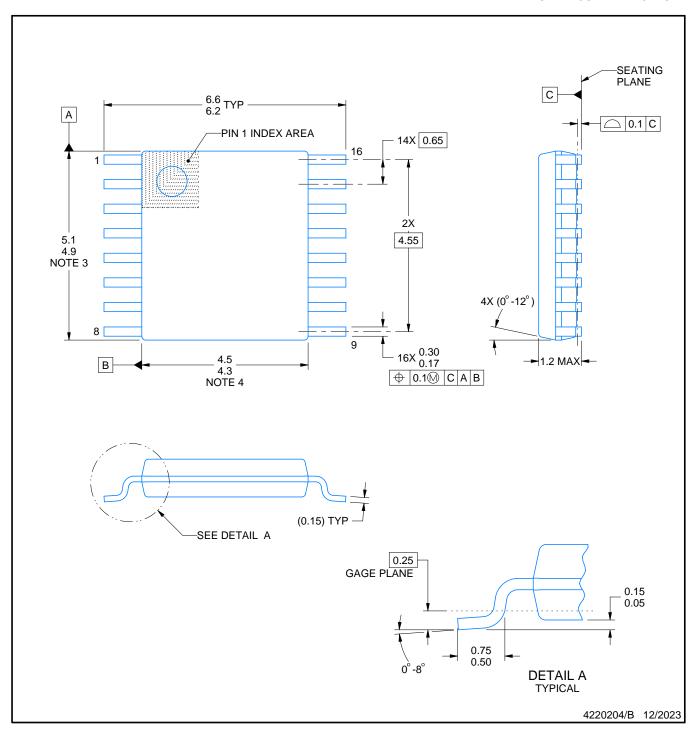

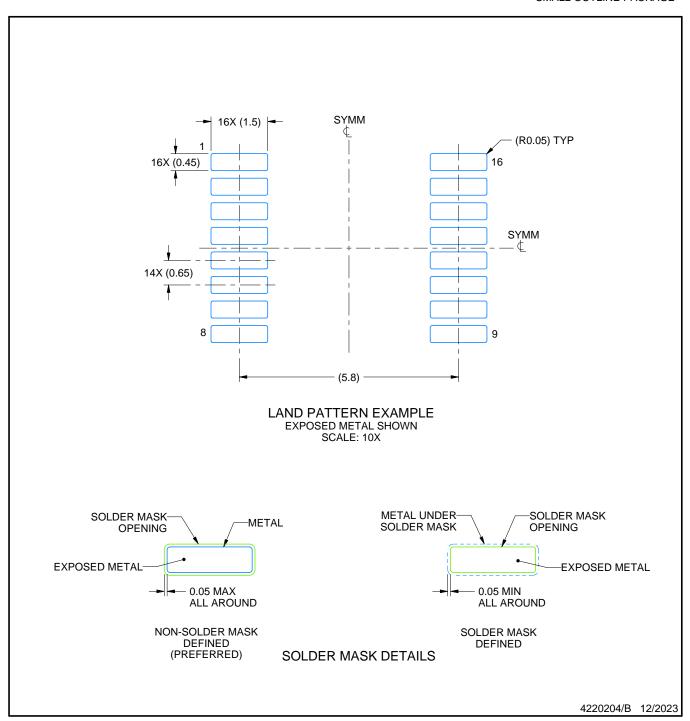

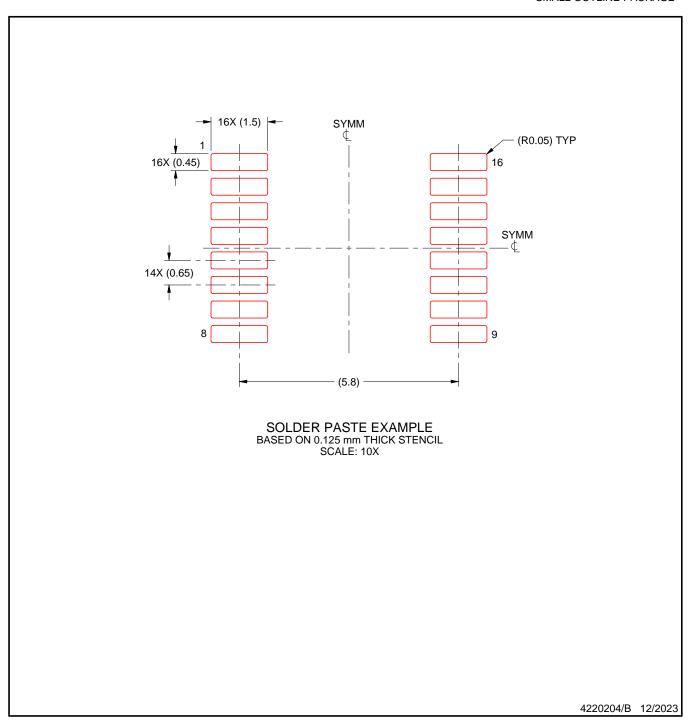

#### Package Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |  |

|-------------|------------|-------------------|--|--|

| PGA460-Q1   | TSSOP (16) | 5.00 mm × 4.40 mm |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

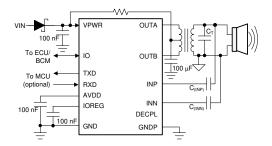

**Typical Application Diagram (Transformer Drive)**

| lab                                                                                           | le of          | Contents                                                                                             |                        |

|-----------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------|------------------------|

| 1 Features                                                                                    | 1              | 7 Detailed Description                                                                               | 10                     |

| 2 Applications                                                                                | 1              | 7.1 Overview                                                                                         |                        |

| 3 Description                                                                                 |                | 7.2 Functional Block Diagram                                                                         | 11                     |

| 4 Revision History                                                                            |                | 7.3 Feature Description                                                                              |                        |

| 5 Pin Configuration and Functions                                                             | 4              | 7.4 Device Functional Modes                                                                          | 49                     |

| 6 Specifications                                                                              |                | 7.5 Programming                                                                                      | 49                     |

| 6.1 Absolute Maximum Ratings                                                                  |                | 7.6 Register Maps                                                                                    | 52                     |

| 6.2 ESD Ratings                                                                               |                | 8 Application and Implementation                                                                     | 101                    |

| 6.3 Recommended Operating Conditions                                                          | 5              | 8.1 Application Information                                                                          | 101                    |

| 6.4 Thermal Information                                                                       | 6              | 8.2 Typical Applications                                                                             | 101                    |

| 6.5 Internal Supply Regulators Characteristics                                                | 6              | 8.3 Power Supply Recommendations                                                                     | 107                    |

| 6.6 Transducer Driver Characteristics                                                         | <mark>6</mark> | 8.4 Layout                                                                                           |                        |

| 6.7 Transducer Receiver Characteristics                                                       | 7              | 9 Device and Documentation Support                                                                   | 109                    |

| 6.8 Analog to Digital Converter Characteristics                                               | <del>7</del>   | 9.1 Documentation Support                                                                            |                        |

| 6.9 Digital Signal Processing Characteristics                                                 | 7              | 9.2 Receiving Notification of Documentation Upda                                                     | ates 1 <mark>09</mark> |

| 6.10 Temperature Sensor Characteristics                                                       | 7              | 9.3 Support Resources                                                                                | 109                    |

| 6.11 High-Voltage I/O Characteristics                                                         | 8              | 9.4 Trademarks                                                                                       | 109                    |

| 6.12 Digital I/O Characteristics                                                              | 8              | 9.5 Electrostatic Discharge Caution                                                                  | 109                    |

| 6.13 EEPROM Characteristics                                                                   | 8              | 9.6 Glossary                                                                                         | 109                    |

| 6.14 Timing Requirements                                                                      | 8              | 10 Mechanical, Packaging, and Orderable                                                              |                        |

| 6.15 Switching Characteristics                                                                | 9              | Information                                                                                          | 109                    |

| 6.16 Typical Characteristics                                                                  | 9              |                                                                                                      |                        |

| NOTE: Page numbers for previous revisions may<br>Changes from Revision B (January 2019) to Re |                |                                                                                                      | Page                   |

| <ul> <li>Updated the numbering format for tables, figur</li> </ul>                            | es, an         | d cross-references throughout the document                                                           | 1                      |

|                                                                                               |                | oller and peripheral where SPI is mentioned                                                          |                        |

|                                                                                               |                | rage Information                                                                                     |                        |

|                                                                                               |                | yout sections to the Application and Implementati                                                    |                        |

|                                                                                               |                |                                                                                                      |                        |

| Section                                                                                       |                |                                                                                                      | 107                    |

| Changes from Revision A (August 2017) to Re                                                   | vision         | B (January 2019)                                                                                     | Page                   |

| •                                                                                             |                | P pin designators for correct grounding of the Ou                                                    | •                      |

|                                                                                               |                |                                                                                                      |                        |

| •                                                                                             |                |                                                                                                      |                        |

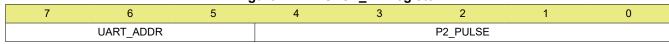

| select because the addressing is handled by the                                               | he thre        | tical to a Serial Peripheral Interface (SPI) without re-bit UART_ADDR value to enable up to eight de | evices                 |

|                                                                                               |                | ample and conversion time requires at least 100 ເ                                                    |                        |

|                                                                                               |                | Do not send other commands during this time to a                                                     |                        |

| •                                                                                             |                | <u> </u>                                                                                             |                        |

| temperature value to properly update                                                          |                |                                                                                                      | 46                     |

| Changes from Revision * (February 2017) to R                                                  | evisio         | n A (August 2017)                                                                                    | Page                   |

##

#### www.ti.com

| • | Added sentence: This includes all threshold timing and level values.                               | 49  |

|---|----------------------------------------------------------------------------------------------------|-----|

|   | Updated UART and USART Communication Examples content                                              |     |

|   | Updated content in Table 8-2                                                                       |     |

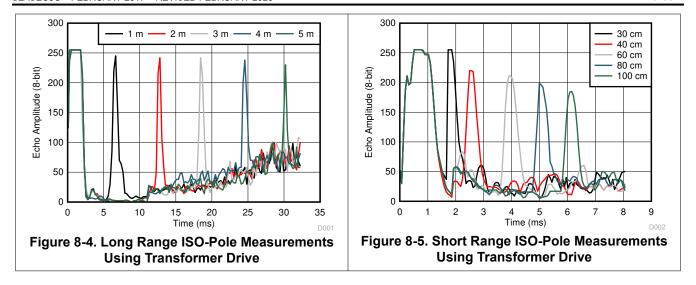

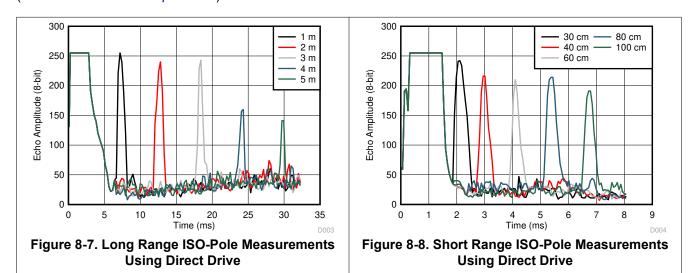

| • | Added content to Application Curves                                                                | 105 |

|   | Added content to Direct-Driven (Transformer-Less) Method and changed Figure 8-6 such that a GND no |     |

|   | present at XDCR <sub>Negative</sub> and C <sub>INN</sub>                                           | 106 |

| • | Changed text from: TDK EPCOS B78416A2232A03 Transformer, muRata MA40H1S-R transducer to:           |     |

|   | Fairchild FDC6506P p-channel MOSFET, muRata MA40H1S-R transducer                                   | 107 |

|   |                                                                                                    |     |

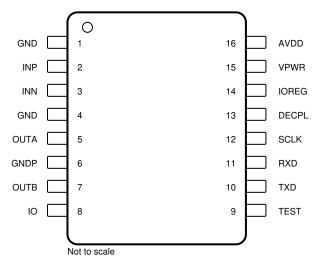

## **5 Pin Configuration and Functions**

Figure 5-1. PW Package 16-Pin TSSOP Top View

**Table 5-1. Pin Functions**

|     | PIN   |                     | DESCRIPTION                                  |  |  |  |

|-----|-------|---------------------|----------------------------------------------|--|--|--|

| NO. | NAME  | TYPE <sup>(1)</sup> | DESCRIPTION                                  |  |  |  |

| 1   | GND   | Р                   | Ground                                       |  |  |  |

| 2   | INP   | I                   | Positive transducer receive                  |  |  |  |

| 3   | INN   | I                   | tive transducer receive                      |  |  |  |

| 4   | GND   | Р                   | Ground                                       |  |  |  |

| 5   | OUTA  | 0                   | Transducer driver output A                   |  |  |  |

| 6   | GNDP  | Р                   | Power ground                                 |  |  |  |

| 7   | OUTB  | 0                   | nsducer driver output B                      |  |  |  |

| 8   | Ю     | I/O                 | Time-command interface data input and output |  |  |  |

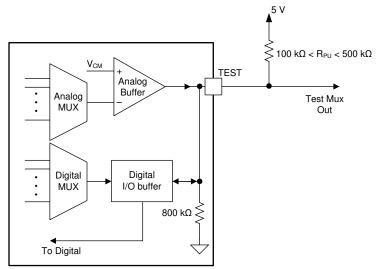

| 9   | TEST  | I/O                 | Test output pin                              |  |  |  |

| 10  | TXD   | 0                   | USART interface transmit                     |  |  |  |

| 11  | RXD   | I                   | USART interface receive                      |  |  |  |

| 12  | SCLK  | I                   | USART synchronous-mode clock input           |  |  |  |

| 13  | DECPL | 0                   | Decoupling transistor gate drive             |  |  |  |

| 14  | IOREG | Р                   | I/O buffer voltage regulator capacitor       |  |  |  |

| 15  | VPWR  | Р                   | Power-supply voltage                         |  |  |  |

| 16  | AVDD  | Р                   | Analog voltage-regulator capacitor           |  |  |  |

(1) I = input, O = output, I/O = input and output, P = power

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                       |                                       | MIN  | MAX | UNIT |

|-----------------------|---------------------------------------|------|-----|------|

| Input voltage         | VPWR                                  | -0.3 | 30  | V    |

|                       | IO                                    | -0.3 | 30  | V    |

| Input voltage         | INP, INN                              | -0.3 | 2   | V    |

|                       | TEST, SCLK, RXD                       | -0.3 | 5.5 | V    |

|                       | AVDD                                  | -0.3 | 2   |      |

| Output voltage        | IOREG, DECPL, TEST, TXD               | -0.3 | 5.5 | V    |

|                       | OUTA, OUTB                            | -0.3 | 30  |      |

| Ground voltage        | GNDP, GND                             | -0.3 | 0.3 | V    |

| Sink current          | OUTA, OUTB                            |      | 500 | mA   |

| Operating junction to | perating junction temperature -40 125 |      | 125 | °C   |

| Storage temperature   | e, T <sub>stg</sub>                   | -40  | 125 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                                            |                                                         |                           |       | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------|---------------------------|-------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                           | ±2000 |       |      |

|                                            | Charged-device model (CDM), per AEC Q100-011            | Corner Pins (1, 8, 9, 16) | ±750  | \/    |      |

|                                            |                                                         | All Other Pins            | ±500  | v     |      |

|                                            | IEC 61000-4-2 contact discharge                         | IO pin                    | ±8000 |       |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification

### **6.3 Recommended Operating Conditions**

Over operating free-air temperature range (unless otherwise noted).

|                      |                                       |                                        | MIN  | MAX                | UNIT |

|----------------------|---------------------------------------|----------------------------------------|------|--------------------|------|

| V <sub>VPWR_XF</sub> | Supply input for transformer topolog  | зу                                     | 6    | 15                 | V    |

| V <sub>VPWR_DD</sub> | Supply input for direct drive topolog | Supply input for direct drive topology |      | 28                 | V    |

| V <sub>IO</sub>      | IO pin                                | Ю                                      | -0.1 | $V_{PWR}$          | V    |

| V <sub>INx</sub>     | Transducer receive input              | INP, INN                               | -0.1 | 0.9                | V    |

| V <sub>DIG_IO</sub>  | Digital I/O pins                      | RXD, TEST, SCLK                        | -0.1 | V <sub>IOREG</sub> | V    |

| V <sub>GND</sub>     | Ground pins                           | GNDP, GND                              | -0.1 | 0.1                | V    |

| I <sub>LPM</sub>     | V Input ourrent                       | Low Power Mode Enabled                 |      | 500                | μΑ   |

| I <sub>BURST</sub>   | V <sub>PWR</sub> Input current        | During Ultrasonic Burst                |      | 500                | mA   |

| T <sub>A</sub>       | Operating free-air temperature        |                                        | -40  | 105                | °C   |

| T <sub>J</sub>       | Operating junction temperature        |                                        | -40  | 125                | °C   |

### **6.4 Thermal Information**

|                       |                                              | PGA460-Q1  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                            | PW (TSSOP) | UNIT |

|                       |                                              | 16 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 96.1       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.6       | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 42         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.8        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 41.3       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Internal Supply Regulators Characteristics

|                          | PARAMETER                                             | TEST CONDITIONS                                                                                  | MIN  | TYP  | MAX  | UNIT |  |

|--------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------|--|

| V <sub>AVDD</sub>        | Internal analog supply voltage                        | I <sub>AVDD</sub> = 5 mA                                                                         | 1.74 | 1.8  | 1.9  | V    |  |

| I <sub>VPWR_RX_ONL</sub> | Supply current from VPWR pin during listen only mode. | V <sub>VPWR</sub> = 14 V; no bursting; Listen only active                                        |      | 12   |      | mA   |  |

| V <sub>IOREG_33</sub>    | Digital IO gupply veltage                             | $V_{TEST} = 0 V during power-up ; I_{IOREG} = 2 mA$                                              | 2.95 | 3.3  | 3.65 | V    |  |

| V <sub>IOREG_50</sub>    | Digital IO supply voltage                             | $V_{TEST} \ge 2 \text{ V during power-up }; I_{IOREG} = 2 \text{ mA; } V_{VPWR} > 7.5 \text{ V}$ | 4.45 | 5    | 5.65 | V    |  |

| I <sub>LIM_AVDD</sub>    | AVDD current limit                                    | AVDD short to GND                                                                                | 40   |      | 150  | mA   |  |

| I <sub>LIM_IOREG</sub>   | IOREG current limit                                   | IOREG short to GND                                                                               | 10   |      | 50   | mA   |  |

| V <sub>OV_AVDD</sub>     | AVDD overvoltage threshold                            |                                                                                                  | 1.95 |      | 2.3  | V    |  |

| V <sub>UV_AVDD</sub>     | AVDD undervoltage threshold                           |                                                                                                  | 1.29 |      | 1.53 | V    |  |

| V <sub>OV_IOREG_33</sub> | IOREG overvoltage threshold                           | V <sub>TEST</sub> = 0 V during power-up                                                          | 3.6  |      | 4.6  | V    |  |

| V <sub>UV_IOREG_33</sub> | IOREG undervoltage threshold                          | V <sub>TEST</sub> = 0 V during power-up                                                          | 2.57 |      | 2.9  | V    |  |

| V <sub>UV_IOREG_50</sub> | TOREG undervoltage threshold                          | V <sub>TEST</sub> ≥ 2 V during power-up                                                          | 3.8  |      | 4.5  |      |  |

|                          |                                                       | VPWR_OV_TH = 0x0                                                                                 | 11   | 12.3 | 15   |      |  |

| \                        | VDWD averyeltage threshold                            | VPWR_OV_TH = 0x1                                                                                 | 16   | 17.7 | 21   | V    |  |

| V <sub>OV_VPWR</sub>     | VPWR overvoltage threshold                            | VPWR_OV_TH = 0x2                                                                                 | 21.5 | 22.8 | 27   | V    |  |

|                          |                                                       | VPWR_OV_TH = 0x3                                                                                 | 27   | 28.3 | 31   |      |  |

| V <sub>UV_VPWR</sub>     | VPWR undervoltage threshold                           |                                                                                                  | 5.25 |      | 6    | V    |  |

| t <sub>ON_REG</sub>      | AVDD and IOREG power-up time                          | V <sub>VPWR</sub> = 6 V                                                                          |      |      | 10   | ms   |  |

### **6.6 Transducer Driver Characteristics**

|                            | PARAMETER                                       | TEST CONDITIONS                                                                           | MIN | TYP | MAX | UNIT |

|----------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>CLAMP_DRV</sub>     | Driver clamping voltage                         | Driver switched off                                                                       | 30  |     |     | V    |

| I <sub>PULSE_MAX_DRV</sub> | Maximum driver pulse current                    | $V_{OUTA}, V_{OUTB} = 6 \text{ V:}$ $F_{SW} = 30 \text{ kHz; } T_A = 105^{\circ}\text{C}$ |     |     | 500 | mA   |

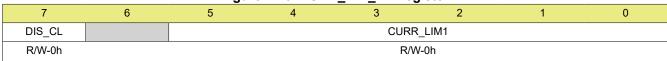

| RDSON <sub>DRV</sub>       | MOSFET on resistance                            | I <sub>DRAIN</sub> = 500 mA: T <sub>A</sub> = 105°C; DIS_CL=1                             |     | 4.8 | 8   | Ω    |

| E <sub>DIS_BURST</sub>     | Energy dissipated during burst                  |                                                                                           |     |     | 6.4 | mJ   |

| I <sub>LEAK_DRV</sub>      | Leakage current                                 | V <sub>OUTA</sub> ,V <sub>OUTB</sub> =14 V                                                | -1  |     | 1   | μA   |

| I <sub>CLAMP_DRV_0</sub>   | Current clamping range for minimum code setting | V <sub>VPWR</sub> >7<br>V;CURR_LIM1 =<br>CURR_LIM2= 0                                     | 15  | 50  | 75  | mA   |

Product Folder Links: PGA460-Q1

|                      | PARAMETER                                                 | TEST CONDITIONS                                        | MIN | TYP | MAX | UNIT  |

|----------------------|-----------------------------------------------------------|--------------------------------------------------------|-----|-----|-----|-------|

| ICLAMP_DRV_63        | Current clamping range from maximum code setting          | V <sub>VPWR</sub> >7<br>V;CURR_LIM1 =<br>CURR_LIM2= 63 | 450 | 500 | 570 | mA    |

| ISTEP_SIZE_CLAMP_DRV | Step size (change in current from value at previous step) |                                                        | 5.2 | 7.2 | 9.2 | mA    |

| f <sub>SW_LOW</sub>  | Configurable switching frequency                          | FREQ_SHIFT = 0                                         | 30  |     | 80  | kHz   |

| f <sub>SW_HIGH</sub> | Cornigurable switching frequency                          | FREQ_SHIFT = 1                                         | 180 | ,   | 480 | KI IZ |

## **6.7 Transducer Receiver Characteristics**

|                               | PARAMETER                               | TEST CONDITIONS                                                                   | MIN   | TYP | MAX  | UNIT        |

|-------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------|-------|-----|------|-------------|

| GAIN <sub>RNG_TOT_RCV</sub>   | Total receiver amplification gain range | $F_{SW} = F_{SW\_LOW}, F_{SW\_HIGH};$<br>$T_A = -40$ °C to +105°C                 | 32    |     | 90   |             |

|                               |                                         | AFE_GAIN_RNG = 0x03                                                               | 32    |     | 64   |             |

| CAINI                         | Desciver amplification gain             | AFE_GAIN_RNG = 0x02                                                               | 46    |     | 78   | dB          |

| GAIN <sub>RNG_RCV</sub>       | Receiver amplification gain             | AFE_GAIN_RNG = 0x01                                                               | 52    |     | 84   |             |

|                               |                                         | AFE_GAIN_RNG = 0x00                                                               | 58    |     | 90   |             |

| GAIN <sub>NSTEP_RCV</sub>     | Gain adjustment steps                   |                                                                                   |       | 64  |      |             |

| GAIN <sub>STEP_SIZE_RCV</sub> | Gain adjustment step size               |                                                                                   | 0.2   | 0.5 | 0.8  | dB          |

| GAIN <sub>THRM_DRFT_RCV</sub> | Gain thermal drift                      | $F_{SW} = 30 \text{ kHz}; T_A = -40^{\circ}\text{C}$<br>to +105°C; Gain = 58.5 dB | -3.5% |     | 3.5% |             |

| Z <sub>INP_RCV</sub>          | Input impedance                         | F <sub>SW</sub> < 80 kHz                                                          | 300   |     |      | kΩ          |

| N <sub>RCV</sub>              | Noise floor                             | F <sub>SW</sub> = 58 kHz; T <sub>A</sub> = 105°C; BW = 4 kHz                      |       | 7   |      | nV/sqrt(Hz) |

## 6.8 Analog to Digital Converter Characteristics

|                      | PARAMETER           | TEST CONDITIONS | MIN | TYP               | MAX               | UNIT |

|----------------------|---------------------|-----------------|-----|-------------------|-------------------|------|

| V <sub>INP_ADC</sub> | Input voltage range |                 | 0   | -                 | V <sub>AVDD</sub> | \/   |

| V <sub>REF_ADC</sub> | Voltage reference   |                 |     | V <sub>AVDD</sub> |                   | V    |

| N <sub>ADC</sub>     | Resolution          |                 |     | 12                |                   | Bits |

| t <sub>CONV</sub>    | Conversion time     |                 |     | 1                 |                   | μs   |

## **6.9 Digital Signal Processing Characteristics**

|                               | PARAMETER                         |                                | MIN | TYP | MAX | UNIT |

|-------------------------------|-----------------------------------|--------------------------------|-----|-----|-----|------|

| FREQ <sub>CENTER_BPF</sub>    | Band-pass filter center frequency | Normalized to driver frequency |     | 1   |     |      |

| BW <sub>BPF</sub>             | Band-pass filter band width       |                                | 2   |     | 8   | kHz  |

| N <sub>BPF</sub>              | Band-pass filter adjustable steps |                                |     | 4   |     |      |

| FREQ <sub>STEP_SIZE_BPF</sub> | Band-pass filter step size        |                                |     | 2   |     | kHz  |

| FREQ <sub>CUTOFF_LPF</sub>    | Low-pass filter cutoff frequency  |                                | 1   |     | 4   | kHz  |

| N <sub>LPF</sub>              | Low-pass filter adjustable steps  |                                |     | 4   |     |      |

| FREQ <sub>STEP_SIZE_LPF</sub> | Low-pass filter step size         |                                |     | 1   |     | kHz  |

## **6.10 Temperature Sensor Characteristics**

|                          | PARAMETER                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------------|--------------------------|-----------------|-----|-----|-----|------|

| T <sub>RANGE_SENSE</sub> | Temperature sensor range |                 | -40 |     | 125 | °C   |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

|                        | PARAMETER      | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT |

|------------------------|----------------|---------------------------------------------|-----|-----|-----|------|

| T <sub>ACC_SENSE</sub> | Range accuracy | VPWR=12<br>V;TEMP_GAIN = 0;<br>TEMP_OFF = 0 |     | 5   |     | °C   |

## 6.11 High-Voltage I/O Characteristics

|                     | PARAMETER                         | TEST CONDITIONS                  | MIN                        | TYP | MAX                        | UNIT |

|---------------------|-----------------------------------|----------------------------------|----------------------------|-----|----------------------------|------|

| V <sub>IH_IO</sub>  | High-voltage IO input high level  | IO pin                           | 0.6 ×<br>V <sub>VPWR</sub> |     |                            | V    |

| V <sub>IL_IO</sub>  | High-voltage IO input low level   | IO pin                           |                            |     | 0.4 ×<br>V <sub>VPWR</sub> | V    |

| V <sub>HYS_IO</sub> | High-voltage input hysteresis     | IO pin                           | 0.05 ×<br>VPWR             |     | 0.175 ×<br>VPWR            | V    |

| V <sub>OL_IO</sub>  | High-voltage IO output low level  | IO pin ; I <sub>IO</sub> = 10 mA |                            |     | 2                          | V    |

| R <sub>PU_IO</sub>  | High-voltage IO pullup resistance | IO pin                           | 4                          | 10  | 16                         | kΩ   |

| I <sub>LIM_IO</sub> | Current limit on high-voltage IO  | Short to VPWR                    | 40                         |     | 250                        | mA   |

## **6.12 Digital I/O Characteristics**

|                          | PARAMETER                                 | TEST CONDITIONS                                                                                                                    | MIN                        | TYP | MAX                        | UNIT |

|--------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|------|

| V <sub>IH_DIGIO</sub>    | Digital input high level                  | RX and SCLK pin; V <sub>IOREG</sub> =V <sub>IOREG_33</sub> /<br>V <sub>IOREG_50</sub>                                              | 0.7*V <sub>IOR</sub><br>EG |     |                            | V    |

| V <sub>IL_DIGIO</sub>    | Digital input low level                   | RX and SCLK pin; V <sub>IOREG</sub> =V <sub>IOREG_33</sub> /<br>V <sub>IOREG_50</sub>                                              |                            |     | 0.3*V <sub>IOR</sub><br>EG | V    |

| V <sub>HYS_DIGIO</sub>   | Digital input hysteresis                  | RX and SCLK pin                                                                                                                    | 100                        |     |                            | mV   |

| V <sub>OH_DIGIO</sub>    | Digital output high level                 | DECPL and TX pin; I <sub>DECPL</sub> /I <sub>TX</sub> = -2<br>mA; V <sub>IOREG</sub> =V <sub>IOREG_33</sub> /V <sub>IOREG_50</sub> | V <sub>IOREG</sub> – 0.2   |     |                            | V    |

| V <sub>OL_DIGIO</sub>    | Digital output low level                  | DECPL and TX pin; I <sub>DECPL</sub> /I <sub>TX</sub> = 2mA                                                                        |                            |     | 0.2                        | V    |

| R <sub>PU_DIGIO_RX</sub> | Digital input pull-up resistance to IOREG | RX pin                                                                                                                             | 90                         | 100 | 160                        | kΩ   |

| R <sub>PU_DIGIO_SC</sub> | Digital input pull-down resistance        | SCLK pin                                                                                                                           | 80                         | 100 | 130                        | kΩ   |

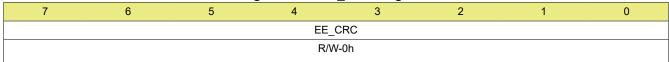

## **6.13 EEPROM Characteristics**

|                         | PARAMETER                  | TEST CONDITIONS                 | MIN | TYP | MAX  | UNIT   |

|-------------------------|----------------------------|---------------------------------|-----|-----|------|--------|

| Bytes <sub>EE</sub>     | EEPROM memory size         | Application and Device Internal |     | 64  |      | Bytes  |

| t <sub>RET_EE</sub>     | EEPROM data retention time | T <sub>A</sub> = 105°C          |     |     | 10   | Years  |

| Cycl <sub>BURN_EE</sub> | EEPROM burn cycles         |                                 |     |     | 1000 | Cycles |

| t <sub>PROG_EE</sub>    | EEPROM programming time    |                                 |     | 600 |      | ms     |

## **6.14 Timing Requirements**

|                       |                                       | MIN | NOM  | MAX  | UNIT |  |  |  |

|-----------------------|---------------------------------------|-----|------|------|------|--|--|--|

| TIME COMMA            | TIME COMMAND INTERFACE                |     |      |      |      |  |  |  |

| t <sub>BIT_TCI</sub>  | Bit period                            | 225 | 300  | 375  | μs   |  |  |  |

| t <sub>BIT0_TCI</sub> | Logical 0 bit length                  | 150 | 200  | 250  | μs   |  |  |  |

| t <sub>BIT1_TCI</sub> | Logical 1 bit length                  | 75  | 100  | 125  | μs   |  |  |  |

| t <sub>BLP1_TCI</sub> | BURST/LISTEN (Preset1) command period | 328 | 400  | 472  | μs   |  |  |  |

| t <sub>BLP2_TCI</sub> | BURST/LISTEN (Preset2) command period | 920 | 1010 | 1100 | μs   |  |  |  |

| t <sub>LP1_TCI</sub>  | LISTEN only (Preset1) command period  | 697 | 780  | 863  | μs   |  |  |  |

| t <sub>LP2_TCI</sub>  | LISTEN only (Preset2) command period  | 503 | 580  | 657  | μs   |  |  |  |

Product Folder Links: PGA460-Q1

|                        |                                        | MIN  | NOM   | MAX  | UNIT |

|------------------------|----------------------------------------|------|-------|------|------|

| t <sub>CFG_TCI</sub>   | Device configuration command period    | 1170 | 1270  | 1370 | μs   |

| t <sub>TEMP_TCI</sub>  | Temperature measurement command period | 1440 | 1550  | 1660 | μs   |

| t <sub>NOISE_TCI</sub> | Noise level measurement command period | 2070 | 2200  | 2340 | μs   |

| t <sub>DT_TCI</sub>    | Command processing dead-time           | 75   | 100   | 125  | μs   |

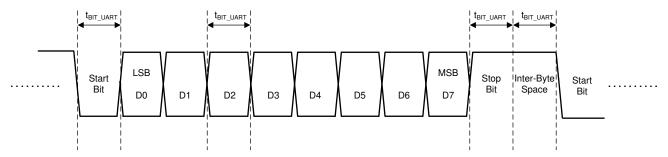

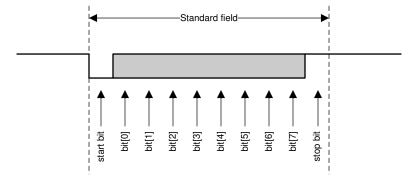

| USART ASYNO            | CHRONOUS INTERFACE                     | •    |       |      |      |

| t <sub>BIT_UART</sub>  | Logical bit length at 19.2 kbps        | 45.5 | 52.08 | 58.6 | μs   |

| t <sub>BITF_UART</sub> | Logical bit length at 115.2 kbps       | 7.6  | 8.68  | 9.76 | μs   |

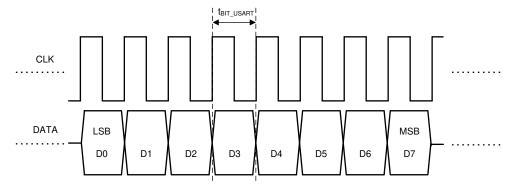

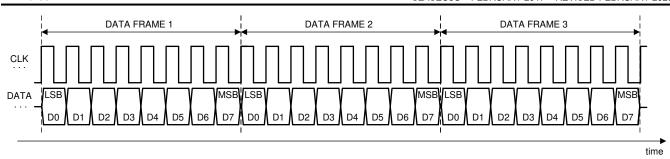

| USART SYNCH            | IRONOUS INTERFACE                      | •    |       | ,    |      |

| t <sub>BIT_USART</sub> | Logical bit length at 8 Mbps           | 55   | 125   |      | ns   |

## 6.15 Switching Characteristics

|                         | PARAMETER                                  |  | MIN  | TYP  | MAX   | UNIT |

|-------------------------|--------------------------------------------|--|------|------|-------|------|

| f <sub>CORE_CLK</sub>   | Core frequency <sup>(1)</sup>              |  | 15.5 | 16   | 16.5  | MHz  |

| ACC <sub>CORE_CLK</sub> | Core frequency accuracy <sup>(2)</sup>     |  | -4%  |      | 4%    |      |

| Baud <sub>UART</sub>    | USART asynchronous interface baud rate     |  | 2.4  | 19.2 | 131.5 | kbps |

| Baud <sub>USART</sub>   | USART interface synchronous mode baud rate |  |      |      | 8     | Mbps |

- (1) At Room Temperature (25°C)

- (2) Across Operating Temperature Range (-40°C to 105°C)

### **6.16 Typical Characteristics**

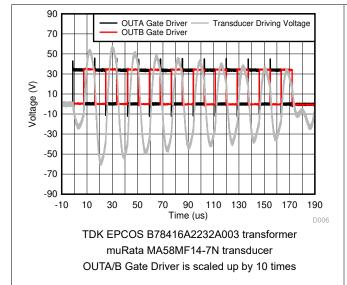

10 pulses, 400-mA current limit, 58.6-kHz driving frequency

Figure 6-1. Driver Stage and Resulting Transducer Behavior

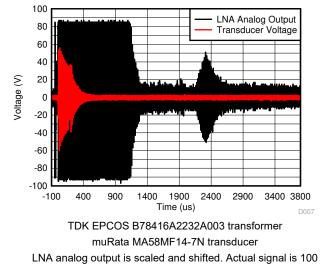

LNA analog output is scaled and shifted. Actual signal is 100 times smaller and common mode is shifted up by 0.9 V

Figure 6-2. Receiver AFE Output Post-LNA Object at 35 cm

## 7 Detailed Description

#### 7.1 Overview

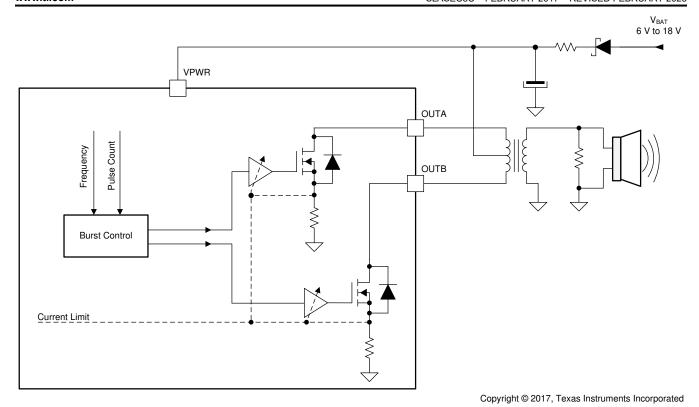

The PGA460-Q1 device is a signal-conditioning and transducer-driver device for ultrasonic sensing for object or distance sensing. The output driver consists of complimentary low-side drivers capable of driving a center-tap transformer to generate large excitation voltages across an ultrasonic transducer and as a result create the desired sound pressure level (SPL). The output driver can also be configured to be used in direct-drive mode without a transformer using external FETs. The output driver implements configurable current limit for efficient driving of the transformer and configurable bursting frequencies and burst length to be compatible with a large number of transducers.

The analog front-end (AFE) can sense the received echo from the transducer and amplify it for correct object detection. The AFE implements a low-noise amplifier followed by a time-varying gain amplifier that allows signals from objects at a variable distance to be amplified correspondingly. This implementation allows for the maximum dynamic range of the ADC to be used for both near-field and far-field objects in the same recording. An embedded temperature sensor can be used to calibrate the signal conditioner for changes in temperature. The digital signal processing path further filters the received echo and uses time-varying thresholds for accurate detection of objects. Two presets for both bursting and thresholds are available which allow faster detection cycles by saving time required to configure the device between multiple bursts. Most configuration parameters are stored in nonvolatile memory for quick power up, which reduces initialization time.

The PGA460-Q1 device provides multiple IO protocols to communicate with the controller. The device provides a time-command interface and one-wire UART on the VPWR reference IO pin. It also provides both synchronous and asynchronous USART on the TXD, RXD, and SCLK pins.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Power-Supply Block

The PGA460-Q1 device uses multiple internal regulators as supplies for the internal circuits. The analog voltage regulator (AVDD) requires an external capacitor of 100 nF. The power-supply block generates precision voltage references, current bias, and an internal clock. An additional regulator (IOREG) generates the supply voltage for the USART pins (RXD, TXD, and SCLK), DECPL pin, and TEST pin for their digital functionality. The AVDD and IOREG regulators are not intended to support any external load. The external capacitors are recommended to be placed as close as possible to the related pins (AVDD and IOREG). The PGA460-Q1 device starts to power up when a voltage is applied to the VPWR pin. The internal power-on reset (POR) is released when all regulator supplies are in regulation and the internal clock is running. During low-power mode, the IOREG regulator is powered up while the other regulators shut down to conserve power.

#### 7.3.2 Burst Generation

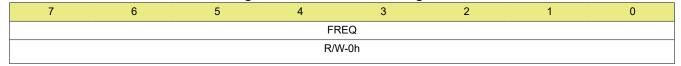

The PGA460-Q1 device has a programmable frequency for the burst and number of pulse by configuring the FREQ and P1\_PULSE/P2\_PULSE registers.

Use Equation 1 to calculate the frequency of burst for a range of 30 kHz to 80 kHz (FREQ SHIFT bit set to 0).

$$f_{(DRV)} = 0.2 \text{ kHz} \times f + 30 \text{ kHz}$$

(1)

where

• f is the frequency which can be from 0 to 200 as defined in the FREQUENCY register.

The actual driving frequency of the output stage is derived from the core clock frequency using Equation 1 and Equation 2

$$n = \frac{f_{(CORE\_CLK)}}{f_{(DRV)}}$$

(2)

where

- n is the ratio by which the main oscillator  $f_{(CORE\ CLK)}$  is divided.

The PULSE\_P1 and PULSE\_P2 registers can range from 0 to 31. When set to a value of M that is greater than 0, the M pulse pairs are generated on the OUTA and OUTB outputs.

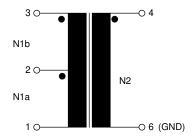

#### 7.3.2.1 Using Center-Tap Transformer

The PGA460-Q1 device provides efficient burst generation by exciting the primary side of a center-tap transformer connected on the OUTA and OUTB pins through the complementary low-side FETs operating in a current limiting mode. The frequency of the burst is from 30 kHz to 80 kHz with the current limit from 50 mA to 500 mA. The frequency of the burst, the current limit for transformer primary current, and the number of burst pulses can be controlled by using the FREQUENCY, CURR\_LIM\_P1, CURR\_LIM\_P12, PULSE\_P1, and PULSE\_P2 parameters, respectively.

Figure 7-1 shows the functional block diagram for echo generation.

Figure 7-1. Echo Generation Block Diagram

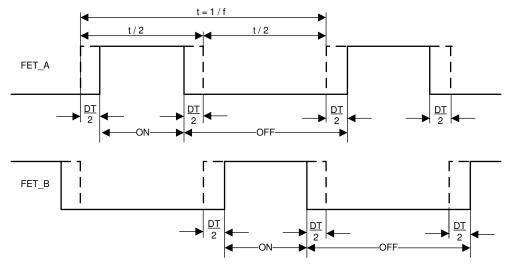

#### 7.3.2.2 Direct Drive

The complementary low-side drivers can be used in conjunction with an external PMOS FET to provide single-ended direct excitation to the transducer. In this configuration, the internal FETs can be used in a RDSON mode by disabling current limiting feature by setting the DIS\_CL bit in the CURR\_LIM\_P1 register.

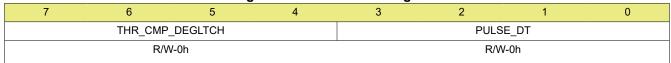

An additional dead-time feature can be used in this mode to eliminate the shoot-through currents between the external PMOS FET and internal low-side FETs by configuring the PULSE\_DT bit. The burst cycle period of the low-side FETs remains unchanged; however, the deactivation time is reduced by the dead-time programmed value. Figure 7-2 shows this case.

Figure 7-2. Echo Generation Dead-Time Adjustment

#### 7.3.2.3 Other Configurations

When any of the P1\_PULSE or P2\_PULSE bits are set to 0, only the OUTA output generates a pulse, while the OUTB output remains in the high-impedance (High-Z) state during this period. This configuration is used to reduce the output voltage when only short distances are required to be detected.

#### Note

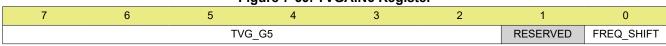

- For higher frequency support, the device has an option to shift up the burst frequency range

which occurs by setting the FREQ\_SHIFT bit in the CURR\_LIM\_P1 register. When this bit is

set, the burst frequency is 6 times higher of the burst frequency selected by the FREQUENCY

register. With this bit set, the range of burst frequencies is from 180 kHz to 480 kHz with a step of

approximately 1.2 kHz.

- The maximum dead time setting should be less than or equal to t / 8 where t is burst period.

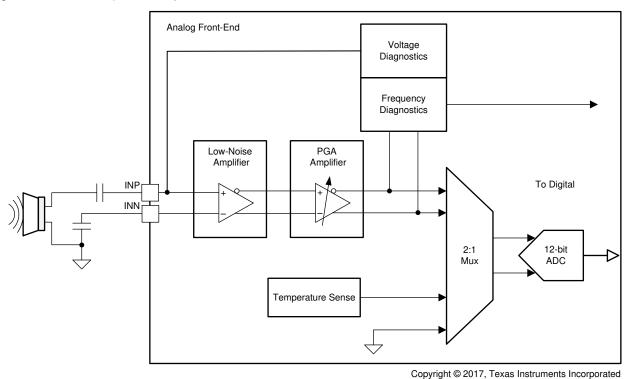

#### 7.3.3 Analog Front-End

The analog front-end (AFE) in the PGA460-Q1 device, shown in Figure 7-3, receives the reflected echo from the object, amplifies it, and feeds it into a digital signal processing (DSP) data path for echo detection. Because the received echo signal can vary amplitude (in millivolts for near objects and in microvolts for far objects), the first AFE stage is a very low-noise balanced amplifier with a predetermined fixed gain followed by a variable gain-stage amplifier with configurable gain from 32 dB to 90 dB. The amplified echo signal is converted into a digital signal by a 12-bit analog-to-digital converter (ADC) and fed to a DSP processing block for further evaluation and time-of-flight measurement.

The PGA460-Q1 AFE implements system diagnostics for sensing element (transducer) monitoring during the burst and decay stage of the echo recording process in a way of measuring the maximum achieved voltage at the transducer node and the frequency of oscillation at the transducer node. For more information on these diagnostics, see the *System Diagnostics* section.

Figure 7-3. Analog Front-End

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

The variable gain amplifier in the AFE implements a time-varying gain feature which allows the user to set different static gains and also specify a gain profile for the echo listening process (echo record time). This feature allows for a uniform amplification of echo signals from objects at different distances without saturating the ADC. As an example, for closer objects, gain can be programmed lower initially in time and then increased during the recording time to detect farther objects which have a very small echo signal. This feature helps in attaining sufficient SNR after ADC conversion for all distances for accurate time of flight measurement.

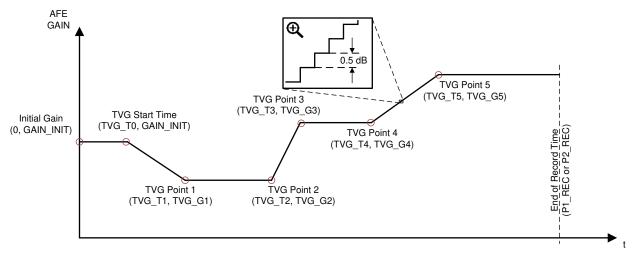

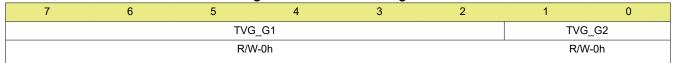

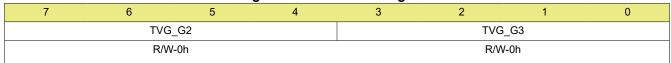

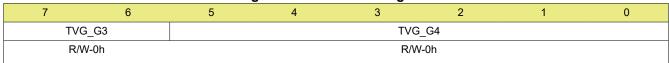

The time-varying gain parameters are stored in the EEPROM memory and characterized by:

- The initial fixed-gain parameter, GAIN INIT.

- A time-varying gain start-time value stored in the TVGAIN0 register.

- An array of 5 gain-varying cross points placed in the TVGAIN0 to TVGAIN6 registers.

Figure 7-4 shows an example plot of the time-varying gain.

Figure 7-4. Time-Varying Gain Assignment Example

The time value, TVG start time, is expressed in terms of absolute time, and all following TVG point times (TVG\_Tx parameters) are expressed as a delta time between the current and previous point. All gain values are expressed in an absolute gain value in dB and are unrelated from each other. The final gain setting of TVG Point 5 (TVG\_G5) will be kept constant until the end of the echo record time. The time-varying gain assignment is the same for both presets. A linear interpolation scheme is used to calculate gain between two TVG points. The AFE gain resolution is 0.5 dB typical.

#### Note

The time-varying gain changes during the recording are applied only on the record cycle that follows. If the TVGAIN[0:6] registers programmed to 0x00, the time-varying gain function of the PGA460-Q1 device is disabled and a fixed gain defined by the INIT\_GAIN register is applied. In this case, changing the INIT\_GAIN register changes the gain of AFE during the recording.

The offset on the time-varying gain is controlled through the two AFE\_GAIN\_RNG bits in DECPL\_TEMP register. For each of the four settings as defined in the *Register Maps* section, the gain can be varied from 0 to 32 dB added on top of the offset.

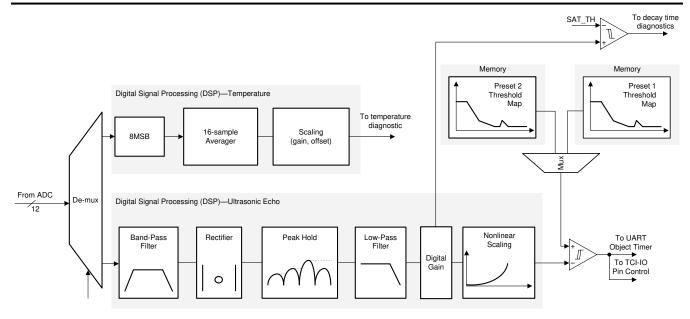

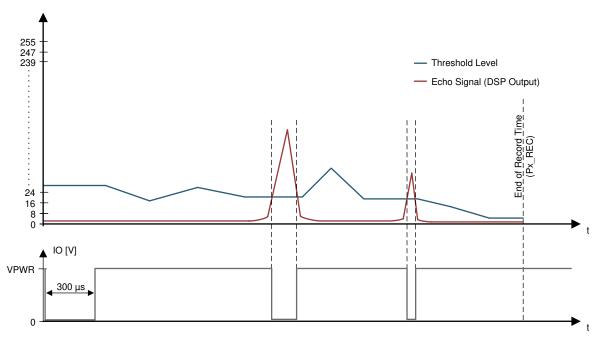

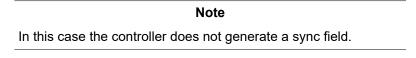

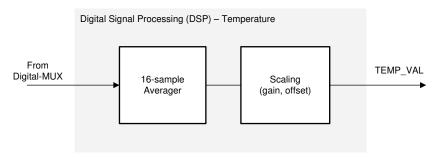

#### 7.3.4 Digital Signal Processing

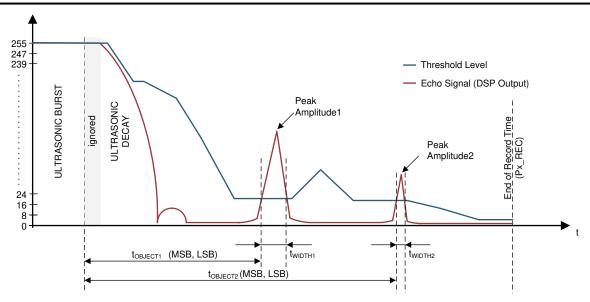

The DSP block of the PGA460-Q1 device processes the digital data from the ADC to extract the peak profile of the echo after which the output of the DSP is compared against the programmed threshold to measure the time of flight for object distance calculation.

Figure 7-5 shows the data path of the DSP. Also, the output of the comparator can be deglitched by the THR CMP DEGLTCH[7:4] bits in the DEADTIME register.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

Figure 7-5. DSP Data-Path

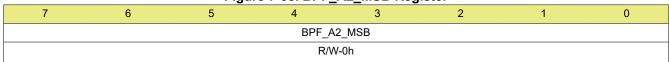

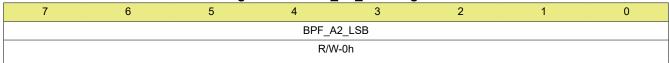

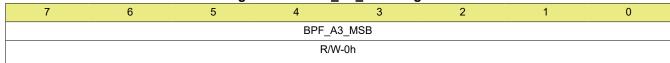

#### 7.3.4.1 Ultrasonic Echo—Band-Pass Filter

The ultrasonic echo signal is an amplitude-modulated signal with an underlying carrier frequency equal to the drive frequency of the ultrasonic transducer. The DSP band-pass filter block allows the frequencies outside of the observed frequency band to be filtered out and therefore reducing the amount of noise influencing the ultrasonic echo signal.

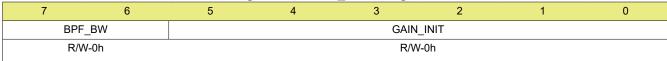

The center frequency of the filter is automatically adjusted based on the driving frequency set by the FREQ bit while the bandwidth of the filter can be adjusted from 2 kHz to 8 kHz in steps of 2 kHz by setting the BPF\_BW bit in the INIT GAIN EEPROM register.

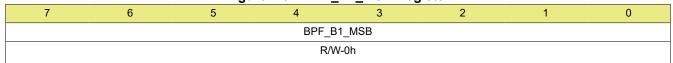

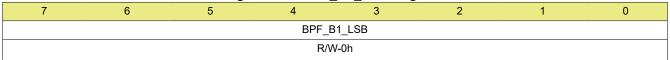

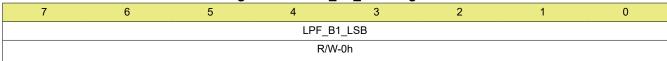

The band-pass filter is a second-order Butterworth IIR type filter. On power up, the PGA460-Q1 device calculates the coefficients and places them in the BPF\_A2\_xSB, BPF\_A3\_xSB, and BPF\_B1\_xSB registers. These registers can be overwritten by the user to reconfigure the filter. However, if the FREQ or BPF\_BW bit is changed, the coefficient calculation sequence is rerun and the device rewrites these registers. In case the FREQ\_SHIFT bit is set to 1 (80- to 480-kHz driving frequency range), the band-pass filter coefficients are not calculated automatically by the PGA460-Q1 device. In this case the MCU is required to write these values through the UART or USART interface.

#### 7.3.4.2 Ultrasonic Echo-Rectifier, Peak Hold, Low-Pass Filter, and Data Selection

The rectifier, peak extractor, and low-pass filter DSP blocks demodulate the echo signal while outputting a base-band representation to be compared against the programmed thresholds. These blocks are defined as:

| Rectifier | This block outputs the absolute value of the input signal since the input signal can be positive |

|-----------|--------------------------------------------------------------------------------------------------|

|           |                                                                                                  |

and negative in amplitude.

Peak hold This block holds the peak value of the rectified signal for a specific amount of time required for

the low-pass filter to detect the peak amplitude of the signal.

Low-pass This block removes any noise artifacts from the echo signal. The LPF is realized as a first-order IIR type filter. The user can set the cutoff frequency by setting the LPF\_CO bit in

CURR LIM P2 register from 1 kHz to 4 kHz with a step of 1 kHz.

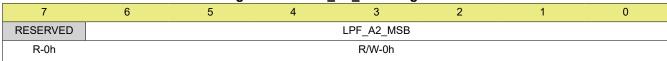

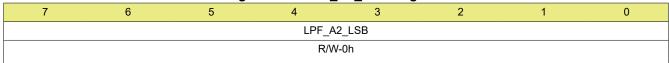

On power up the PGA460-Q1 device calculates the values of the filter coefficients and places them in the LPF\_A2\_xSB and LPF\_B1\_xSB registers, respectively. The user can overwrite the values in these registers and reconfigure the filter. In this case, the PGA460-Q1 device does not take any action. However, if the LPF\_CO bit is changed, the coefficient calculation sequence must be rerun and the device repopulates these registers.

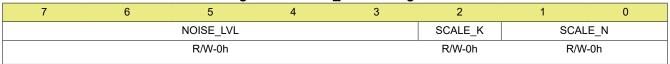

#### 7.3.4.3 Ultrasonic Echo—Nonlinear Scaling

The nonlinear scaling block in the DSP data path provides exponential scaling (digital nonlinear amplification) for the echo signal to achieve a higher SNR. This feature is useful for detecting long distance object where the amplitude of the echo signal is very attenuated and close to the noise floor.

The nonlinear scaling block performs the following algorithm:

#### where

- t is the current record time.

- Time\_Offset is set by the SCALE\_N parameter and is used to select one of the time points corresponding

to threshold points, TH9, TH10, TH11, or TH12 defined in the *Ultrasonic Echo—Threshold Data Assignment*section.

- Scale Exponent is the nonlinear exponent (1.5 or 2) and defined by the SCALE K bit.

- · Noise\_Level is the user-set noise level between 0 and 31 in 1 LSB step and defined by the NOISE\_LVL bit.

The SCALE\_N, SCALE\_K, and NOISE\_LVL bits are EEPROM parameters in the DSP\_SCALE register.

#### Note

The nonlinear scaling block can be applied to Preset1 and Preset2.

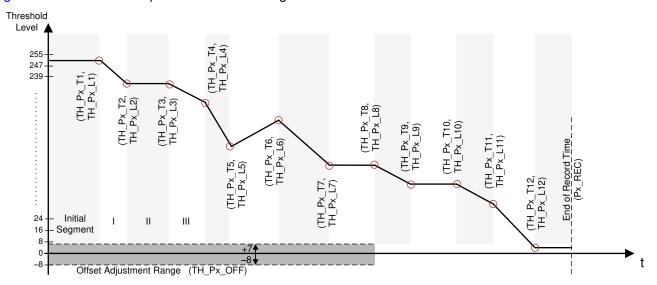

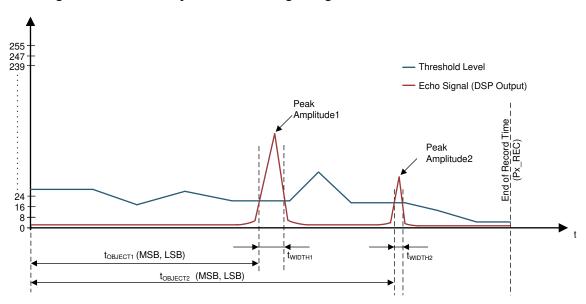

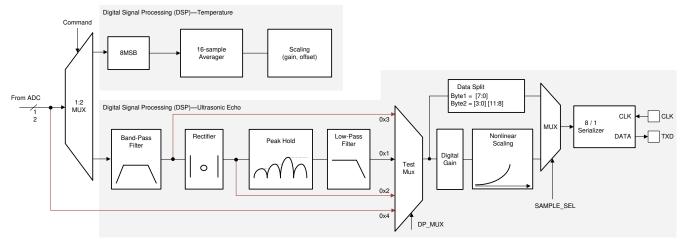

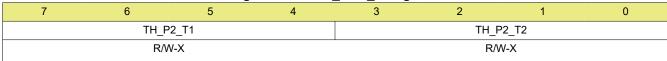

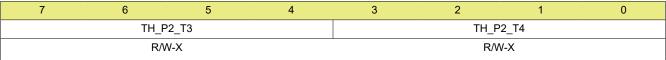

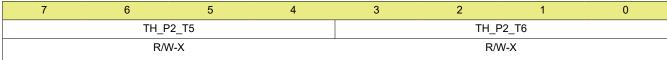

#### 7.3.4.4 Ultrasonic Echo—Threshold Data Assignment

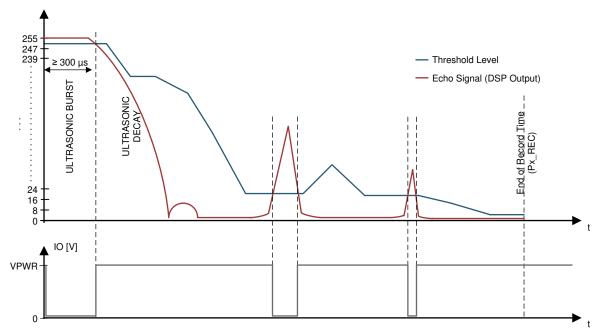

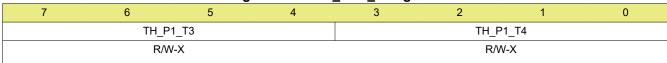

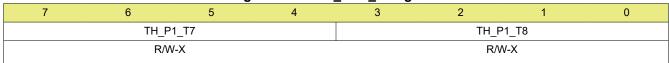

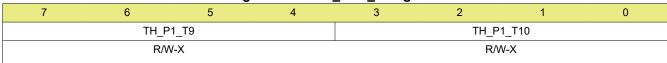

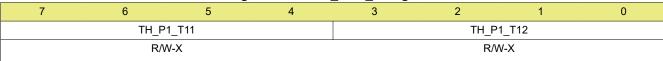

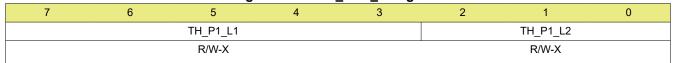

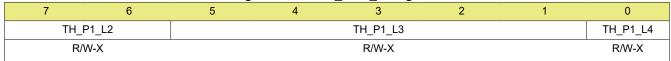

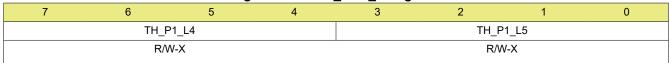

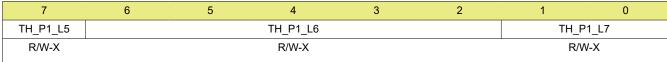

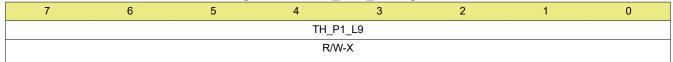

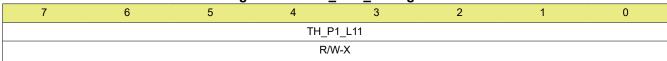

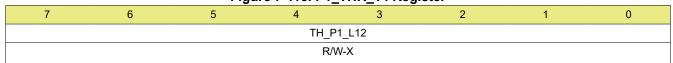

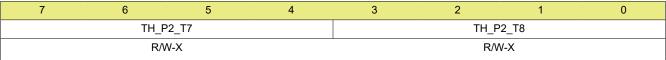

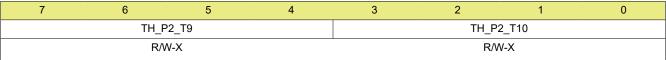

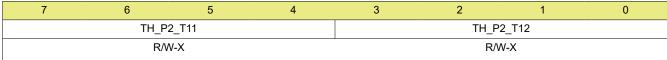

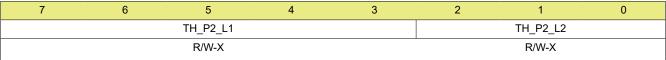

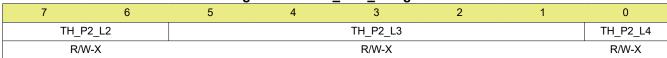

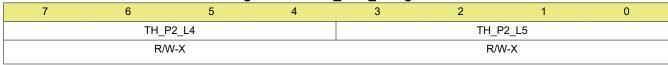

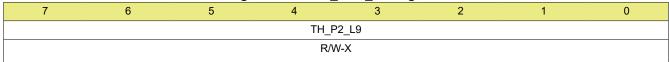

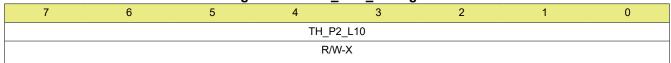

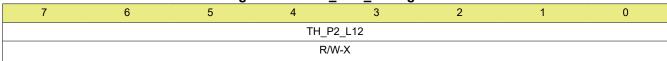

The PGA460-Q1 threshold assignments are organized in two presets: Preset1 and Preset2. Both of these presets have an independent memory map for threshold segment allocation. The PGA460-Q1 device supports up to 12 threshold segments for each preset defined by the threshold segment points (TSP) in the P1\_THR\_[0:15] registers for Preset1 and P2\_THR\_[0:15] registers for Preset2.

Figure 7-6 shows an example of a threshold assignment.

Figure 7-6. Threshold Assignment Example

As shown in Figure 7-6, each TSP is described in the (time, level) format while Px is the preset number (P1 for Preset1, P2 for Preset2). Additionally, only the initial segment time parameter (TH\_Px\_T1) value is expressed

in terms of absolute time, while all following TSP times (TH\_Px\_Tx parameters) are expressed as a delta time between the absolute time value of the previous TSP and the absolute time value of the current TSP. The level values of each TSP (TH\_Px\_Lx parameters) are all expressed in an absolute LSB-level value and are unrelated from each other. The TSP level threshold value at any given time moment is determined by the PGA460-Q1 device as a linear interpolation function between the two neighboring threshold segment points

As shown in Figure 7-6, the initial segment has a constant threshold value determined by the TH\_Px\_L1 parameter until reaching the start of the first segment and also the 12th segment will have a constant threshold value determined by the TH\_Px\_L12 parameter until reaching the end of record time defined by the Px\_REC parameter.

The TH\_Px\_L1 through TH\_Px\_L8 threshold parameters are 5-bits wide and the TH\_Px\_L9 through TH\_Px\_L12 parameters are 8-bits wide. These sizes help save memory space and at the same time allow higher resolution for long-range detection of weak echo signals in presence of noise while keeping the range constant across all TSPs. Because the TH\_Px\_L1 through TH\_Px\_L8 resolution is an 8 LSB, a threshold offset is defined to allow finer adjustment of the threshold map for short-range detection.

#### Note

- All calculated values of TSP after adding offset, if negative, are clamped to 0 before linear interpolation which causes the slope of threshold curve to deviate from expected value.

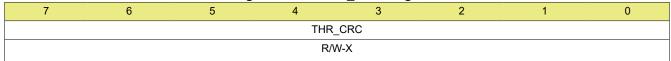

- Both Preset1 and Preset2 threshold map parameters are protected by a CRC calculation algorithm (Equation 6).

- At power up or wakeup from low power mode, all threshold registers (Px\_THR\_XX) and threshold CRC register (THR\_CRC) are not initialized to the default value which causes a CRC error and sets THR\_CRC\_ERR bit to 1. This occurrence indicates to the MCU that the configuration is not loaded properly. Writing to threshold registers reruns CRC calculation and updates the error bit.

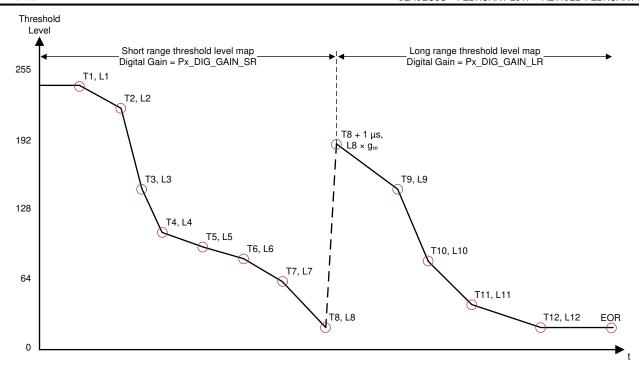

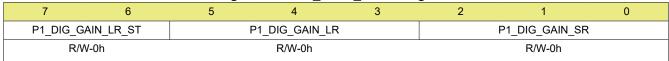

#### 7.3.4.5 Digital Gain

A digital gain feature after the low-pass filtering is implemented to improve the SNR of the received echo without lowering the threshold values. Because this gain is applied after the band-pass and low-pass filtering, the digital gain does not amplify the out of band noise. This gain feature can help in suppressing false detection such as ground reflection and detecting farther objects with more accuracy.

Two sets of digital gain ranges are available: short range (SR) and long range (LR). The SR and LR gain levels are set using the Px\_DIG\_GAIN\_SR and Px\_DIG\_GAIN\_LR parameters, respectively, in the Px\_GAIN\_CTRL register independently for Preset1 and Preset2. The LR gain is applied starting from the threshold level point set by Px\_DIG\_GAIN\_LR\_ST parameter to the end of the record period. The SR gain is applied from time zero to the start of the selected LR-threshold level point.

To prevent false detection of an echo at the point in time where the digital gain is applied, the defined thresholds are also changed (see Figure 7-7). Here, the LR gain is applied starting from the threshold level point 9. If the LR gain is different than the SR gain at threshold level point 8, the threshold level 8 is multiplied by the ratio between the LR gain and SR gain (DIG\_GAIN\_LR/DIG\_GAIN\_SR) 1 µs after the end of the SR threshold level 9 point. Although this creates a discontinuity in the threshold level, the object detection is not affected (a false threshold crossing is prevented) because the echo signal is also scaled by the same gain ratio. After this point, the threshold level is changed to the next set threshold level (point 9 in example below) using a linear interpolation scheme. The threshold levels should be adjusted by taking the digital gain and the ratio between the LR and SR gains into account.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Figure 7-7. Example of DIG\_GAIN\_LR\_ST = [00] TH9

#### 7.3.5 System Diagnostics

The system diagnostics in the PGA460-Q1 device help characterize the transducer element during the burst itself and determine the status of the overall system. By using the provided information the system should be able to detect transducer failure, driver-circuit failure (transformer failure if used), environmental effects on the system (such as ice, dirt, snow), objects compromising the transducer operation (such as pressure applied to the transducer), and others.

Three implemented system diagnostics are available in the PGA460-Q1 device that provide information which can be used in detecting system flaws. These diagnostics are described as follows:

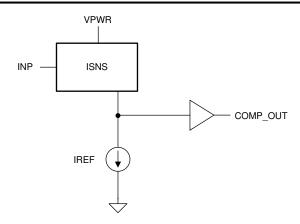

Voltage diagnostic measurement

The voltage diagnostic feature is obtained by monitoring the current flowing through the INP pin only when a BURST/LISTEN run command is executed. The transducer excitation voltage at the particular burst frequency results in a current at INP pin that is compared to a reference current with a current comparator as shown in Figure 7-8. If the excitation current exceeds the threshold level set using the FVOLT\_ERR\_TH in FVOLT\_DEC register, the current comparator output goes high which implies a normal burst with the desired level of excitation voltage. The measurement starts approximately 50 µs after the burst stage is started and ends at the end of the burst stage. The result of this diagnostic measurement is reported in the status frames of the IO time-command or the UART interface as described in the *Interface Description* section.

Figure 7-8. Block Diagram for Voltage Diagnostic

$$V_{(diag)} \cong 3.25 E^{-03} \times FVOLT\_ERR\_TH[2:0] \times \left(R_{(INP)} + \frac{1}{6.28 \times f_{(burst)} \times C_{(INP)}}\right) \tag{4}$$

#### where

- FVOLT\_ERR\_TH[2:0] corresponds to 1 for 000b to 8 for 111b.

- f<sub>(burst)</sub> is the burst frequency in kilohertz.

- $\dot{C}_{(INP)}$  is the input capacitance on the INP pin.

- R<sub>(INP)</sub> is an optional resistor (see Figure 8-1) used for EMI and ESD robustness.

#### Note

Prior to bursting, the comparator output is expected to be low. In the event that the output is stuck high, the condition is detected and the diagnostic fail flag is set

# Transducer frequency measurement

During the decay stage of the record interval a frequency measurement on the transducer node is performed to validate the performance and proper tuning of the transformer and transducer matching.

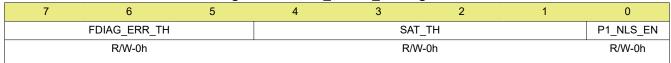

To measure the transducer frequency, a start parameter, FDIAG\_START, and a window length parameter, FDIAG\_LEN, are defined in EEPROM memory. The start parameter, FDIAG\_START, defines the time when the frequency measurement starts relative to the end of the burst time. The diagnostic window length parameter, FDIAG\_LEN, sets the time width of the diagnostic window in terms of signal periods captured. A brief example of parameter configuration can be explained:

- 1. Assume FDIAG\_START = 2 and FDIAG\_LEN = 1. Referring to the *Register Maps* section, the start time of these EEPROM parameters is determined to be 200  $\mu$ s after the burst is completed and window length of 3 signal periods. Assuming an operating frequency of 58 kHz, the signal period is 17.24  $\mu$ s and therefore the diagnostic ends at 200  $\mu$ s + 3 × 17.24  $\mu$ s = 251.72  $\mu$ s after the burst is complete.

- 2. The frequency information captured in the measurement window is averaged and expressed as a 500-ns time based counter value. The signal frequency can be calculated using Equation 5.

$$f = 1 / (FDIAG_VAL \times 500e_{-09})$$

(5)

#### where

FDIAG VAL is a value that can be extracted using any of the device interfaces.

3. If the specified number of objects are detected before a frequency diagnostic measurement completes, no frequency measurement results are saved. This can be managed by setting the previously defined diagnostic parameters and threshold settings for near-object detection.

An additional frequency error feature is implemented in the PGA460-Q1 device to signify that the measured transducer frequency is outside of the limits set by the FDIAG\_ERR\_TH threshold parameter. The result of this feature is reported in the status frames of the IO time-command or the UART interface. For more information on reporting the transducer frequency error, see the *Interface Description* section.

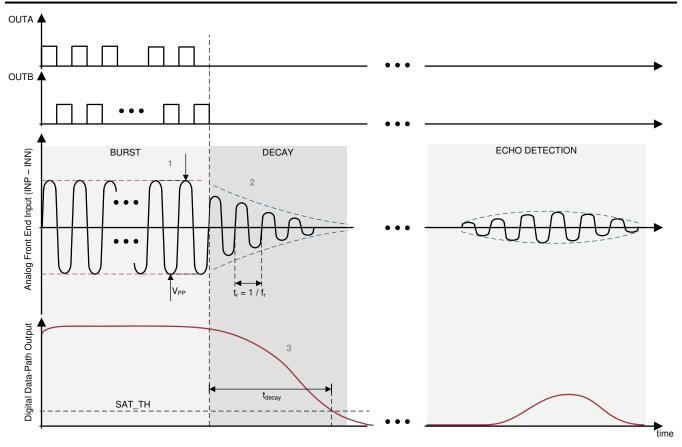

## Decay-period time capture

During the decay stage of the record interval a transducer decay time measurement is performed to verify correct operation of the transducer. This diagnostic in combination with the transducer frequency measurement are commonly used in ultrasonic systems to detect external blockage of the ultrasonic transducer.

The decay period time is measured at the output of the digital data path. The measurement starts at the same time when the burst stage is completed and the decay period is measured as long as the echo level is higher than a saturation threshold level defined in the EEPROM by the SAT\_TH parameter. The provided result can be extracted by using any of the PGA460-Q1 interfaces, while the value is expressed in 16-µs time increments. If the decay time measured greater than 4 ms, the value extracted will read 0xFF.

## Noise level measurement

An additional system diagnostic implemented in the PGA460-Q1 device is the noise-level measurement diagnostic. The purpose of this function is to evaluate the surrounding noise generated by other ultrasonic systems nearby to determine disturbances and also evaluate the noise floor level when far distance objects are being detected.

During the noise-level measurement, the PGA460-Q1 device executes the LISTEN ONLY (Preset2) command (see the *Interface Description* section for details of the command) where no burst is performed but only a record interval is started and lasts 8.192 ms. During this record interval, the data collected at the output of the digital data path is averaged into two groups each containing 4096 samples. The final noise level is measured by performing the noise-level measurement function is the higher averaged value of the two groups. This value is reported as the final noise-level measurement.

#### Note

The nonlinear scaling block is always disabled (scale factor EEPROM by setting the SCALE\_K bit 0 and the NOISE\_LVL bit to 0) during the noise-level measurement process.

Figure 7-9 shows the system diagnostics implemented in the PGA460-Q1 device as a full object-detection record cycle example. The numbers 1, 2, and 3 in Figure 7-9 show voltage diagnostic, transducer frequency, and decay-period measurement, respectively.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

Figure 7-9. Systems Diagnostics Example

#### 7.3.5.1 Device Internal Diagnostics

The PGA460-Q1 device also offers Internal diagnostics against overvoltage (OV), undervoltage (UV), overcurrent (OC), and thermal shutdown.

The OV, UV, and thermal shutdown conditions are reported through the status bits in the DEV\_STAT1 register. The OC protection is implemented on the device integrated regulators; however, the effect of this protection is not reported. For proper operation and to avoid false triggering, all electrical diagnostics are passed through a 25-µs deglitch while the thermal shutdown diagnostic is passed through a 50-µs deglitch before being reported.

The OV and UV protection thresholds for the internal regulators are listed in the *Specifications* section. When a fault is detected, the corresponding status bit is set and it is cleared upon interface read (clear-on-read type). The input device supply on the VPWR pin defines a fixed UV-threshold level and adjustable OV-threshold level (VPWR\_OV\_TH) that keeps the device active while disabling the output driver. This feature allows control of power dissipation at high voltage inputs without damaging the driver. When a VPWR\_UV flag is detected, any presently running TCI command finish and no new TCI commands are executed until the undervoltage condition is removed. This feature is not applicable to USART communication irrespective of the pins (RXD, TXD, or IO)

The thermal shutdown protection diagnostic monitors the temperature of the FETs of the low-side driver. In case of a thermal shutdown event, the PGA460-Q1 device disables the output drivers and re-enables them when the thermal shutdown condition is removed. After thermal shutdown recovery, the thermal shutdown status bit is set to notify the user of the action taken.

#### Note

If the voltage on the VPWR pin is less than 5 V, the performance of the device is not ensured as the digital core might reset. Any settings stored in the volatile memory section of the register map will be cleared.

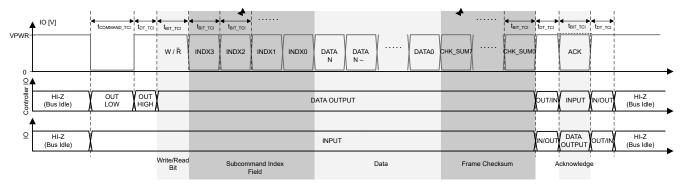

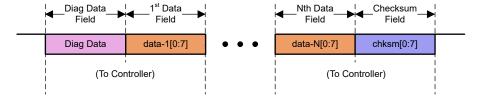

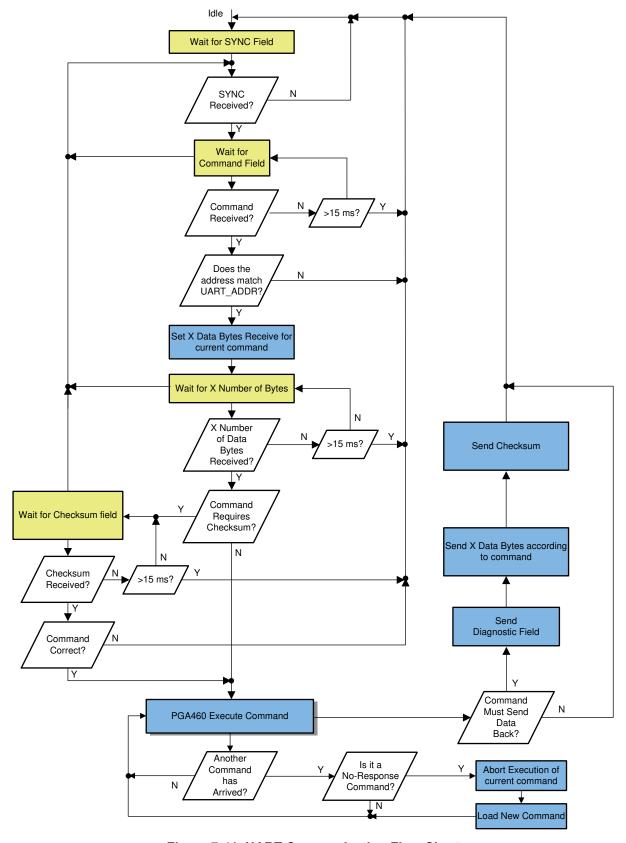

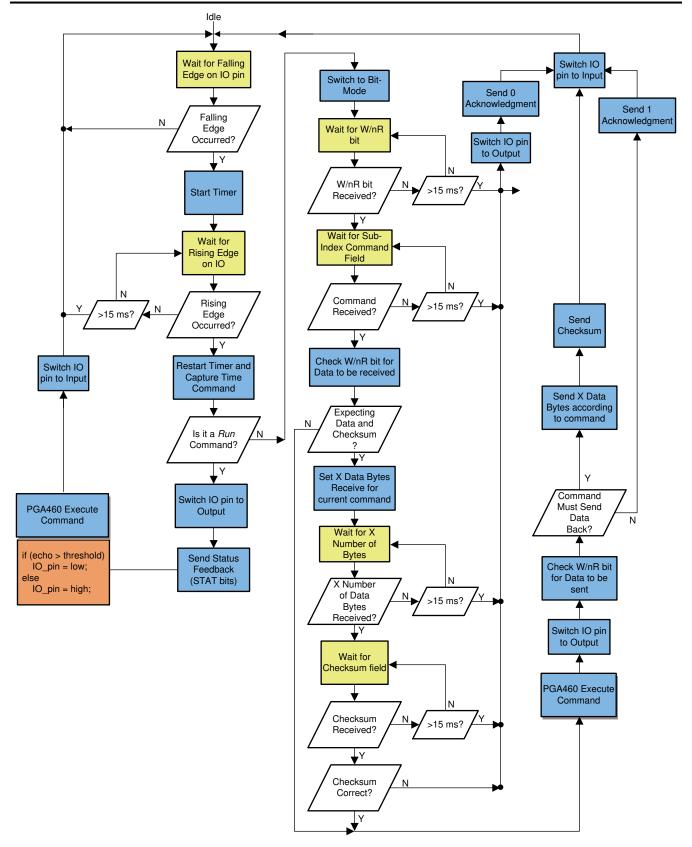

#### 7.3.6 Interface Description

The PGA460-Q1 device is equipped with two communication interfaces, each with a designated pin. The time-command interface is connected to the IO pin which is an open-drain output structure with an internal  $10\text{-k}\Omega$  pullup resistor capable of communicating at battery level voltage. The asynchronous UART interface can communicate on the IO pin and is also connected to the RXD and TXD pins. A third Interface option is to use the synchronous USART interface which is available only at the RXD and TXD pins. This communication uses SCLK pin for a serial clock input and is the fastest data-rate mode. USART communication on RXD and TXD pins is available at a 3.3-V or 5-V CMOS level depending on the configured IOREG voltage as described in the *TEST Pin Functionality* section.

#### Note

Because the system is unlikely to simultaneously use both the time-command interface and the UART interface, the PGA460-Q1 device can disable the IO pin transceiver to preserve power. To do so, the IO\_IF\_SEL bit must be 0, and the IO\_DIS bit must be 1 which immediately disables the IO pin transceiver upon which communication is only possible through the RXD and TXD pins. Setting the IO\_DIS bit back to 0 does not re-enable the IO interface. If the IO\_DIS bit was set unintentionally, the device can recover the IO interface (reset the IO\_DIS bit to 0) upon power-cycle; however, when the value of this bit is programmed in the EEPROM, the PGA460-Q1 device always follows the EEPROM-programmed value on power up.

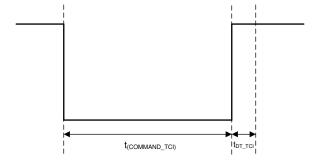

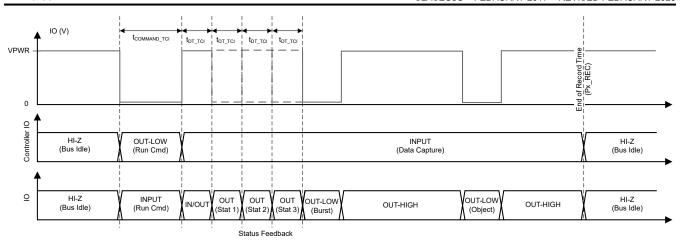

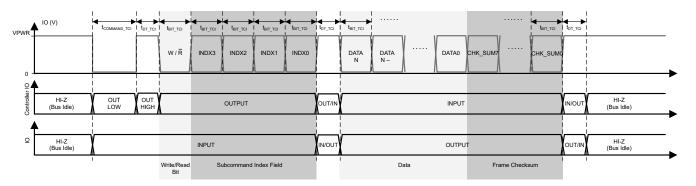

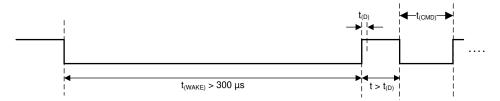

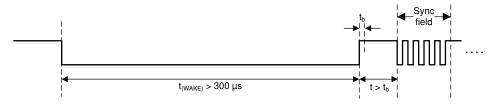

#### 7.3.6.1 Time-Command Interface

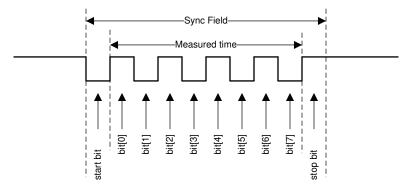

The time-command interface is the communication interface connected on the IO pin. The default state for the IO pin when the interface is idle is HIGH (pulled up to VPWR). The pin communication is bi-directional, where upon receiving a command, the PGA460-Q1 device is actively driving the IO pin and providing a response by changing the state of the IO pin. If the time-command interface remains stuck while transmitting a command or data for a particular command that is either LOW or HIGH for more than 15 ms, then the PGA460-Q1 communication resets and is expected to receive a new command transmission from the controller.

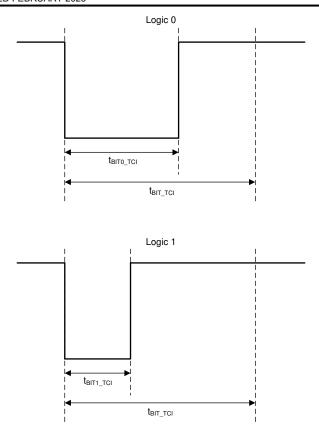

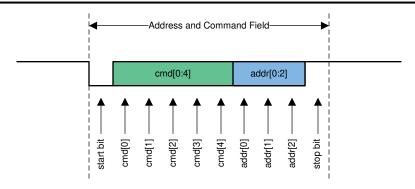

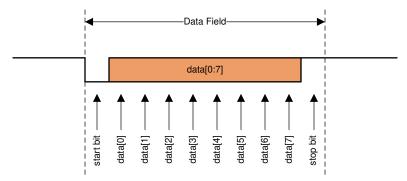

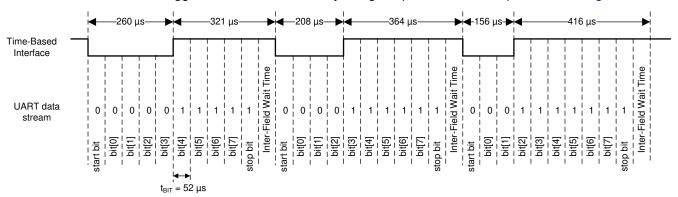

The time-command interface is specified by five time commands, where four are classified as run commands and one CONFIGURATION/STATUS command. Logic 0 is transmitted by pulling the IO pin low for a time duration of  $t_{BIT0\_TCI}$  and logic 1 is transmitted by pulling the IO pin low for time duration of  $t_{BIT1\_TCI}$  as defined in the *Specifications* section. Figure 7-10 and Figure 7-11 receptively show the general timing diagram for device time commands and for logic bit timing. The  $t_{(DT\_TCI)}$  dead-time is defined for the PGA460-Q1 device to process the received command and change the IO pin state from input to output.

Figure 7-10. Time-Command Interface Command Timing

Figure 7-11. Time-Command Interface Bit Timing

#### 7.3.6.1.1 RUN Commands

The run commands are used for device run-time operation and are most commonly used during the normal operation cycle of the PGA460-Q1 device. These device commands are specified by pulling the IO pull low for a specified period of time as defined in the *Specifications* section. The following are classified as run commands:

## Burst/Listen (Preset1)

The device sends an ultrasonic burst using the P1\_PULSE number of pulses while using the CURR\_LIM1 current-limit setting and runs an object-detection record interval defined by the value of the P1\_REC time length. During the process of object detection, the P1\_THR\_xx threshold map is used for signal comparison. The nonlinear scaling DSP function is available for use with this command.

## Burst/Listen (Preset2)

The device sends an ultrasonic burst using the P2\_PULSE number of pulses while using the CURR\_LIM2 current-limit setting and runs an object-detection record interval defined by the value of the P2\_REC time length. During the process of object detection, the P2\_THR\_xx threshold map is used for signal comparison. The nonlinear scaling DSP function is available for use with this command.

## Listen Only (Preset1)

The device does not send an ultrasonic burst, however, and only runs an object-detection record interval defined by the value of the P1\_REC time length. During the process of object detection, the P1\_THR\_xx threshold map is used for signal comparison. The nonlinear scaling DSP function is available for use with this command.

## Listen Only (Preset2)

The device does not send an ultrasonic burst, however, but only runs an object-detection record interval defined by the value of the P2\_REC time length. During the process of object detection, the P2\_THR\_xx threshold map is used for signal comparison. The nonlinear scaling DSP function is available for use with this command.

Figure 7-12 shows the process of the communication of the IO pin run command.

Figure 7-12. Time-Command Interface RUN Command Execution

The status field of the PGA460-Q1 device is embedded in the run command and provided back to the controller by extending the dead-time on the IO bus. The dead-time can be further extended for up to  $3 \times t_{(DT\_TCI)}$  which signifies three status bits, STAT[1:3]. Table 7-1 shows the assigned diagnostic and a priority of each status bit.

|                     | Table 7-1. Time-Command interface Status bits description |                                          |  |  |  |  |  |

|---------------------|-----------------------------------------------------------|------------------------------------------|--|--|--|--|--|

| STATUS BIT PRIORITY |                                                           | DESCRIPTION                              |  |  |  |  |  |

| STAT 1              | 1, low                                                    | Threshold settings uninitialized error   |  |  |  |  |  |

| STAT 2              | 2                                                         | Frequency diagnostics error              |  |  |  |  |  |

| SIAI 2              | 2                                                         | Voltage diagnostic error                 |  |  |  |  |  |

| STAT 3              | 3, high                                                   | Power-up auto EEPROM CRC error           |  |  |  |  |  |

| SIAIS               | S, High                                                   | User triggered EEPROM download CRC error |  |  |  |  |  |

Table 7-1. Time-Command Interface Status Bits Description

As listed in Table 7-1, the STAT3 bit has the highest priority. When a STAT3 error condition is present, then the dead-time is further extended by 3 ×  $t_{(DT\_TCI)}$ . In this case, if any STAT2 or STAT1 error conditions are also present, these conditions are overruled by the higher priority of STAT3 error conditions. In a similar way, a STAT1 condition is overruled by a STAT2 error condition in which case the dead-time is further extended by 2 ×  $t_{(DT\_TCI)}$ . When all STAT3 and STAT2 error conditions have cleared, a STAT1 condition further extends the dead-time by an additional  $t_{(DT\_TCI)}$ .

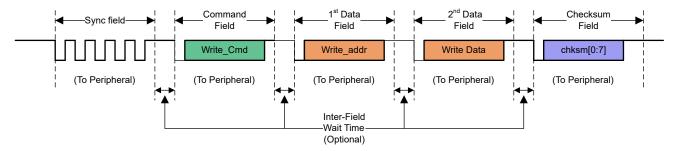

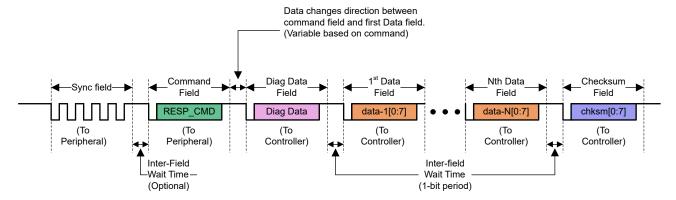

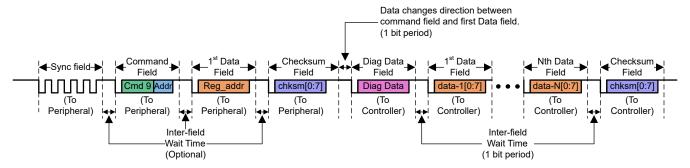

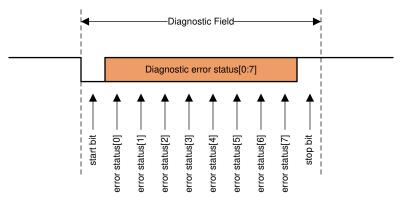

The functions of the status bits can be explained as follows: