# LMG2640 Integrated 650V GaN Half Bridge

#### 1 Features

- 650V GaN power-FET half bridge

- $105m\Omega$  low-side and high-side GaN FETs

- Integrated gate drivers with low propagation delays

- Current-sense emulation with high-bandwidth and high accuracy

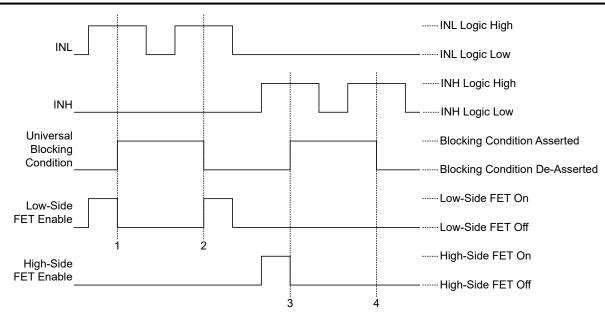

- Low-side / high-side gate-drive interlock

- High-side gate-drive signal level shifter

- Smart-switched bootstrap diode function

- High-side start up : < 8µs

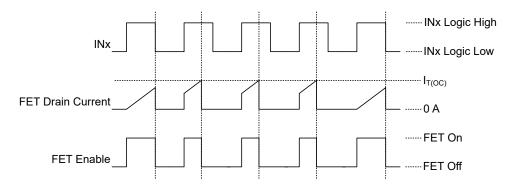

- Low-side / high-side cycle-by-cycle over-current protection

- Over-temperature protection with FLT pin reporting

- AUX idle quiescent current: 250µA

- AUX standby quiescent current: 50µA

- BST idle quiescent current: 65µA

- Maximum supply and input logic pin voltage: 26V

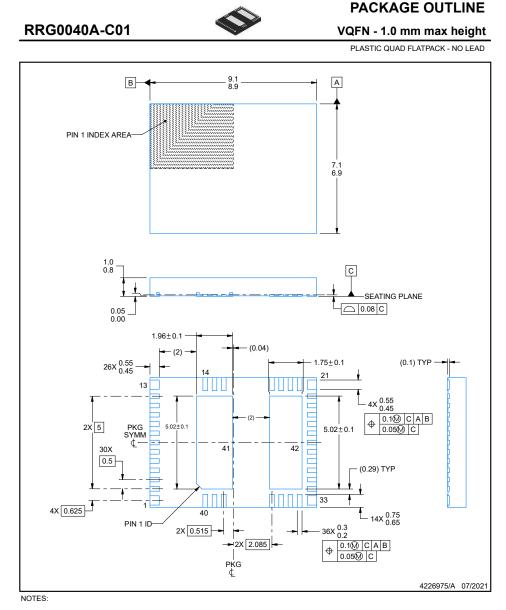

- 9×7mm QFN package with dual thermal pads

# 2 Applications

- AC/DC adapters and chargers

- AC/DC USB wall outlet power supplies

- AC/DC auxiliary power supplies

- Mobile wall charger design

- USB wall power outlet

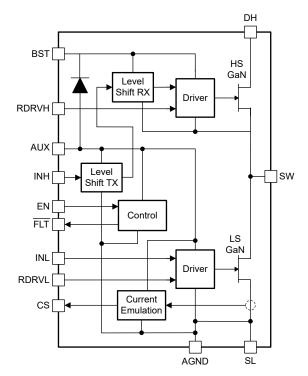

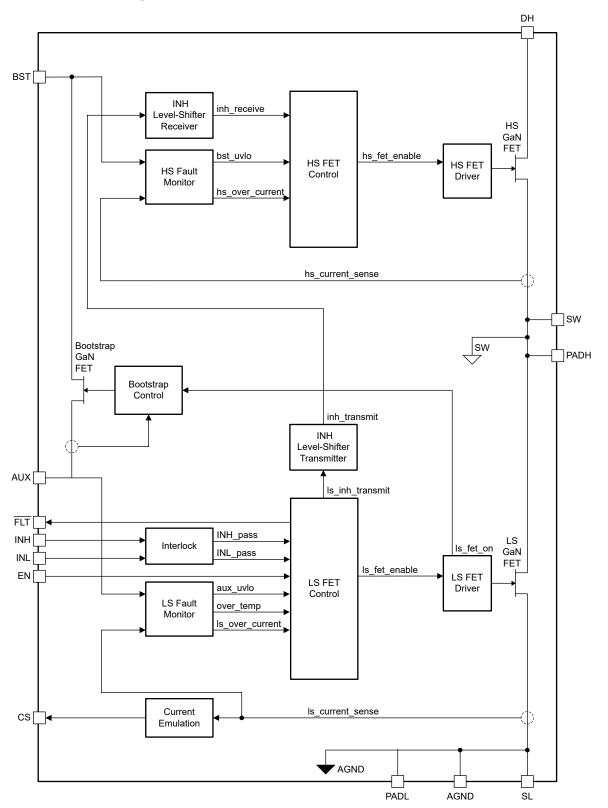

Simplified Block Diagram

### 3 Description

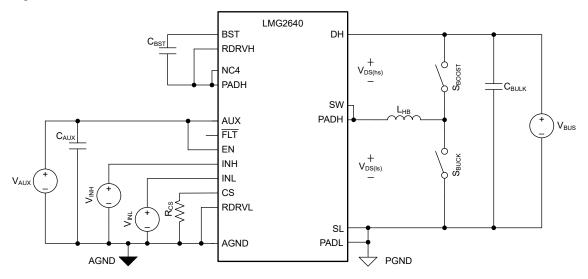

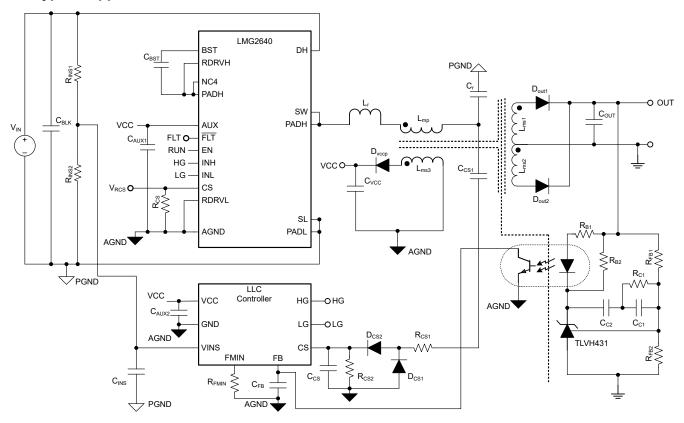

The LMG2640 is a 650V GaN power-FET half bridge intended for switch mode power supply applications. The LMG2640 simplifies design, reduces component count, and reduces board space by integrating halfbridge power FETs, gate drivers, bootstrap diode, and high-side gate-drive level shifter in a 9mm by 7mm QFN package.

The low-side current-sense emulation reduces power dissipation compared to the traditional current-sense resistor and allows the low-side thermal pad to be connected to the cooling PCB power ground.

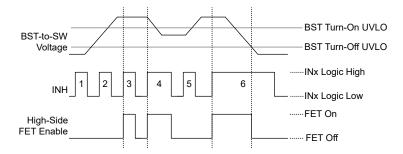

The high-side gate-drive signal level shifter eliminates noise and burst-mode power dissipation problems found with external solutions. The smart-switched GaN bootstrap FET has no diode forward-voltage drop, avoids overcharging the high-side supply, and has zero reverse-recovery charge.

The LMG2640 supports converter light-load efficiency requirements and burst-mode operation with low quiescent currents and fast start-up times. Protection features include FET turn-on interlock, under-voltage lockout (UVLO), cycle-by-cycle current limit, and overtemperature shut down.

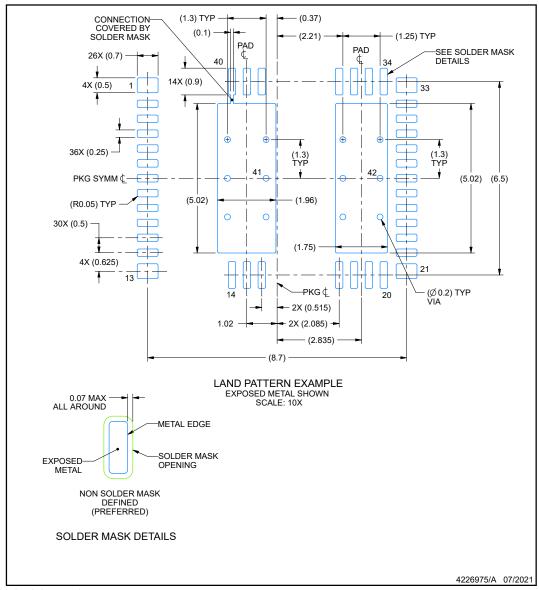

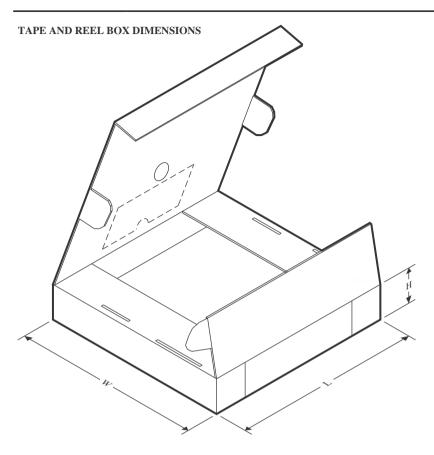

**Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE(2) |  |  |

|-------------|------------------------|-----------------|--|--|

| LMG2640     | RRG (QFN, 40)          | 9.00mm × 7.00mm |  |  |

- For more information, see the Section 11 section.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

**Package View**

# **Table of Contents**

| 1 Features1                              | 7.3 Feature Description                             | 22 |

|------------------------------------------|-----------------------------------------------------|----|

| 2 Applications1                          | 7.4 Device Functional Modes                         |    |

| 3 Description1                           | 8 Application and Implementation                    | 29 |

| 4 Pin Configuration and Functions3       | 8.1 Application Information                         | 29 |

| 5 Specifications5                        | 8.2 Typical Application                             |    |

| 5.1 Absolute Maximum Ratings5            | 8.3 Power Supply Recommendations                    |    |

| 5.2 ESD Ratings5                         | 8.4 Layout                                          | 32 |

| 5.3 Recommended Operating Conditions6    | 9 Device and Documentation Support                  |    |

| 5.4 Thermal Information6                 | 9.1 Documentation Support                           | 34 |

| 5.5 Electrical Characteristics7          | 9.2 Receiving Notification of Documentation Updates |    |

| 5.6 Switching Characteristics10          | 9.3 Support Resources                               | 34 |

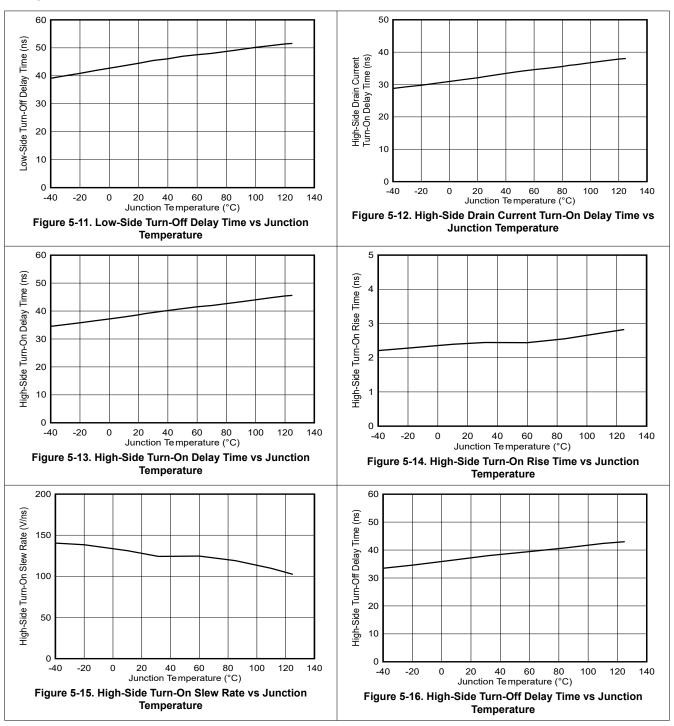

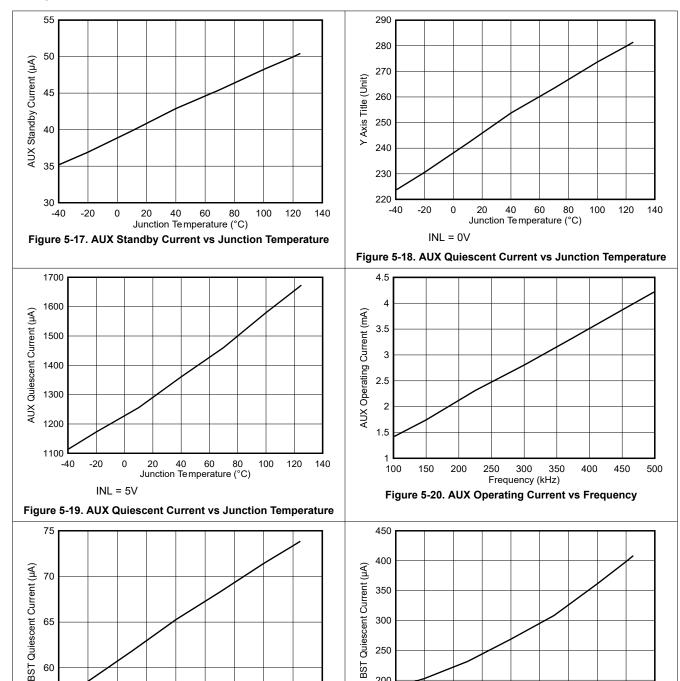

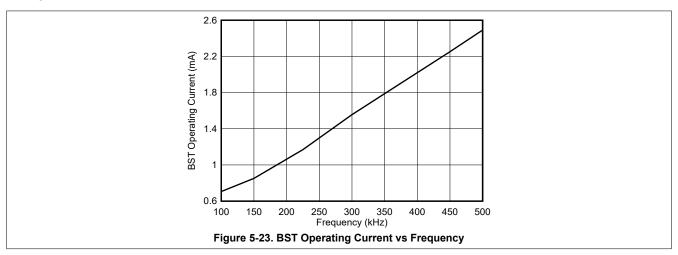

| 5.7 Typical Characteristics13            | 9.4 Trademarks                                      |    |

| 6 Parameter Measurement Information18    | 9.5 Electrostatic Discharge Caution                 |    |

| 6.1 GaN Power FET Switching Parameters18 | 9.6 Glossary                                        |    |

| 7 Detailed Description20                 | 10 Revision History                                 | 34 |

| 7.1 Overview                             | 11 Mechanical, Packaging, and Orderable             |    |

| 7.2 Functional Block Diagram21           |                                                     | 35 |

| · ·                                      |                                                     |    |

# **4 Pin Configuration and Functions**

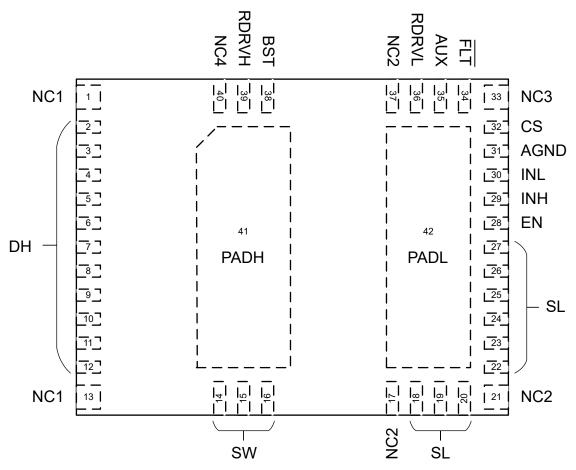

Figure 4-1. RRG Package, 40-Pin VQFN (Top View)

## **Table 4-1. Pin Functions**

| PIN   |              | (1)                 | DEGODISTION                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO.          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                      |

| NC1   | 1, 13        | NC                  | Used to anchor QFN package to PCB. Pins must be soldered to PCB landing pads. The PCB landing pads are non-solder mask defined pads and must not be physically connected to any other metal on the PCB. Internally connected to DH.                                                                                                                              |

| DH    | 2–12         | Р                   | High-side GaN FET drain. Internally connected to NC1.                                                                                                                                                                                                                                                                                                            |

| sw    | 14–16        | Р                   | GaN FET half-bridge switch node between the high-side GaN FET source and low-side GaN FET drain. Internally connected to PADH.                                                                                                                                                                                                                                   |

| NC2   | 17, 21, 37   | NC                  | Used to anchor QFN package to PCB. Pins must be soldered to PCB landing pads.  The PCB landing pads are non-solder mask defined pads and must not be physically connected to any other metal on the PCB. Internally connected to AGND, SL, and PADL.                                                                                                             |

| SL    | 18–20, 22–27 | Р                   | Low-side GaN FET source. Internally connected to AGND, PADL, and NC2.                                                                                                                                                                                                                                                                                            |

| EN    | 28           | I                   | Enable. Used to toggle between active and standby modes. The standby mode has reduced quiescent current to support converter light load efficiency targets. There is a forward biased ESD diode from EN to AUX so avoid driving EN higher than AUX.                                                                                                              |

| INH   | 29           | I                   | High-side gate-drive control input. Referenced to AGND. Signal is level shifted internally to the high-side GaN FET driver. There is a forward biased ESD diode from INH to AUX so avoid driving INH higher than AUX.                                                                                                                                            |

| INL   | 30           | I                   | Low-side gate-drive control input. Referenced to AGND. There is a forward biased ESD diode from INL to AUX so avoid driving INL higher than AUX.                                                                                                                                                                                                                 |

| AGND  | 31           | GND                 | Low-side analog ground. Internally connected to SL, PADL, and NC2.                                                                                                                                                                                                                                                                                               |

| cs    | 32           | 0                   | Current-sense emulation output. Outputs 0.616 ma/A scaled replica of the low-side GaN FET current. Feed output current into a resistor to create a current sense voltage signal. Reference the resistor to the power supply controller IC local ground. This function replaces the external current-sense resistor that is used in series with the low-side FET. |

| NC3   | 33           | NC                  | Used to anchor QFN package to PCB. Pin must be soldered to a PCB landing pad. The PCB landing pad is non-solder mask defined pad and must not be physically connected to any other metal on the PCB. Pin not connected internally.                                                                                                                               |

| FLT   | 34           | 0                   | Active-low fault output. Open-drain output that asserts during an over-temperature shutdown.                                                                                                                                                                                                                                                                     |

| AUX   | 35           | Р                   | Auxiliary voltage rail. Low-side supply voltage. Connect a local bypass capacitor between AUX and AGND.                                                                                                                                                                                                                                                          |

| RDRVL | 36           | I                   | Short to AGND.                                                                                                                                                                                                                                                                                                                                                   |

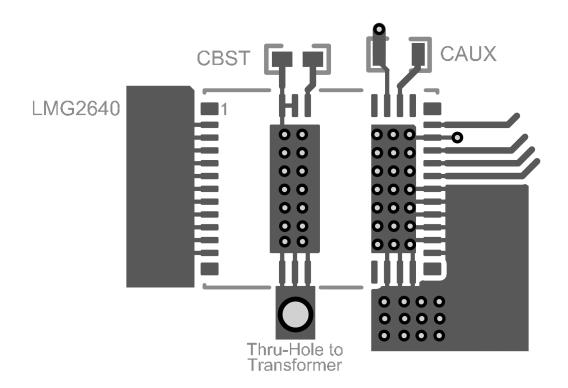

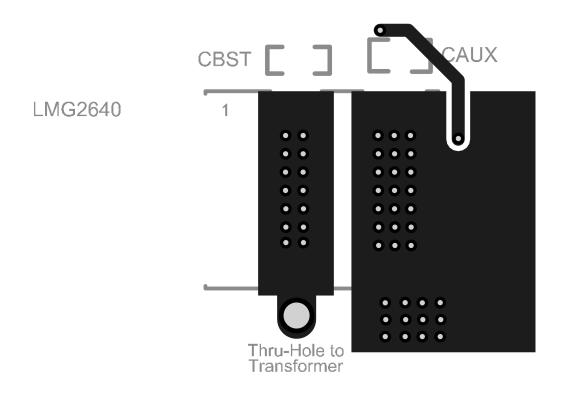

| BST   | 38           | Р                   | Bootstrap voltage rail. High-side supply voltage. The bootstrap diode function between AUX and BST is internally provided. Connect an appropriately sized bootstrap capacitor between BST and SW. Recommend to make the SW connection using NC4 as a pass through connection to PADH (PADH = SW) as explained in the NC4 description.                            |

| RDRVH | 39           | I                   | Short to SW.Recommend to make the SW connection using NC4 as a pass through connection to PADH (PADH = SW) as explained in the NC4 description.                                                                                                                                                                                                                  |

| NC4   | 40           | NC                  | Pin is not functional. Pin is high impedance and referenced to SW. Recommend to connect pin to PADH (PADH = SW) to use as convenient connection for the BST bypass capacitor and the RDRVH. See the example board layout in the <i>Layout Example</i> section.                                                                                                   |

| PADH  | 41           | TP                  | High-side thermal pad. Internally connected to SW. All the SW current can be conducted with PADH (PADH = SW).                                                                                                                                                                                                                                                    |

| PADL  | 42           | TP                  | Low-side thermal pad. Internally connected to SL, AGND, and NC2. All the SL current can be conducted with PADL (PADL = SL).                                                                                                                                                                                                                                      |

<sup>(1)</sup> I = Input, O = Output, G = Ground, P = Power, NC = No Connect, TP = Thermal Pad.

# **5 Specifications**

## 5.1 Absolute Maximum Ratings

Unless otherwise noted: voltages are respect to AGND<sup>(1)</sup>

|                            |                                                                                |                              | MIN  | MAX                    | UNIT |

|----------------------------|--------------------------------------------------------------------------------|------------------------------|------|------------------------|------|

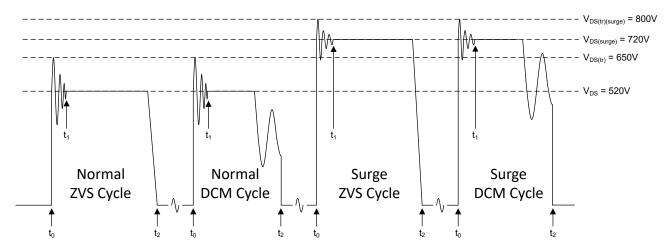

| V <sub>DS(Is)</sub>        | Low-side drain-source (SW to SL) voltage, FET off                              |                              |      | 650                    | V    |

| V <sub>DS(surge)(ls)</sub> | Low-side drain-source (SW to SL) voltage, surge condit                         | ion, FET off <sup>(2)</sup>  |      | 720                    | V    |

| V <sub>DS(tr)(surge)</sub> | Low-side drain-source (SW to SL) transient ringing peal FET off <sup>(2)</sup> | k voltage, surge condition,  |      | 800                    | V    |

| V <sub>DS(hs)</sub>        | High-side drain source (DH to SW) voltage, FET off                             |                              |      | 650                    | V    |

| V <sub>DS(surge)(hs)</sub> | High-side drain-source (DH to SW) voltage, surge cond                          |                              | 720  | V                      |      |

| V <sub>DS(tr)(surge)</sub> | High-side drain-source (DH to SW) transient ringing pea                        | ak voltage, surge condition, |      | 800                    | V    |

|                            |                                                                                | AUX                          | -0.3 | 30                     | V    |

|                            | Din veltage                                                                    | EN, INL, INH, FLT            | -0.3 | V <sub>AUX</sub> + 0.3 | V    |

|                            | Pin voltage                                                                    | CS                           | -0.3 | 5.5                    | V    |

|                            |                                                                                | RDRVL                        | -0.3 | 4                      | V    |

|                            | Pin voltage to SW                                                              | BST                          | -0.3 |                        | V    |

|                            | Pili voltage to SW                                                             | RDRVH                        | -0.3 | 4                      | V    |

| I <sub>D(cnts)(ls)</sub>   | Low-side drain (SW to SL) continuous current, FET on                           |                              | -10  | Internally<br>limited  | Α    |

| I <sub>S(cnts)(Is)</sub>   | Low-side source (SL to SW) continuous current, FET of                          | f                            |      | 10                     | Α    |

| I <sub>D(cnts)(hs)</sub>   | High-side drain (DH to SW) continuous current, FET on                          |                              | -10  | Internally<br>limited  | Α    |

| I <sub>S(cnts)(hs)</sub>   | High-side source (SW to DH) continuous current, FET of                         | off                          |      | 10                     | Α    |

|                            |                                                                                | CS                           |      | 10                     | mA   |

|                            | Positive sink current                                                          | FLT (while asserted)         |      | Internally<br>limited  | mA   |

| TJ                         | Operating junction temperature                                                 |                              | -40  | 150                    | °C   |

| T <sub>stg</sub>           | Storage temperature                                                            |                              | -65  | 150                    | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) See Section 7.3.1 for more information on the GaN power FET switching capability.

### 5.2 ESD Ratings

Copyright © 2024 Texas Instruments Incorporated

|                    |               |                                                                             |                                       | VALUE | UNIT |

|--------------------|---------------|-----------------------------------------------------------------------------|---------------------------------------|-------|------|

|                    |               | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>           | Pins 1 through 16, Pins 38 through 40 | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic |                                                                             | Pins 17 through 37                    | ±2000 | V    |

| (ESD)              | Charged de    | Charged device model<br>(CDM), per ANSI/ESDA/JEDEC<br>JS-002 <sup>(2)</sup> |                                       | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **5.3 Recommended Operating Conditions**

Unless otherwise noted: voltages are respect to AGND

|                          |                                           |                 | MIN                  | NOM MAX          | UNIT |

|--------------------------|-------------------------------------------|-----------------|----------------------|------------------|------|

|                          | Supply voltage                            | AUX             | 10                   | 26               | V    |

|                          | Supply voltage to SW                      | BST             | 7.5                  | 26               | V    |

|                          | Input voltage                             | EN, INL, INH    | 0                    | V <sub>AUX</sub> | V    |

|                          | Pull-up voltage on open-drain output      | FLT             | 0                    | V <sub>AUX</sub> | V    |

| V <sub>IH</sub>          | High-level input voltage                  | EN, INL, INH    | 2.5                  |                  | V    |

| V <sub>IL</sub>          | Low-level input voltage                   | EIN, IINL, IINП |                      | 0.6              | V    |

| I <sub>D(cnts)(ls)</sub> | Low-side drain (SW to SL) continuous curr | ent, FET on     | -8.2                 | 8.2              | Α    |

| I <sub>D(cnts)(hs)</sub> | High-side drain (DH to SW) continuous cur | rent, FET on    | -8.2                 | 8.2              | Α    |

| C <sub>AUX</sub>         | AUX to AGND capacitance from external b   | ypass capacitor | 3 x C <sub>BST</sub> |                  | μF   |

| C <sub>BST_SW</sub>      | BST to SW capacitance from external bypa  | ass capacitor   | 0.010                |                  | μF   |

## **5.4 Thermal Information**

|                       |                                              | LMG2640    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RRG (VQFN) | UNIT |

|                       |                                              | 40 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 22.8       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.21       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 5.5 Electrical Characteristics

1) Symbol definitions:  $V_{DS(|s)} = SW$  to SL voltage;  $I_{DS(|s)} = SW$  to SL current;  $V_{DS(hs)} = DH$  to SW voltage;  $I_{D(hs)} = DH$  to SW current; 2) Unless otherwise noted: voltage, resistance, and capacitance are respect to AGND;  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ ;  $10V \le V_{AUX} \le 26V$ ;  $7.5V \le V_{BST-SW} \le 26V$ ;  $V_{EN} = 5V$ ;  $V_{INL} = 0V$ ;  $V_{INH} = 0V$ ;  $V_{INH} = 10V$ ;  $V_{INH} = 1$

|                         | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                              | MIN | TYP  | MAX      | UNIT  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|------|----------|-------|

| LOW-SID                 | E GAN POWER FET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |     |      | <u>'</u> |       |

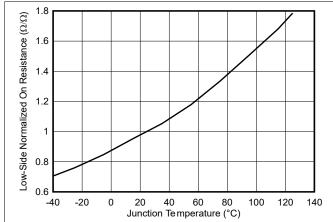

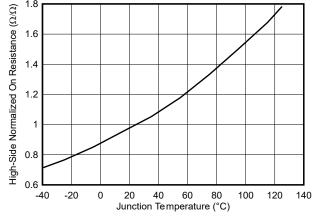

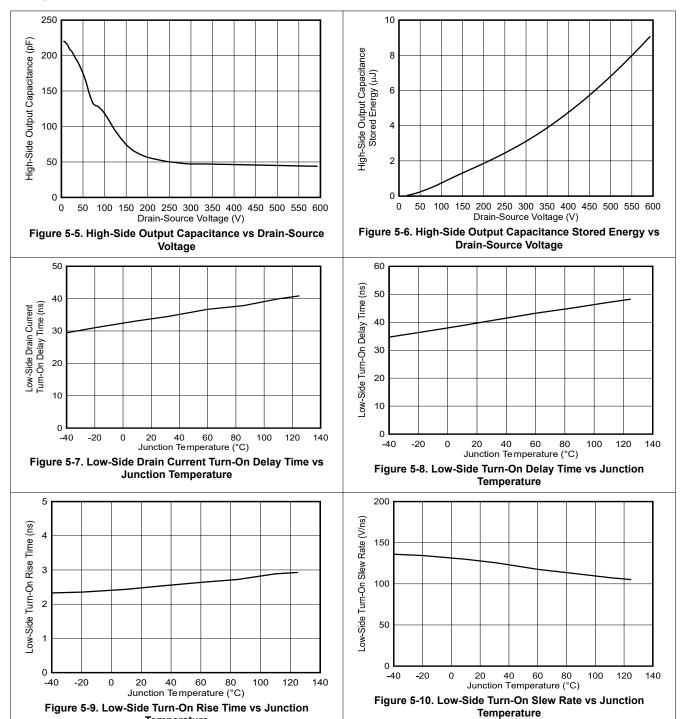

| <b>D</b>                | During a control (OWA) of the control of the contro | V <sub>INL</sub> = 5V, I <sub>D(Is)</sub> = 4.8A, T <sub>J</sub> = 25°C      |     | 105  |          | 0     |

| $R_{DS(on)(ls)}$        | Drain-source (SW to SL) on resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>INL</sub> = 5V, I <sub>D(Is)</sub> = 4.8A, T <sub>J</sub> = 125°C     |     | 200  |          | mΩ    |

|                         | Durin (OWA) OLVI alama and and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DS(hs)</sub> = 0V, V <sub>DS(ls)</sub> = 650V, T <sub>J</sub> = 25°C  |     | 3.1  |          |       |

| I <sub>DSS(Is)</sub>    | Drain (SW to SL) leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>DS(hs)</sub> = 0V, V <sub>DS(ls)</sub> = 650V, T <sub>J</sub> = 125°C |     | 15.4 |          | μΑ    |

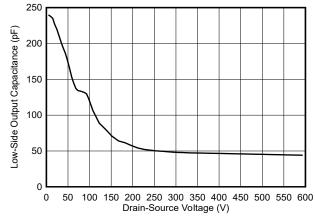

| Q <sub>OSS(ls)</sub>    | Output (SW to SL) charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |     | 33.6 |          | nC    |

| C <sub>OSS(Is)</sub>    | Output (SW to SL) capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |     | 51.0 |          | pF    |

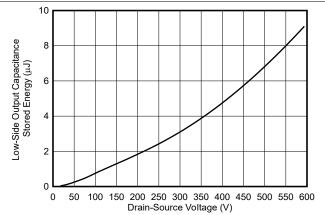

| E <sub>OSS(Is)</sub>    | Output (SW to SL) capacitance stored energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>DS(hs)</sub> = 0V, V <sub>DS(ls)</sub> = 400V                         |     | 4.64 |          | μJ    |

| C <sub>OSS,er(Is)</sub> | Energy related effective output (SW to SL) capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                              |     | 58.0 |          | pF    |

| C <sub>OSS,tr(ls)</sub> | Time related effective output (SW to SL) capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>DS(hs)</sub> = 0V, V <sub>DS(ls)</sub> = 0V to 400V                   |     | 84.0 |          | pF    |

| Q <sub>RR(Is)</sub>     | Reverse recovery charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |     | 0    |          | nC    |

| HIGH-SID                | E GAN POWER FET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |     |      |          |       |

| R <sub>DS(on)</sub>     | Drain-source (DH to SW) on resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>INH</sub> = 5V, I <sub>D(hs)</sub> = 4.8A, T <sub>J</sub> = 25°C      |     | 105  |          | mΩ    |

| (hs)                    | Diam-source (Dir to Sw) on resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>INH</sub> = 5V, I <sub>D(hs)</sub> = 4.8A, T <sub>J</sub> = 125°C     |     | 200  |          | 11122 |

| I                       | Drain (DH to SW) leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{DS(ls)} = 0V, V_{DS(hs)} = 650V, T_J = 25^{\circ}C$                      |     | 3.1  |          | μA    |

| I <sub>DSS(hs)</sub>    | Diam (Dir to Sw) leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{DS(ls)} = 0V, V_{DS(hs)} = 650V, T_J = 125^{\circ}C$                     |     | 15.4 |          | μΑ    |

| Q <sub>OSS(hs)</sub>    | Output (DH to SW) charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |     | 33.6 |          | nC    |

| C <sub>OSS(hs)</sub>    | Output (DH to SW) capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |     | 51.0 |          | pF    |

| E <sub>OSS(hs)</sub>    | Output (DH to SW) capacitance stored energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_{DS(ls)} = 0V, V_{DS(hs)} = 400V$                                         |     | 4.64 |          | μJ    |

| C <sub>OSS,er(hs</sub>  | Energy related effective output (DH to SW) capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                              |     | 58.0 |          | pF    |

| $C_{OSS,tr(hs)}$        | Time related effective output (DH to SW) capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{DS(ls)} = 0V, V_{DS(hs)} = 0V \text{ to } 400V$                          |     | 84.0 |          | pF    |

| Q <sub>RR(hs)</sub>     | Reverse recovery charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              |     | 0    |          | nC    |

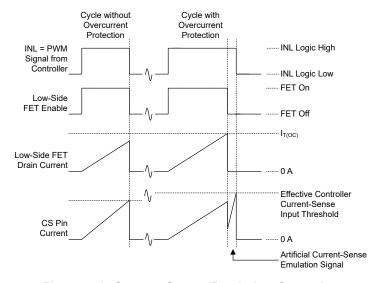

| LOW-SID                 | E OVERCURRENT PROTECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |     |      |          |       |

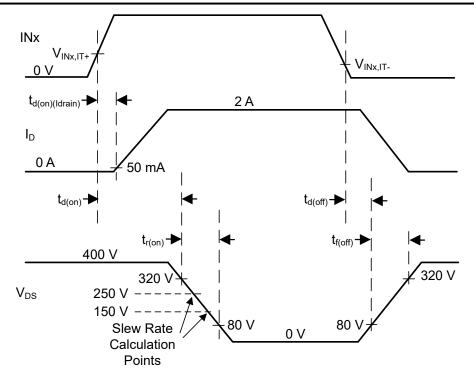

| $I_{T(OC)(ls)}$         | Overcurrent fault – threshold current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              | 8.2 | 9.1  | 10       | Α     |