# **INAx133 High-Speed, Precision Difference Amplifiers**

#### 1 Features

- Single, dual versions

- Low offset voltage: ±450µV (maximum)

- Low offset voltage drift: ±5µV/°C (maximum)

- Low gain error: 0.05% (maximum)

- Wide bandwidth: 1.5MHz

- High slew rate: 5V/µs

- Fast settling time: 5.5µs to 0.01%

- Low guiescent current: 950µA

- Wide supply range: ±2.25V to ±18V

## 2 Applications

- Battery cell formation & test equipment

- Sensor tag & data logger

- Servo drive position feedback

- Level transmitter

- String inverter

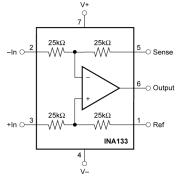

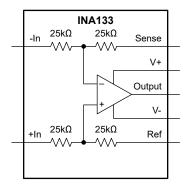

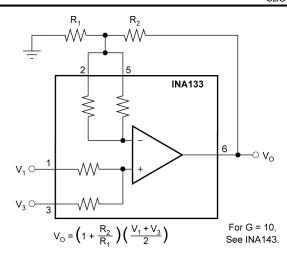

**INA133 Simplified Internal Schematic**

### 3 Description

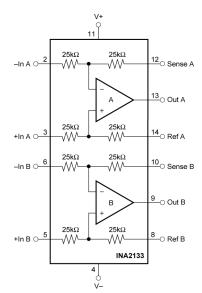

The INA133 and INA2133 are high slew rate, unity gain difference amplifiers made up of a precision operational amplifier with a precision resistor network. The on-chip resistors are laser trimmed for accurate gain and high common-mode rejection. Excellent tracking of resistors (TCR) maintains gain accuracy and common-mode rejection over temperature. The INAx133 operates over a wide supply range, ±2.25V to ±18V (+4.5V to +36V single supply), and that input common-mode voltage range extends beyond the positive and negative supply rails.

The differential amplifier is the foundation of many commonly used circuits. The INAx133 provides this precision circuit function for cost-optimized designs.

The single INA133 version is available in the SOIC-8 surface mount package. The dual INA2133 version is available in SOIC-14 package. Both are specified for operation over the industrial temperature range -40°C to +85°C.

**Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| INA133      | D (SOIC, 8)            | 4.90mm × 6.00mm             |

| INA2133     | D (SOIC, 14)           | 8.65mm × 6.00mm             |

- For all available packages, see the orderable addendum in Section 10.

- The package size (length × width) is a nominal value and includes pins, where applicable.

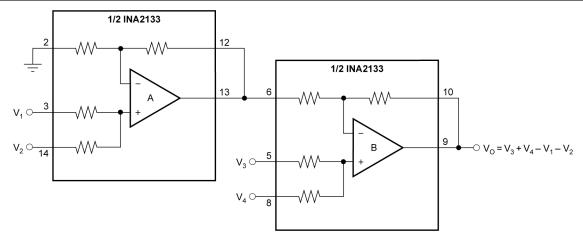

**INA2133 Simplified Internal Schematic**

# **Table of Contents**

| 1 Features                           | 1  | 7.1 Application Information                      | 14    |

|--------------------------------------|----|--------------------------------------------------|-------|

| 2 Applications                       | 1  | 7.2 Typical Application                          | 15    |

| 3 Description                        | 1  | 7.3 Additional Applications                      |       |

| 4 Pin Configuration and Functions    | 3  | 7.4 Power Supply Recommendations                 | 24    |

| 5 Specifications                     | 5  | 7.5 Layout                                       | 24    |

| 5.1 Absolute Maximum Ratings         | 5  | 8 Device and Documentation Support               |       |

| 5.2 Recommended Operating Conditions | 5  | 8.1 Device Support                               | 26    |

| 5.3 Thermal Information              | 5  | 8.2 Receiving Notification of Documentation Upda | tes26 |

| 5.4 Electrical Characteristics       | 6  | 8.3 Support Resources                            | 26    |

| 5.5 Typical Characteristics          | 8  | 8.4 Trademarks                                   | 26    |

| 6 Detailed Description               | 12 | 8.5 Electrostatic Discharge Caution              | 26    |

| 6.1 Overview                         | 12 | 8.6 Glossary                                     | 27    |

| 6.2 Functional Block Diagram         | 12 | 9 Revision History                               | 27    |

| 6.3 Feature Description              | 12 | 10 Mechanical, Packaging, and Orderable          |       |

| 6.4 Device Functional Modes          | 13 | Information                                      | 27    |

| 7 Application and Implementation     | 14 |                                                  |       |

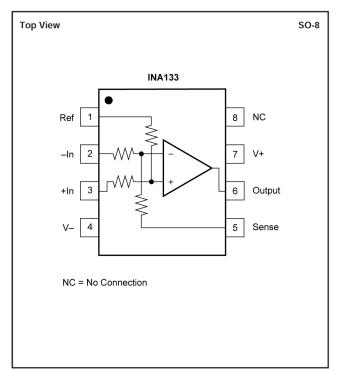

# **4 Pin Configuration and Functions**

Table 4-1. Pin Functions: INA133

| NAME   | NO. | TYPE   | DESCRIPTION                                                                    |  |  |

|--------|-----|--------|--------------------------------------------------------------------------------|--|--|

| +In    | 3   | Input  | Positive (noninverting) input 25kΩ resistor to noninverting terminal of op amp |  |  |

| -In    | 2   | Input  | egative (inverting) input 25kΩ resistor to inverting terminal of op amp        |  |  |

| Output | 6   | Output | Output                                                                         |  |  |

| Ref    | 1   | Input  | Reference input 25kΩ resistor to noninverting terminal of op amp               |  |  |

| V+     | 7   | _      | Positive (highest) power supply                                                |  |  |

| V-     | 4   | -      | Negative (lowest) power supply                                                 |  |  |

| Sense  | 5   | Input  | Sense input 25kΩ resistor to inverting terminal of op amp                      |  |  |

| NC     | 8   | -      | No internal connection (can be left floating)                                  |  |  |

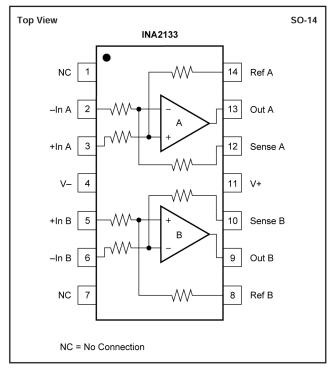

Table 4-2. Pin Functions: INA2133

| NAME    | NO. | TYPE   | DESCRIPTION                                                                                       |  |  |  |

|---------|-----|--------|---------------------------------------------------------------------------------------------------|--|--|--|

| +In A   | 3   | Input  | Positive (noninverting) input, Channel A $25k\Omega$ resistor to noninverting terminal of op amp  |  |  |  |

| -In A   | 2   | Input  | Negative (inverting) input, Channel A 25kΩ resistor to inverting terminal of op amp               |  |  |  |

| +In B   | 5   | Input  | Positive (noninverting) input, Channel B $25k\Omega$ resistor to non-inverting terminal of op amp |  |  |  |

| -In B   | 6   | Input  | Negative (inverting) input, Channel B 25kΩ resistor to inverting terminal of op amp               |  |  |  |

| Out A   | 13  | Output | Output, Channel A                                                                                 |  |  |  |

| Out B   | 9   | Output | Output, Channel B                                                                                 |  |  |  |

| Ref A   | 14  | Input  | Reference input, Channel A 25kΩ resistor to noninverting terminal of op amp                       |  |  |  |

| Ref B   | 8   | Input  | Reference input, Channel B 25kΩ resistor to noninverting terminal of op amp                       |  |  |  |

| Sense A | 12  | Input  | Sense input, Channel A 25kΩ resistor to inverting terminal of op amp                              |  |  |  |

| Sense B | 10  | Input  | Sense input, Channel B 25kΩ resistor to inverting terminal of op amp                              |  |  |  |

| V+      | 11  | -      | Positive (highest) power supply                                                                   |  |  |  |

### Table 4-2. Pin Functions: INA2133 (continued)

| NAME | NO. | TYPE | DESCRIPTION                    |

|------|-----|------|--------------------------------|

| V-   | 4   | _    | Negative (lowest) power supply |

### **5.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                           |                           | MIN        | MAX                | UNIT |

|-------------------------------------------|---------------------------|------------|--------------------|------|

| Supply voltage, V <sub>S</sub> = (V+) – ( | V–)                       | 0          | 36                 | V    |

| Signal input nine                         | Input pins                | 0          | 2 x V <sub>S</sub> | V    |

| Signal input pins                         | Sense, and REF pins       | 0          | Vs                 | V    |

| Output short-circuit <sup>(2)</sup>       |                           | Continuous | 3                  |      |

|                                           | Operating, T <sub>A</sub> | -55        | 125                |      |

| Temperature                               | Junction, T <sub>J</sub>  |            | 150                | °C   |

|                                           | Storage, T <sub>stg</sub> | -55        | 125                |      |

<sup>(1)</sup> Operation outside the *Absolute Maximum Ratings* may cause permanent device damage. *Absolute Maximum Ratings* do not imply functional operation of the device at these or any other conditions beyond those listed under *Recommended Operating Conditions*. If used outside the *Recommended Operating Conditions* but within the *Absolute Maximum Ratings*, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) Short-circuit to V<sub>S</sub>/2, one channel per package.

### **5.2 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                       |               | MIN   | NOM | MAX | UNIT |

|-----------------------|---------------|-------|-----|-----|------|

| Supply voltage        | Single supply | 4.5   | 30  | 36  | \/   |

| Supply voltage        | Dual supply   | ±2.25 | ±15 | ±18 | V    |

| Specified temperature |               | -40   |     | 85  | °C   |

### 5.3 Thermal Information

|                       |                                              | INA133   | INA2133  |      |

|-----------------------|----------------------------------------------|----------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | 8 PINS   | 14 PINS  | UNIT |

|                       |                                              | D (SOIC) | D (SOIC) | -    |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 108.9    | 71.4     | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 45.9     | 33.1     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 56.6     | 31.2     | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 4.8      | 3.4      | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 55.7     | 30.9     | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A      | N/A      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### **5.4 Electrical Characteristics**

at  $T_A$  = 25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$  connected to ground,  $V_{REF}$  = 0V, and G = 1, applies to all packages and part variants (unless otherwise noted)

|                    | PARAMETER                            | TEST CONDITIO                                                            | MIN                    | TYP          | MAX          | UNIT               |                    |  |

|--------------------|--------------------------------------|--------------------------------------------------------------------------|------------------------|--------------|--------------|--------------------|--------------------|--|

| INPUT              |                                      |                                                                          |                        |              |              |                    |                    |  |

|                    |                                      | RTO <sup>(1)</sup> (2), V <sub>CM</sub> = 0V                             | U variant              |              | ±150         | ±450               | μV                 |  |

| V                  | Offeet voltage                       | KTOWY (= , V <sub>CM</sub> = UV                                          | UA variant             |              | ±150         | ±900               | μV                 |  |

| V <sub>OS</sub>    | Offset voltage                       | RTO <sup>(1)</sup> (2), V <sub>CM</sub> = 0V, V <sub>S</sub> = ±5V       | U variant              |              | ±300         | ±750               | μV                 |  |

|                    |                                      | NIO(**, V <sub>CM</sub> = 0V, V <sub>S</sub> = ±5V                       | UA variant             |              | ±300         | ±1500              | μV                 |  |

|                    |                                      |                                                                          |                        |              | ±2           | ±5                 | μV/°C              |  |

|                    | Offset voltage drift                 | RTO <sup>(1)</sup> (2), $T_A = -40^{\circ}\text{C}$ to +85°C             | $V_S = \pm 5V$         |              | ±2           |                    | μV/°C              |  |

| PSRR               | Power-supply rejection               | RTO <sup>(1)</sup> (2), V <sub>S</sub> = ±2.25V to ±18V                  | U variant              |              | ±10          | ±30                | μV/V               |  |

| PSRK               | ratio                                | R10(7) (-7, V <sub>S</sub> = ±2.25V to ±18V                              | UA variant             | 850          | 900          | 950                | μV/V               |  |

|                    | Long-term stability                  | RTO <sup>(1) (2)</sup>                                                   |                        | 0.3          |              | μV/√ <del>mo</del> |                    |  |

| Z <sub>IN-DM</sub> | Differential impedance (3)           |                                                                          |                        |              | 50           |                    | kΩ                 |  |

| Z <sub>IN-CM</sub> | Common-mode impedance <sup>(3)</sup> | V <sub>CM</sub> = 0V                                                     |                        |              | 25           |                    | kΩ                 |  |

| V                  | Common-mode voltage                  | V = 0V V = 14EV and V = 1EV                                              | Positive               | 2 x (V+) - 3 | 2 x (V+) – 2 |                    | V                  |  |

| V <sub>CM</sub>    | range <sup>(4)</sup>                 | $V_0 = 0V$ , $V_S = \pm 15V$ and $V_S = \pm 5V$                          | Negative               | 2 x (V-) + 3 | 2 x (V–) + 2 |                    | V                  |  |

| CMRR               | Common-mode rejection                | $V_S = \pm 15V$ and $V_S = \pm 5V$ , $V_{CM} = 2 x$                      | U variant              | 80           | 90           |                    | dB                 |  |

| CIVIRR             | ratio                                | $(V-) + 3 \text{ to } 2 \times (V+) - 3, R_S = 0\Omega$                  | UA variant             | 74           | 90           |                    | dB                 |  |

| NOISE V            | OLTAGE                               |                                                                          | •                      |              |              |                    |                    |  |

|                    |                                      |                                                                          | f = 0.01Hz to 10Hz     |              | 2            |                    | μV <sub>PP</sub>   |  |

| _                  | Valtaga najaa                        | RTO <sup>(2) (5)</sup>                                                   | f = 10Hz               |              | 80           |                    |                    |  |

| e <sub>N</sub>     | Voltage noise                        | RTO(2) (6)                                                               | f = 100Hz              |              | 60           |                    | nV/√ <del>Hz</del> |  |

|                    |                                      |                                                                          | f = 1kHz               |              | 57           |                    |                    |  |

| GAIN               |                                      |                                                                          |                        |              |              |                    |                    |  |

| G                  | Initial gain                         | $V_S = \pm 15V$ and $V_S = \pm 5V$                                       |                        |              | 1            |                    | V/V                |  |

|                    | Gain error                           | $V_S = \pm 15V$ and $V_S = \pm 5V$ , (V-) + 1V $\leq$                    | U variant              |              | ±0.02        | ±0.05              | %                  |  |

| GE                 | Gain error                           | V <sub>O</sub> ≤ (V+) - 1.5V                                             | UA variant             |              | ±0.02        | ±0.1               | 70                 |  |

|                    | Gain drift                           | T <sub>A</sub> = -40°C to +85°C                                          |                        |              | ±1           | ±10                | ppm/°C             |  |

|                    | Gain nonlinearity                    | $V_S = \pm 15V$ and $V_S = \pm 5V$ , $(V-) + 1V \le V_O \le (V+) - 1.5V$ | U variant              |              | ±0.0001      | ±0.001             | % of FSR           |  |

|                    | — Gain nonlinearity                  | $V_S = \pm 15V$ and $V_S = \pm 5V$ , $(V-) + 1V \le V_O \le (V+) - 1.5V$ | UA variant             |              | ±0.0001      | ±0.002             | % of FSR           |  |

| ОИТРИТ             | Γ                                    |                                                                          |                        |              |              | '                  |                    |  |

|                    |                                      | Desitive V = ±15V and V = ±5V                                            |                        | (V+) - 1.5   | (V+) - 1.3   |                    | V                  |  |

| \/                 | Output voltage, gain error <         | Positive, $V_S = \pm 15V$ and $V_S = \pm 5V$                             | R <sub>L</sub> = 100kΩ |              | (V+) - 0.8   |                    |                    |  |

| Vo                 | 0.1%                                 | Negative V = ±15V and V = ±5V                                            |                        | (V-) + 1     | (V+)-0.8     |                    |                    |  |

|                    |                                      | Negative, $V_S = \pm 15V$ and $V_S = \pm 5V$                             | R <sub>L</sub> = 100kΩ |              | (V-)+0.3     |                    |                    |  |

|                    | Capacitive load (stable operation)   |                                                                          |                        |              | 1000         |                    | pF                 |  |

| I <sub>SC</sub>    | Short-circuit current                | Continuous to V <sub>S</sub> / 2                                         |                        |              | +32/ –25     |                    | mA                 |  |

Product Folder Links: INA133 INA2133

at  $T_A$  = 25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$  connected to ground,  $V_{REF}$  = 0V, and G = 1, applies to all packages and part variants (unless otherwise noted)

|                | PARAMETER              | TEST CONDITIONS                                         | MIN | TYP   | MAX  | UNIT |

|----------------|------------------------|---------------------------------------------------------|-----|-------|------|------|

| FREQU          | JENCY RESPONSE         |                                                         |     |       |      |      |

| BW             | Bandwidth, –3dB        |                                                         |     | 1.5   |      | MHz  |

| SR             | Slew rate              |                                                         |     | 5     |      | V/µs |

| +.             | Settling time          | 0.1%, V <sub>STEP</sub> = 10V, C <sub>L</sub> = 100pF   |     | 4     |      | μs   |

| t <sub>S</sub> | Setting time           | 0.01%, V <sub>STEP</sub> = 10V, C <sub>L</sub> = 1000pF |     | 5.5   |      | μs   |

|                | Overload recovery time | 50% Overdrive                                           |     | 4     |      | μs   |

| POWE           | R SUPPLY               |                                                         |     |       |      |      |

| 1.             | Quiescent current (per | I <sub>O</sub> = 0V                                     |     | ±0.95 | ±1.2 | mA   |

| IQ             | amplifier)             | $I_{O} = 0V, V_{S} = \pm 5V$                            |     | ±0.92 | ±1.2 | mA   |

- Referred to output in unity-gain difference configuration.

- Includes effects of input bias and offset currents of the amplifier. (2)

- $25k\Omega$  resistors are ratio matched but have  $\pm 20\%$  absolute value. (3)

- Maximum input voltage without protection is 10V more than either  $\pm 15V$  supply ( $\pm 25V$ ). Limit  $I_{IN}$  to 1mA.

- Includes effects of input current noise of the amplifier and thermal noise contribution of resistor network.

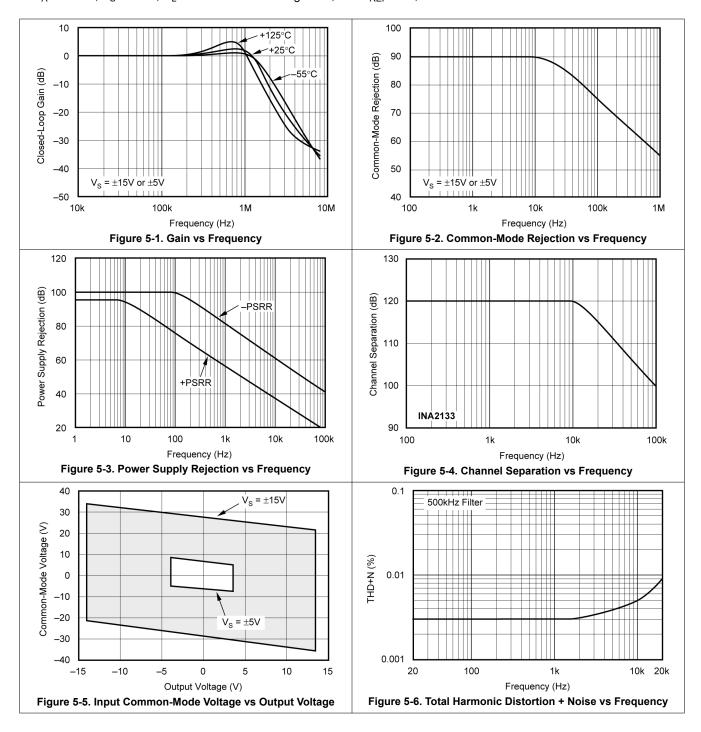

### 5.5 Typical Characteristics

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$  connected to ground, and  $V_{REF}$  = 0V, unless otherwise noted.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

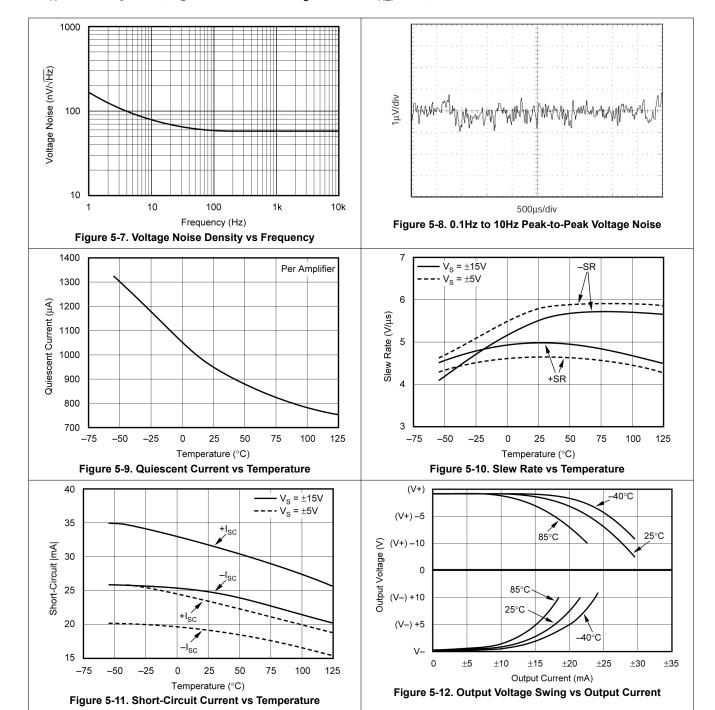

### **5.5 Typical Characteristics (continued)**

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$  connected to ground, and  $V_{REF}$  = 0V, unless otherwise noted.

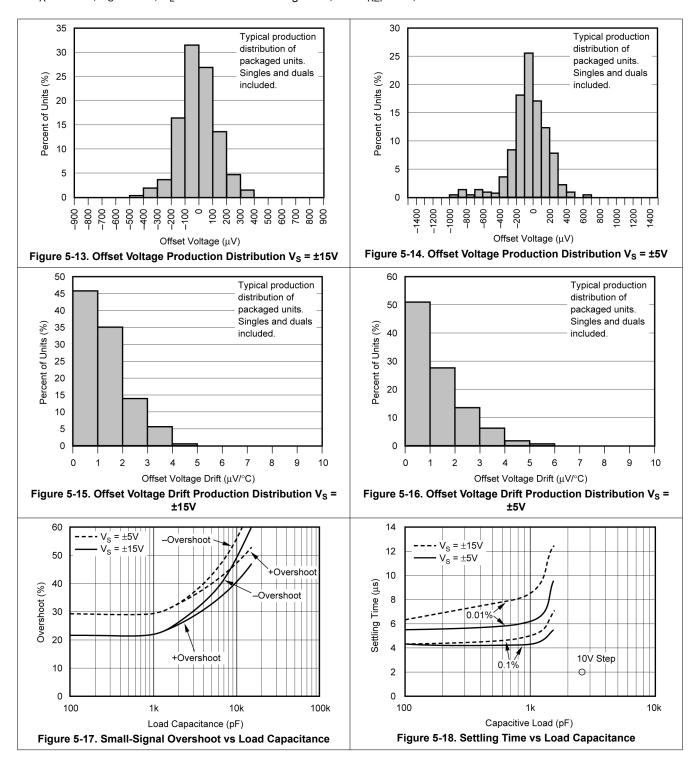

### 5.5 Typical Characteristics (continued)

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$  connected to ground, and  $V_{REF}$  = 0V, unless otherwise noted.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

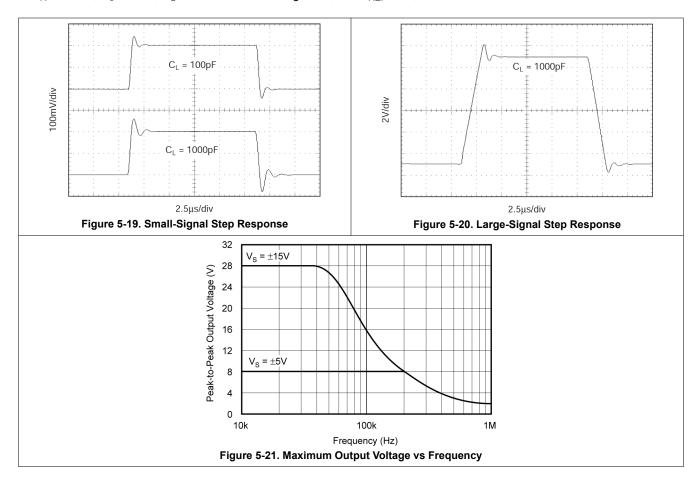

# **5.5 Typical Characteristics (continued)**

At  $T_A$  = +25°C,  $V_S$  = ±15V,  $R_L$  = 10k $\Omega$  connected to ground, and  $V_{REF}$  = 0V, unless otherwise noted.

### **6 Detailed Description**

### 6.1 Overview

The INAx133 has a high-precision operational amplifier and four trimmed, on-chip resistors. The device can be configured to make a wide variety of amplifier configurations, including difference, noninverting, and inverting configurations. The integrated, matched resistors provide an advantage over discrete implementation.

Much of the DC performance of op amp circuits depends on the accuracy of the surrounding resistors. The resistors on the INAx133 are laid out to be tightly matched. The resistors of each part are matched on-chop and tested for matching accuracy. As a result, the INAx133 provides high accuracy for specifications such as gain drift, common-mode rejection ratio, and gain error.

### 6.2 Functional Block Diagram

### **6.3 Feature Description**

#### 6.3.1 Gain Error and Drift

Gain error in the INAx133 is limited by the mismatch of the integrated precision resistors. Gain drift is limited by the slight mismatch of the temperature coefficient of integrated resistors. The integrated resistors are precision-matched with low temperature coefficient resistors to improve overall gain drift compared to the discrete implementation of differences amplifiers build when using external resistors.

Product Folder Links: INA133 INA2133

### 6.3.2 Input Voltage Range

The INAx133 difference amplifier is able to achieve a wide input common-mode voltage range by dividing down the input signal with a high-precision resistor divider. The internal resistors divide down the voltage before the voltage reaches the internal op amp and provide protection to the op amp inputs. Figure 6-1 shows an example of how the voltage division works in a difference-amplifier configuration.

Figure 6-1. Voltage Division in the Difference Amplifier Configuration

#### **6.4 Device Functional Modes**

The INAx133 has one functional mode. The device is specified on a power supply of ±15V or ±5V and can operate on a power supply from ±2.25V to ±18V with derated performance. See *Typical Characteristics*.

## 7 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 7.1 Application Information

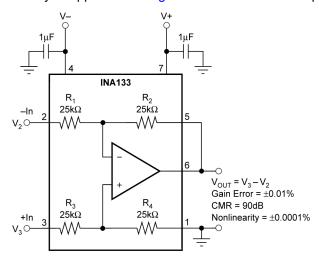

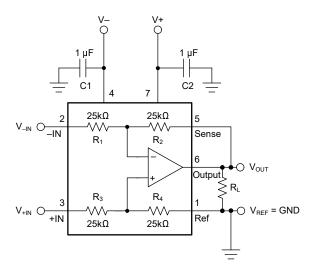

The INA133 and INA2133 are high-speed difference amplifiers are designed for a wide range of general-purpose applications. Figure 7-2 shows the basic connections required for operation of the INA133. Place decoupling capacitors close to the device pins as shown in Figure 7-2 in applications with noisy or high impedance power supplies. All circuitry is completely independent in the dual version to provide lowest crosstalk and normal behavior when one amplifier is overdriven or short-circuited.

As shown in Figure 7-2, the differential input signal is connected to pins 2 and 3. The source impedances connected to the inputs must be nearly equal to maintain good common-mode rejection. A  $5\Omega$  mismatch in source impedance degrades the common-mode rejection of a typical device to approximately 80dB (a  $10\Omega$  mismatch degrades CMR to 74dB). If the source has a known impedance mismatch, an additional resistor in series with the opposite input can be used to preserve good common-mode rejection.

The internal resistors of the INA133 are accurately ratio trimmed to match. That is,  $R_1$  is trimmed to match  $R_2$  and  $R_3$  is trimmed to match  $R_4$ . However, the absolute values may not be equal ( $R_1 + R_2$  may be slightly different than  $R_3 + R_4$ ). Thus, large series resistors on the input (greater than 250 $\Omega$ ), even if well matched, can degrade common-mode rejection.

Circuit board layout constraints can suggest possible variations in connections of the internal resistors, like that pins 1 and 3 can be interchanged. However, because of the ratio trimming technique used, CMRR can degrade. If pins 1 and 3 are interchanged, pins 2 and 5 must also be interchanged to maintain proper ratio matching.

#### 7.1.1 Operating Voltage

The INA133 and INA2133 operate from single (+4.5V to +36V) or dual (±2.25V to ±18V) supplies with excellent performance. Specifications are production tested with ±5V and ±15V supplies. Most behavior remains unchanged throughout the full operating voltage range. Parameters which vary significantly with operating voltage are shown in the *Typical Characteristics*.

### 7.1.2 Input Voltage

The INA133 and INA2133 can accurately measure differential signals that are above and below the supply rails. Linear common-mode range extends from  $2 \times (V+)-3V$  to  $2 \times (V-)+3V$  (nearly twice the supplies). See Figure 5-5.

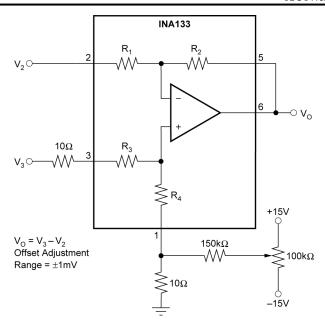

### 7.1.3 Offset Voltage Trim

The INA133 and INA2133 are laser trimmed for low offset voltage and drift. Most applications require no external offset adjustment. Figure 7-1 shows an optional circuit for trimming the output offset voltage. The output is referred to the output reference terminal (pin 1), which is normally grounded. A voltage applied to the Ref terminal is summed with the output signal. This can be used to null offset voltage as shown in Figure 7-1. To maintain good common-mode rejection, keep the source impedance of a signal applied to the Ref terminal less than  $10\Omega$ .

Product Folder Links: INA133 INA2133

Figure 7-1. Offset Adjustment

# 7.2 Typical Application

The INAx133 can be used in a variety of applications. Figure 7-2 shows one example.

Figure 7-2. Precision Difference Amplifier (Basic Power Supply and Signal Connections)

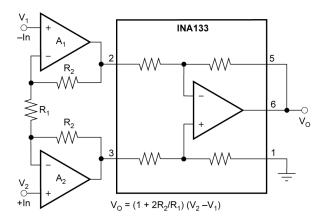

### 7.3 Additional Applications

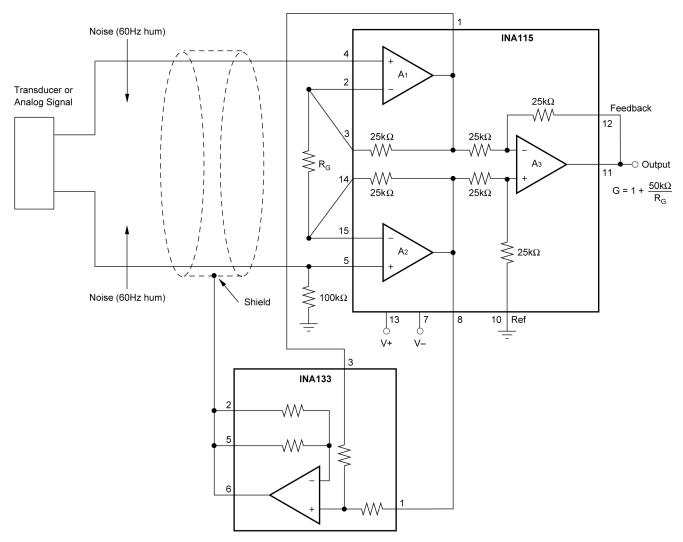

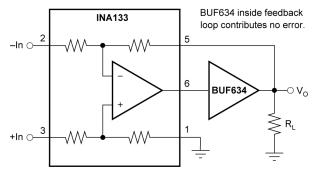

Figure 7-3. Precision Instrumentation Amplifier

NOTE: (1) Input series resistors should be less than  $250\Omega$  (1% max mismatch) to maintain excellent CMR. With  $100\Omega$  resistors, gain error is increased to 0.5%.

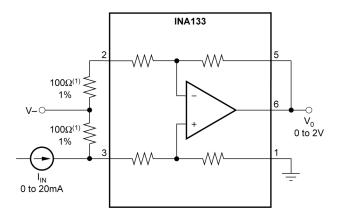

Figure 7-4. Current Receiver With Compliance to Rails

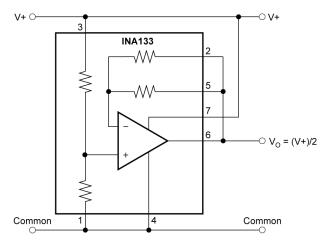

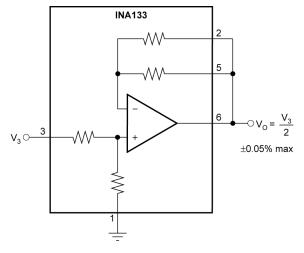

Figure 7-5. Pseudoground Generator

Product Folder Links: INA133 INA2133

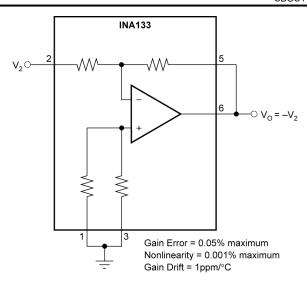

Figure 7-6. Precision Unity-Gain Inverting Amplifier

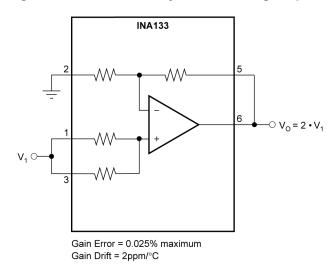

Figure 7-7. Precision Gain = 2 Amplifier

Figure 7-8. Precision Gain = 1/2 Amplifier

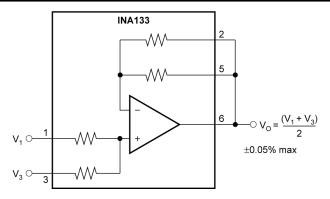

Figure 7-9. Precision Average Value Amplifier

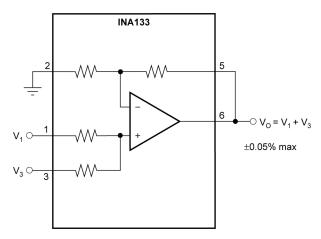

Figure 7-10. Precision Summing Amplifier

Figure 7-11. Precision Bipolar Offsetting

Product Folder Links: INA133 INA2133

Figure 7-12. Precision Summing Amplifier With Gain

Figure 7-13. Instrumentation Amplifier Guard Drive Generator

Figure 7-14. Precision Summing Instrumentation Amplifier

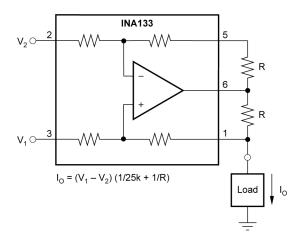

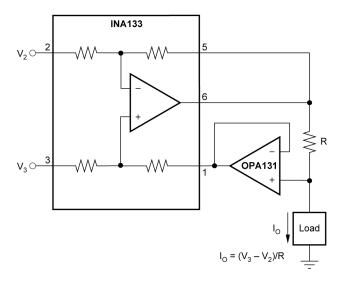

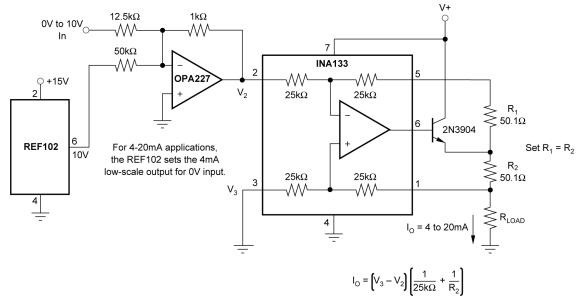

Figure 7-15. Precision Voltage-to-Current Converter With Differential Inputs

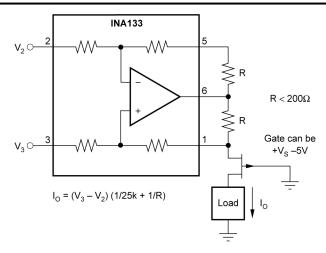

Figure 7-16. Differential Input Voltage-to-Current Converter for Low I<sub>OUT</sub>

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

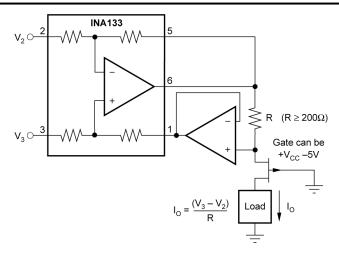

Figure 7-17. Isolating Current Source

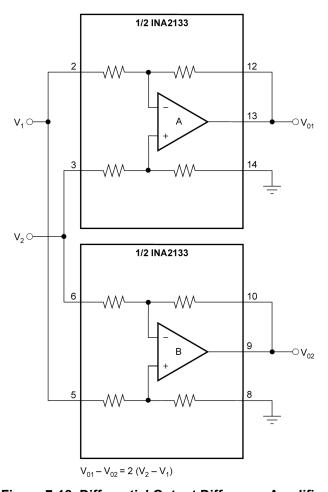

Figure 7-18. Differential Output Difference Amplifier

Figure 7-19. Isolating Current Source With Buffering Amplifier for Greater Accuracy

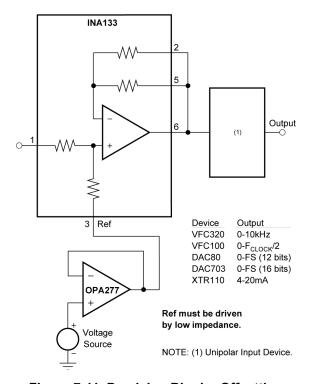

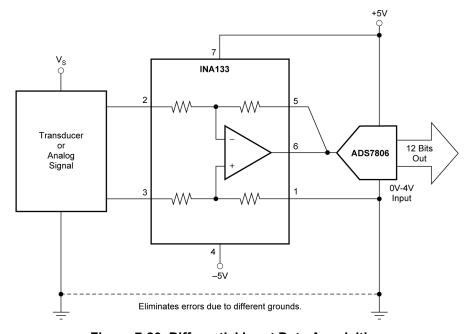

Figure 7-20. Differential Input Data Acquisition

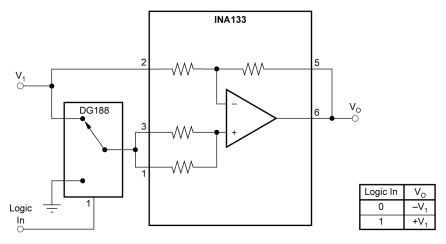

Figure 7-21. Digitally Controlled Gain of ±1 Amplifier

Submit Document Feedback

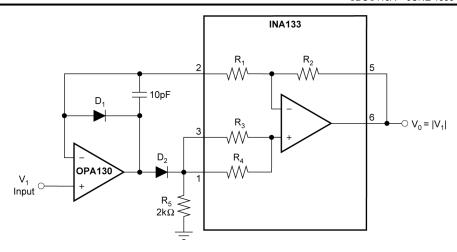

Figure 7-22. Precision Absolute Value Buffer

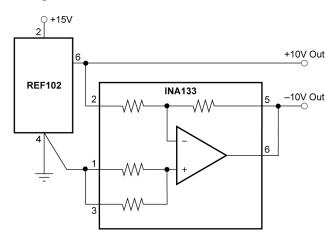

Figure 7-23. ±10V Precision Voltage Reference

Figure 7-24. High Output Current Precision Difference Amplifier

Figure 7-25. Precision Voltage-to-Current Conversion

### 7.4 Power Supply Recommendations

The nominal performance of the INA105 is specified with a supply voltage of ±15V or ±5V. The device operates using power supplies from ±2.25V to ±18V with varying performance. Parameters varying across the operating voltage and reference voltage range can be referenced in the *Typical Characteristics*.

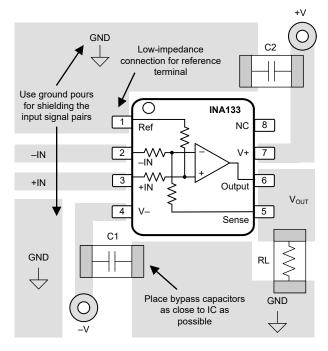

TI highly recommends to add low-ESR ceramic bypass capacitors ( $C_{BYP}$ ) between each supply pin and ground. Only one  $C_{BYP}$  is sufficient for single supply operation. Place the  $C_{BYP}$  as close to the device as possible to reduce coupling errors from noisy or high-impedance power supplies. Route the power supply trace through  $C_{BYP}$  before reaching the device power supply terminals. For more information, see *Layout Guidelines*.

#### 7.5 Layout

#### 7.5.1 Layout Guidelines

Attention to good layout practices is always recommended. For best operational performance of the device, use good PCB layout practices, including:

- Make sure that both input paths are well-matched for source impedance and capacitance to avoid converting common-mode signals into differential signals.

- Noise propagates into analog circuitry through the power pins of the circuit as a whole and of the device.

Bypass capacitors reduce the coupled noise by providing low-impedance power sources local to the analog circuitry.

- Connect low-ESR, 0.1µF ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable for singlesupply applications.

- To reduce parasitic coupling, route the input traces as far away from the supply or output traces as possible.

If these traces cannot be kept separate, crossing the sensitive trace perpendicular is preferred over crossing in parallel with the noisy trace.

- Place the external components as close to the device as possible.

- Keep the traces as short as possible.

# 7.5.2 Layout Examples

Figure 7-26. Example Schematic

Figure 7-27. Associated PCB Layout for SOIC-8 Package

### 8 Device and Documentation Support

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

### 8.1 Device Support

### 8.1.1 Development Support

For development support on this product, see the following:

### 8.1.1.1 PSpice® for TI

PSpice® for TI is a design and simulation environment that helps evaluate performance of analog circuits. Create subsystem designs and prototype solutions before committing to layout and fabrication, reducing development cost and time to market.

#### 8.1.1.2 TINA-TI™ (Free Software Download)

TINA™ is a simple, powerful, and easy-to-use circuit simulation program based on a SPICE engine. TINA-TI is a free, fully-functional version of the TINA software, preloaded with a library of macro models in addition to a range of both passive and active models. TINA-TI provides all the conventional dc, transient, and frequency domain analysis of SPICE, as well as additional design capabilities.

Available as a free download from the Analog eLab Design Center, TINA-TI offers extensive post-processing capability that allows users to format results in a variety of ways. Virtual instruments offer the ability to select input waveforms and probe circuit nodes, voltages, and waveforms, creating a dynamic quick-start tool.

#### Note

These files require that either the TINA software (from DesignSoft<sup>™</sup>) or TINA-TI software be installed. Download the free TINA-TI software from the TINA-TI folder.

### 8.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Notifications* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 8.3 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

### 8.4 Trademarks

TINA-TI<sup>™</sup> and TI E2E<sup>™</sup> are trademarks of Texas Instruments.

TINA<sup>™</sup> and DesignSoft<sup>™</sup> are trademarks of DesignSoft, Inc.

PSpice® is a registered trademark of Cadence Design Systems, Inc.

All trademarks are the property of their respective owners.

#### 8.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 8.6 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

### 9 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision \* (June 1999) to Revision A (March 2025) Page Added the Pin Configuration and Functions, Specifications, Recommended Operating Conditions, Thermal Information, Detailed Description, Overview, Functional Block Diagram, Feature Description, Device Functional Modes, Application and Implementation, Power Supply Recommendations, Layout, Layout Guidelines, Layout Example, Device and Documentation Support, and Mechanical, Packaging, and Orderable Information sections......1 Changed parameter name in Electrical Characteristics from Offset Voltage Initial vs Temperature to Offset voltage drift .......6 Changed parameter name in Electrical Characteristics from Offset Voltage Initial vs Power Supply to Power Changed parameter name in Electrical Characteristics from Offset Voltage vs Time to Long-term stability .....6 Changed parameter name in Electrical Characteristics from Current Limit, Continuous-to-Common to Shortcircuit current and added test condition......6 Moved the power supply and temperature ranges from the *Electrical Characteristics* table to the

### 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com

7-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status           | Material type | Package   Pins | Package qty   Carrier | (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)          |

|-----------------------|------------------|---------------|----------------|-----------------------|-----|-------------------------------|----------------------------|--------------|---------------------------|

| INA133U               | Last<br>Time Buy | Production    | SOIC (D)   8   | 75   TUBE             | Yes | Call TI                       | Level-3-260C-168 HR        | -40 to 85    | INA<br>133U               |

| INA133U/2K5           | Active           | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes | Call TI   Nipdau              | Level-3-260C-168 HR        | -            | INA<br>133U               |

| INA133U/2K5.A         | Active           | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes | Call TI                       | Level-3-260C-168 HR        | -40 to 85    | INA<br>133U               |

| INA133UA              | Last<br>Time Buy | Production    | SOIC (D)   8   | 75   TUBE             | Yes | Call TI                       | Level-3-260C-168 HR        | -            | INA<br>133U<br>A          |

| INA133UA/2K5          | Active           | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes | NIPDAU                        | Level-3-260C-168 HR        | -            | INA<br>(133U, 133UA)<br>A |

| INA133UA/2K5.A        | Active           | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | INA<br>(133U, 133UA)<br>A |

| INA2133U              | Active           | Production    | SOIC (D)   14  | 50   TUBE             | Yes | Call TI                       | Level-3-260C-168 HR        | -55 to 125   | INA2133U                  |

| INA2133U.A            | Active           | Production    | SOIC (D)   14  | 50   TUBE             | Yes | Call TI                       | Level-3-260C-168 HR        | -55 to 125   | INA2133U                  |

| INA2133UA             | Active           | Production    | SOIC (D)   14  | 50   TUBE             | Yes | Call TI                       | Level-3-260C-168 HR        | -55 to 125   | INA2133U<br>A             |

| INA2133UA.A           | Active           | Production    | SOIC (D)   14  | 50   TUBE             | Yes | Call TI                       | Level-3-260C-168 HR        | -55 to 125   | INA2133U<br>A             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 7-Nov-2025

(5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

(6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

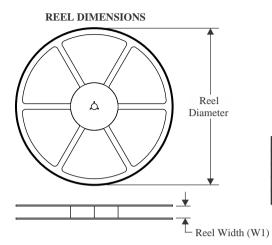

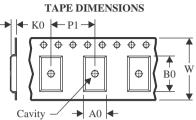

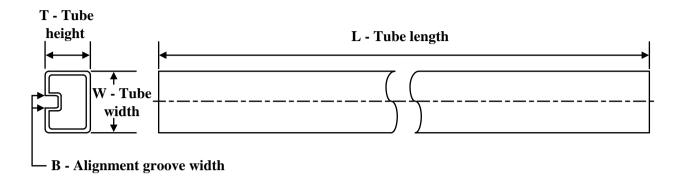

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

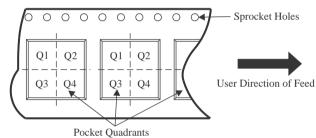

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| INA133U/2K5  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| INA133UA/2K5 | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 24-Jul-2025

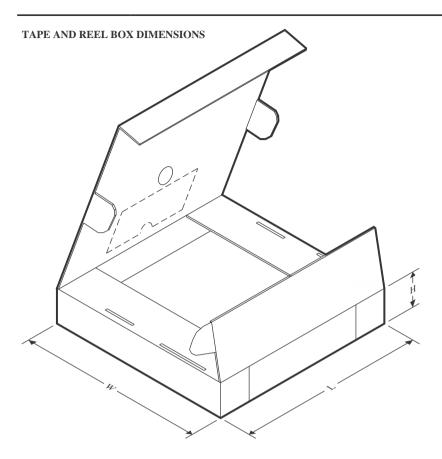

### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| INA133U/2K5  | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA133UA/2K5 | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

### **TUBE**

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| INA133U     | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| INA133UA    | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| INA2133U    | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| INA2133U.A  | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| INA2133UA   | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| INA2133UA.A | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025