# DRV816x 100V Half-Bridge Smart Gate Driver with Integrated Protection and Current **Sense Amplifier**

## 1 Features

- Drives two N-channel MOSFETs in half-bridge configuration

- High-side MOSFET source/drain up to 102V (absolute max)

- 8V (5V DRV8162L) to 20V gate drive power supply

- Integrated bootstrap diode

- **Functional Safety Quality-Managed**

- Documentation available to aid functional safety system design

- Supports 100% PWM duty cycle with an integrated trickle charge pump

- 16-level gate drive peak current

- 16mA 1000mA source current

- 32mA 2000mA sink current

- Source-sink current ratio 1:1, 1:2, 1:3

- Adjustable PWM dead time insertion 20ns 900ns

- Robust design for motor phase (SH) switching

- Slew rate 50V/ns

- Negative transient voltage -20V

- 2A strong gate pull down

- Split gate drive supply inputs for redundant shutdown (DRV8162, DRV8162L)

- Low-offset current sense amplifier (DRV8161)

- Adjustable gain (5, 10, 20, 40V/V)

- Flexible PWM control interface; 2-pin PWM, 1-pin PWM, and independent PWM mode

- 13-level VDS over current threshold

- Independent shutdown pin (nDRVOFF)

- Gate driver soft shutdown sequence

- Integrated protection features

- GVDD under voltage (GVDDUV)

- Bootstrap under voltage (BST UV)

- MOSFET over current protection (VDS)

- Shoot through protection

- Thermal shutdown (OTSD)

- Fault condition indicator (nFAULT)

- Supports 3.3V, and 5V Logic Inputs

## 2 Applications

- Industrial & collaborative robot

- Mobile robot (AGV/AMR)

- Linear motor transport systems

- Servo Drives

- E-Bikes, E-Scooters, E-Mobility

# 3 Description

The DRV816x devices are half-bridge gate drivers capable of driving high-side and low-side N-channel MOSFETs. The gate drive voltages are generated from the GVDD supply pin and the integrated bootstrap circuit is used to drive the high-side FET up to 102V drain. The Smart Gate Drive architecture supports 16-level (48 combination) gate drive peak current up to 1A source and 2A sink, and a built-in timing control of gate drive current. The devices can be used to drive various types of loads including brushless/brushed DC motors, PMSM, stepper motors, SRM, and solenoids.

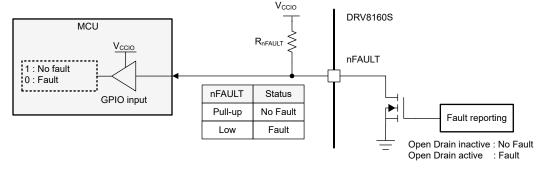

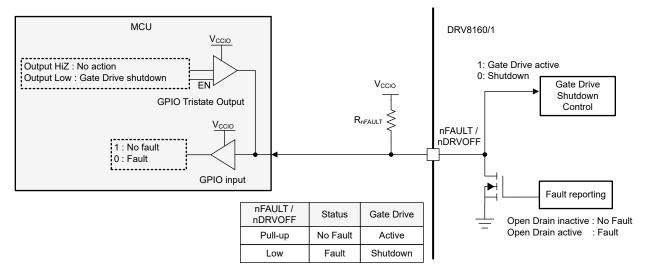

Internal protection functions are provided for supply undervoltage, FET over-current, and die over temperature. The nFAULT pin indicates fault events detected by the protection features. The nDRVOFF pin initiates power stage shutdown independent from PWM control. The DRV8162 and DRV8162L devices offer split power supply architecture to assist safe torque off (STO) function.

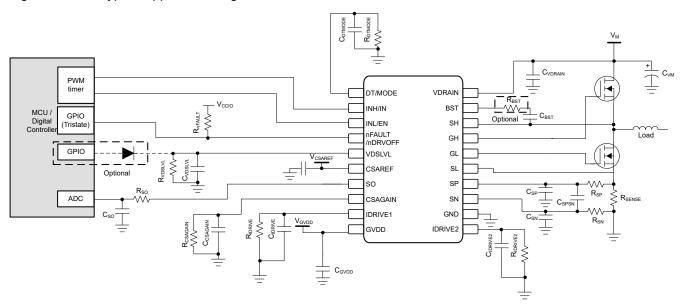

Many device parameters including gate drive current, dead time, PWM control interface, and over current detection are configurable with a few passive components connected to device pins. An integrated low-side current sense amplifier (DRV8161) provides current measurement information back to the controller.

#### **Device Information**

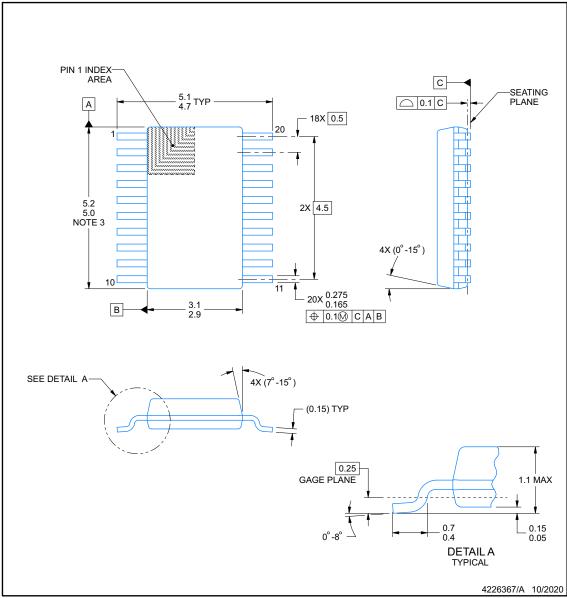

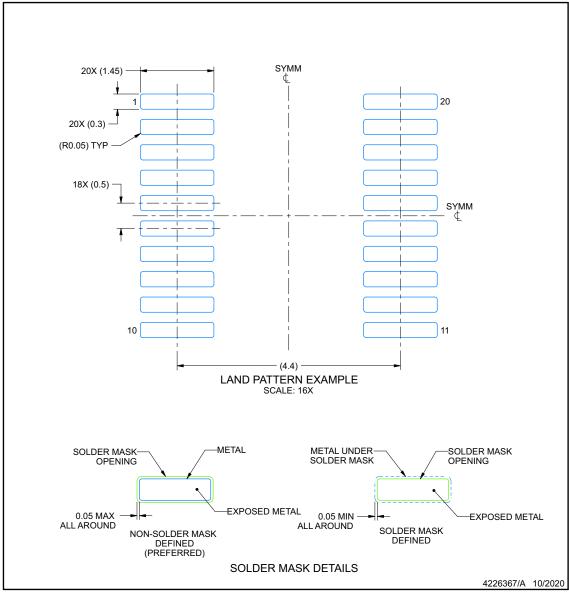

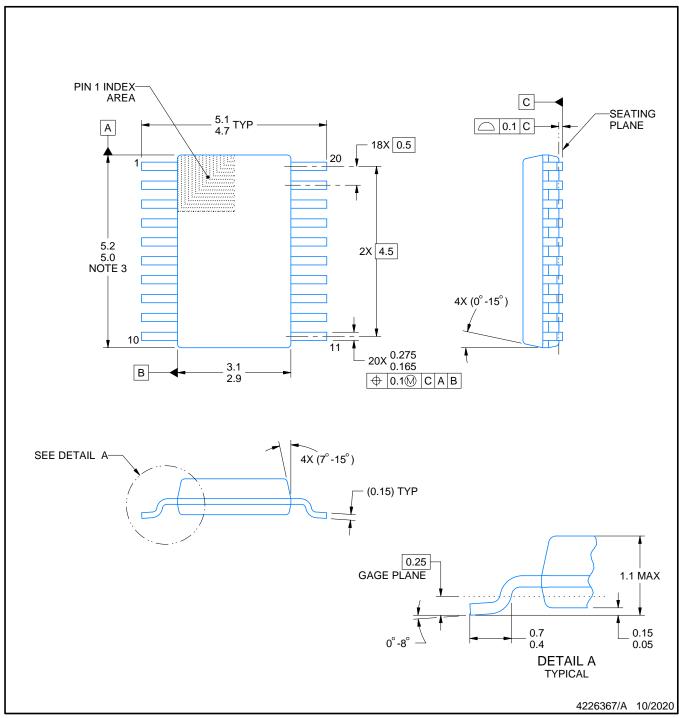

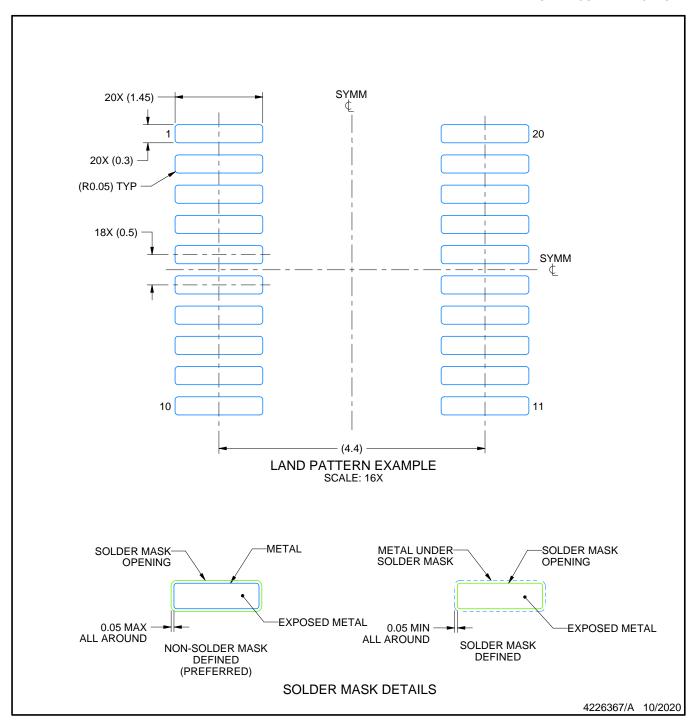

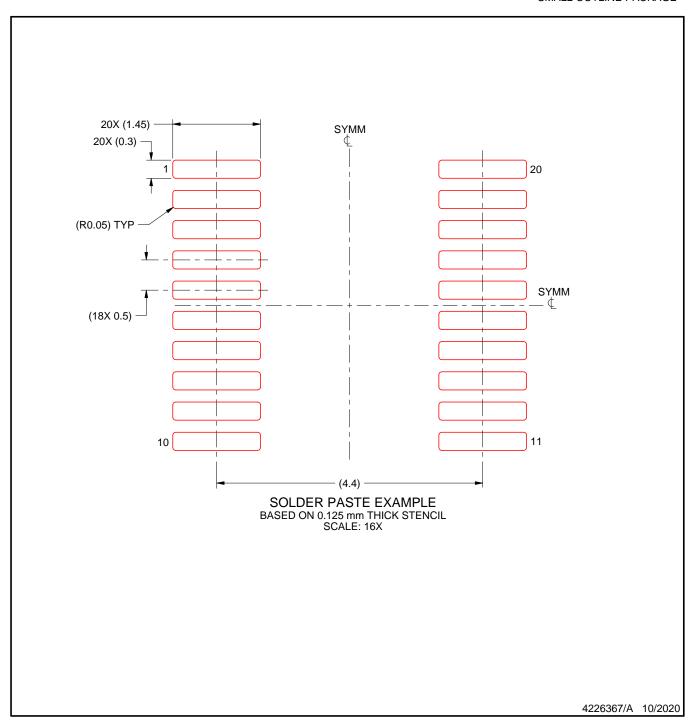

| PART<br>NUMBER         | PACKAGE <sup>(1)</sup> | PACKAGE<br>SIZE <sup>(2)</sup> | BODY SIZE<br>(NOM) |  |

|------------------------|------------------------|--------------------------------|--------------------|--|

| DRV8161                | VSSOP (20)             | 5.1mm ×<br>4.9mm               | 5.1mm ×<br>3.0mm   |  |

| DRV8162 <sup>(3)</sup> | VSSOP (20)             | 5.1mm ×<br>4.9mm               | 5.1mm ×<br>3.0mm   |  |

- For more information, see Section 11

- The package size (length × width) is a nominal value and (2) includes pins, where applicable.

- Includes DRV8162 and DRV8162L device variant. See the Device Comparison Table.

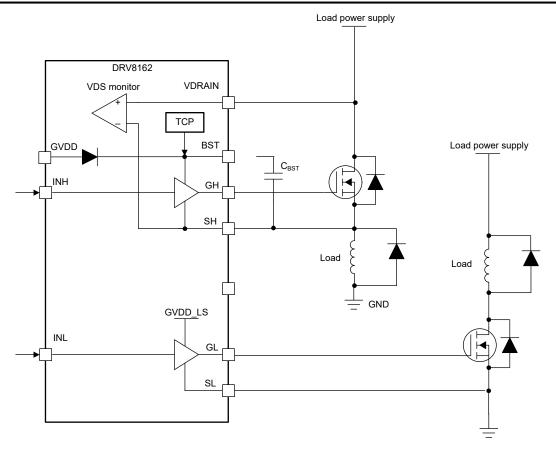

**DRV816x Simplified Schematic**

# **Table of Contents**

| 1 Features                           | 1              | 8.1 Application Information                     | 35     |

|--------------------------------------|----------------|-------------------------------------------------|--------|

| 2 Applications                       | 1              | 8.2 Typical Application                         | 35     |

| 3 Description                        | 1              | 8.3 Layout                                      | 37     |

| 4 Device Comparison Table            | 3              | 8.4 Power Supply Recommendations                |        |

| 5 Pin Configuration and Functions    | 4              | 9 Device and Documentation Support              | 40     |

| 6 Specification                      |                | 9.1 Device Support                              |        |

| 6.1 Absolute Maximum Ratings         | 6              | 9.2 Documentation Support                       | 40     |

| 6.2 ESD Ratings                      | 6              | 9.3 Receiving Notification of Documentation Upd | ates40 |

| 6.3 Recommended Operating Conditions | <mark>7</mark> | 9.4 Support Resources                           | 40     |

| 6.4 Thermal Information 1pkg         | 7              | 9.5 Trademarks                                  | 40     |

| 6.5 Electrical Characteristics       | 8              | 9.6 Electrostatic Discharge Caution             | 40     |

| 6.6 Timing Diagrams                  | 13             | 9.7 Glossary                                    | 40     |

| 7 Detailed Description               | 15             | 9.8 Community Resources                         | 40     |

| 7.1 Overview                         |                | 10 Revision History                             | 40     |

| 7.2 Functional Block Diagram         | 16             | 11 Mechanical, Packaging, and Orderable         |        |

| 7.3 Feature Description              | 18             | Information                                     | 41     |

| 8 Application and Implementation     | 35             |                                                 |        |

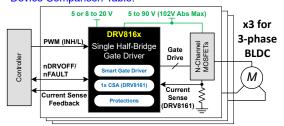

# **4 Device Comparison Table**

| DEVICE  | DEVICE<br>VARIANT | PACKAGE<br>PIN COUNT | CURRENT SENSE<br>AMPLIFIER | GATE DRIVE POWER SUPPLY | MIN GVDD<br>OPERATION | Control Mode                         |

|---------|-------------------|----------------------|----------------------------|-------------------------|-----------------------|--------------------------------------|

| DRV8161 | DRV8161           |                      | YES                        | GVDD                    | 8V                    |                                      |

| DRV8162 | DRV8162           | 20                   | No                         | GVDD and GVDD_LS        | 8V                    | 2-pin, 1-pin PWM,<br>Independent FET |

|         | DRV8162L          |                      |                            |                         | 5V                    | indopondent i E i                    |

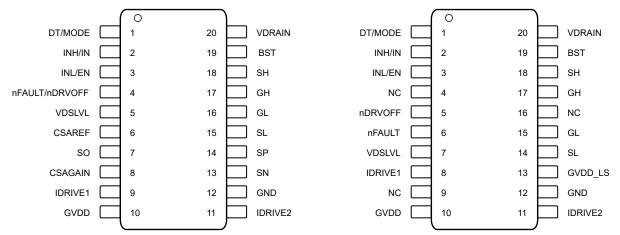

# **5 Pin Configuration and Functions**

Figure 5-1. DRV8161 DGS Package 20-pin VSSOP Top View

Figure 5-2. DRV8162 and DRV8162L DGS Package 20-pin VSSOP Top View

Table 5-1. Pin Functions—DRV816x Devices

|                    | PIN               |                                |      |                                                                                                                                                                                                                                                                                          |

|--------------------|-------------------|--------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | N                 | О.                             | _    |                                                                                                                                                                                                                                                                                          |

| NAME               | DRV8161<br>20-pin | DRV8162,<br>DRV8162L<br>20-pin | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                              |

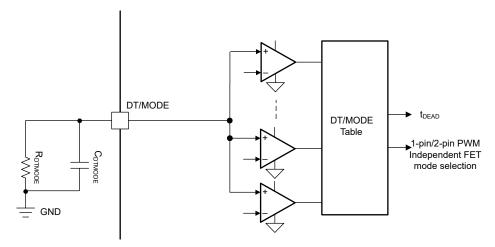

| DT/MODE            | 1                 | 1                              | ı    | Selects input pin interface logic and gate drive dead time setting. Connect a resistor between DT and GND to adjust dead time between 20ns to 900ns, and select a PWM mode.                                                                                                              |

| INH/IN             | 2                 | 2                              | I    | Gate driver control input. Gate driver control depends on DT/MODE pin setting.                                                                                                                                                                                                           |

| INL/EN             | 3                 | 3                              | I    | Gate driver control input. Gate driver control depends on DT/MODE pin setting.                                                                                                                                                                                                           |

| NC                 | _                 | 4                              | N/A  | No Connect. Leave open.                                                                                                                                                                                                                                                                  |

| nDRVOFF            | _                 | 5                              | ı    | Gate driver shutdown control. Pulling nDRVOFF low turns off high-side and low-side external MOSFETs by putting the gate drivers into the pull-down state.                                                                                                                                |

| nFAULT/<br>nDRVOFF | 4                 | _                              | I/OD | Shared fault indicator pin and gate driver shutdown pin. Connect this pin to an external pull-up resistor to the controller supply or a controller output pin. This pin is pulled logic low during a fault condition. To active gate drive shutdown, pull the pin low by external logic. |

| nFAULT             | _                 | 6                              | OD   | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor to controller I/O supply, 3.3V to 5.0V.                                                                                                                          |

| VDSLVL             | 5                 | 7                              | I    | VDS monitor threshold setting. This pin is a multilevel input pin set by an external resistor.                                                                                                                                                                                           |

| CSAREF             | 6                 | _                              | PWR  | Current sense amplifier reference. Connect a capacitor between the CSAREF and GND pins.                                                                                                                                                                                                  |

| so                 | 7                 | _                              | 0    | Current sense amplifier output.                                                                                                                                                                                                                                                          |

| CSAGAIN            | 8                 | _                              | ı    | Gain settings for current sense amplifier. This pin is a multilevel input pin set by an external resistor.                                                                                                                                                                               |

| IDRIVE1            | 9                 | 8                              | I    | Gate drive source and sink current setting. This pin is a multilevel input pin set by an external resistor.                                                                                                                                                                              |

| NC                 |                   | 9, 16                          |      | No Connect. Leave open.                                                                                                                                                                                                                                                                  |

| GVDD               | 10                | 10                             | PWR  | Gate driver power supply input. Connect a capacitor between the GVDD and GND pins.                                                                                                                                                                                                       |

| IDRIVE2            | 11                | 11                             | I    | Gate drive source and sink current setting. This pin is a multilevel input pin set by an external resistor.                                                                                                                                                                              |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

# Table 5-1. Pin Functions—DRV816x Devices (continued)

|         | PIN               |                                |      |                                                                                                                                                                 |

|---------|-------------------|--------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | N                 | NO.                            |      |                                                                                                                                                                 |

| NAME    | DRV8161<br>20-pin | DRV8162,<br>DRV8162L<br>20-pin | TYPE | DESCRIPTION                                                                                                                                                     |

| GND     | 12                | 12                             | PWR  | Device ground.                                                                                                                                                  |

| GVDD_LS | _                 | 13                             | PWR  | Low-side gate driver power supply input (DRV8162 and DRV8162L only). Connect a capacitor between the GVDD_LS and GND pins.                                      |

| SN      | 13                | _                              | I    | Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                           |

| SP      | 14                | _                              | I    | Current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                         |

| SL      | 15                | 14                             | I    | Low-side source pin. Connect to the low-side power MOSFET source. This pin is an input for the VDS monitor and the output for the low-side gate driver sink.    |

| GL      | 16                | 15                             | 0    | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                  |

| GH      | 17                | 17                             | 0    | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                |

| SH      | 18                | 18                             | I    | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink. |

| BST     | 19                | 19                             | 0    | Bootstrap output pin. Connect a capacitor between BST and SH.                                                                                                   |

| VDRAIN  | 20                | 20                             | PWR  | High-side MOSFET drain sense input for VDS monitor and charge pump reference. Connect to the high-side MOSFET drain.                                            |

PWR = power, I = input, O = output, NC = no connection, OD = open-drain output

# **6 Specification**

# 6.1 Absolute Maximum Ratings

Over recommended operating conditions (unless otherwise noted)(1)

|                                                      | ·                                        | MIN  | MAX                       | UNIT |

|------------------------------------------------------|------------------------------------------|------|---------------------------|------|

| Gate driver regulator pin voltage                    | GVDD, GVDD_LS                            | -0.3 | 20                        | V    |

| High-side drain pin voltage                          | VDRAIN, T <sub>J</sub> = 25°C            | -0.3 | 102                       | V    |

| Bootstrap pin voltage                                | BST, T <sub>J</sub> = 25°C               | -0.3 | 115                       | V    |

| Bootstrap pin voltage                                | BST with respect to SH                   | -0.3 | 20                        | V    |

|                                                      | nFAULT                                   | -0.3 | 20                        |      |

| Logic pin voltage                                    | INH(IN), INL(EN), nDRVOFF, VDSLVL        | -0.3 | 20                        | V    |

|                                                      | DT/MODE, IDRIVE1, IDRIVE2,<br>CSAGAIN    | -0.3 | 6                         | •    |

| High-side gate drive pin voltage                     | GH, T <sub>J</sub> = 25°C<br>GVDD >= 11V | -5   | 115                       | V    |

| High-side gate drive pin voltage                     | GH with respect to SH                    | -0.3 | 20                        | V    |

| High-side source pin voltage                         | SH, DC                                   | -5   | 105                       | V    |

| Transient high-side source pin negative voltage      | SH, 1 µs                                 | -20  |                           | V    |

| High-side source pin slew rate                       | SH , V <sub>BST-SH</sub> >3.5V           |      | 50                        | V/ns |

| Low-side gate drive pin voltage                      | GL with respect to SL                    | -0.3 | 20                        | V    |

| Low-side source sense pin voltage                    | SL                                       | -5   | V <sub>GVDD</sub> +0.3    | V    |

| Transient low-side source sense pin negative voltage | SL, 1 µs                                 | -16  |                           | V    |

| Current sense amplifier reference input pin voltage  | CSAREF                                   | -0.3 | 5.5                       | V    |

| Shunt amplifier input pin voltage                    | SN, SP                                   | -1   | 1                         | V    |

| Transient 500-ns shunt amplifier input pin voltage   | SN, SP, 500ns                            | -16  | 20                        | V    |

| Shunt amplifier output pin voltage                   | so                                       | -0.3 | V <sub>CSAREF</sub> + 0.3 | V    |

| Junction temperature, T <sub>J</sub>                 |                                          | -40  | 150                       | °C   |

| Storage temperature, T <sub>stg</sub>                |                                          | -65  | 150                       | °C   |

<sup>1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime

## 6.2 ESD Ratings

|                    |               |                                                                       | VALUE | UNIT |

|--------------------|---------------|-----------------------------------------------------------------------|-------|------|

| ./                 | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating temperature range (unless otherwise noted)

|                      |                                                         |                                                                                                                                                                                                                                                           | MIN | NOM | MAX | UNIT |

|----------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                      | Power supply voltage                                    | GVDD, GVDD_LS                                                                                                                                                                                                                                             | 8   |     |     | V    |

| $V_{GVDD}$           | Power supply voltage (DRV8162L only)                    | GVDD, GVDD_LS, DRV8162L device variant                                                                                                                                                                                                                    | 5   |     |     | V    |

| V <sub>GVDD-SL</sub> | Power supply voltage with respect to SL                 | GVDD(DRV8161), GVDD_LS<br>(DRV8162x) for low-side Pre-Driver<br>PWM operation                                                                                                                                                                             | 3.5 |     |     | V    |

| V <sub>VDRAIN</sub>  | High-side drain pin voltage                             | VDRAIN, low-side gate drive, and high-<br>side gate drive switching with bootstrap                                                                                                                                                                        | 0   |     | 90  | V    |

| V <sub>BST-SH</sub>  | Bootstrap pin voltage with respect to SH                | $\begin{aligned} & \text{BST (V}_{\text{BST}}\text{-}\text{V}_{\text{SH}})\text{, high-side gate drive} \\ & \text{switching and no BST\_UV detection,} \\ & \text{V}_{\text{BST-SH}}\text{ min > V}_{\text{BST\_UV}}\text{ max (rising),} \end{aligned}$ | 6.1 |     |     | V    |

|                      | Bootstrap pin voltage with respect to SH (DRV8162Lonly) | BST (V <sub>BST</sub> - V <sub>SH</sub> ), DRV8162L<br>device variant only, high-side gate<br>drive switching and no BST_UV<br>detection, V <sub>BST-SH</sub> min > V <sub>BST_UV</sub> max<br>(rising)                                                   | 4.6 |     | 20  | V    |

| V <sub>BST</sub>     | Bootstrap pin voltage                                   | BST                                                                                                                                                                                                                                                       | 0   |     | 105 | V    |

| V <sub>SH</sub>      | High-side source pin voltage                            | SH                                                                                                                                                                                                                                                        | -2  |     | 95  | V    |

| V <sub>I</sub>       | Digital / Pin detection input voltage                   | INH, INL, IDRIVE1, IDRIVE2, CSAGAIN, VDSLVL, nDRVOFF, DT/MODE                                                                                                                                                                                             | 0   |     | 5.5 | V    |

| V <sub>OD</sub>      | Open drain pullup voltage                               | nFAULT                                                                                                                                                                                                                                                    |     |     | 5.5 | V    |

| I <sub>OD</sub>      | Open drain output current                               | nFAULT                                                                                                                                                                                                                                                    |     |     | -5  | mA   |

| V <sub>CSAREF</sub>  | Current sense amplifier reference voltage               | CSAREF                                                                                                                                                                                                                                                    | 3.0 |     | 5.5 | V    |

| T <sub>A</sub>       | Operating ambient temperature                           |                                                                                                                                                                                                                                                           |     |     | 125 | °C   |

| TJ                   | Operating junction temperature                          |                                                                                                                                                                                                                                                           | -40 |     | 150 | °C   |

# 6.4 Thermal Information 1pkg

|                       |                                              | DRV8161/DRV8162 |      |

|-----------------------|----------------------------------------------|-----------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP)     | UNIT |

|                       |                                              | 20 PINS         |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 87.0            | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 31.2            | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 42.3            | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.9             | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 41.9            | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | N/A             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

V<sub>GVDD</sub> = 12 V V<sub>VDRAIN</sub> = 48 V T<sub>J</sub> = 25°C (unless otherwise noted)

|                               | PARAMETER                                                                     | TEST CONDITIONS                                                                                                         | MIN | TYP   | MAX  | UNIT |

|-------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------|

| POWER SUI                     | PPLIES (GVDD, BST)                                                            |                                                                                                                         |     |       |      |      |

| I <sub>VDRAIN_UNP</sub><br>WR | VDRAIN leakage current under GVDD unpowered                                   | GVDD = 0V, VDRAIN = 48V, V <sub>BST-SH</sub> = 0V<br>Leakage current of VDRAIN + SH                                     |     | 3.5   | 5    | μΑ   |

| I <sub>GVDD</sub>             | GVDD active mode current                                                      | INH = INL = Switching @ 20kHz; V <sub>BST</sub> = V <sub>GVDD</sub> ; NO FETs connected, DT/MODE Pin open. VDS_LVL = 2V |     | 2     |      | mA   |

| t <sub>WAKE</sub>             | Turnon time                                                                   | GVDD = 0V to 12V<br>GVDD_UV to active mode (outputs<br>ready) (nFAULT = High)                                           |     | 0.4   |      | ms   |

| IL <sub>BS_TCPON</sub>        | Bootstrap pin leakage current during high-side pull-up                        | INH = high; TCP_ON                                                                                                      |     | 30    |      | μΑ   |

| LOGIC-LEVI                    | EL INPUTS (INH, INL, nDRVOFF)                                                 |                                                                                                                         |     |       |      |      |

| V <sub>IL</sub>               | Input logic low voltage                                                       | INL, INH, nDRVOFF                                                                                                       |     |       | 0.8  | V    |

| V <sub>IH</sub>               | Input logic high voltage                                                      | INL, INH, nDRVOFF                                                                                                       | 2.2 |       |      | V    |

| R <sub>PU</sub>               | Input pullup resistance                                                       | nDRVOFF to internal regulator, no external connection                                                                   |     | 250   |      | kΩ   |

| R <sub>PD</sub>               | Input pulldown resistance                                                     | INH, INL to GND                                                                                                         |     | 250   |      | kΩ   |

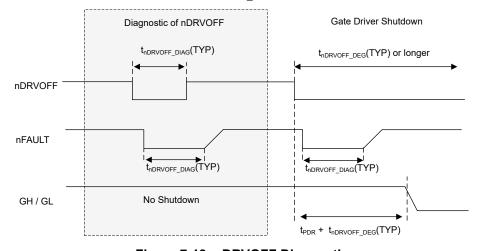

| t <sub>nDRVOFF_DE</sub>       | nDRVOFF input deglitch time                                                   | DRVOFF falling and rising                                                                                               | 1   | 2.1   | 4.2  | μs   |

| t <sub>nDRVOFF_DIA</sub>      | nDRVOFF diagnostic pulse valid input time                                     | DRV8162 and DRV8162L only                                                                                               |     | 0.5   |      | μs   |

| OPEN-DRAI                     | N OUTPUT (nFAULT)                                                             |                                                                                                                         |     |       |      |      |

| V <sub>OL</sub>               | Output logic low voltage                                                      | I <sub>OD</sub> = 5 mA, GVDD > 4V                                                                                       |     |       | 0.4  | V    |

| BOOTSTRA                      | P DIODE (BST)                                                                 |                                                                                                                         |     |       |      |      |

| V <sub>BOOTD</sub>            | Bootstrap diode forward voltage                                               | I <sub>BOOT</sub> = 100 μA                                                                                              |     |       | 0.82 | V    |

| V <sub>BOOTD</sub>            | Bootstrap diode forward voltage                                               | I <sub>BOOT</sub> = 100 mA                                                                                              |     |       | 1.6  | V    |

| R <sub>BOOTD</sub>            | Bootstrap dynamic resistance $(\Delta V_{BOOTD}/\Delta I_{BOOT})$             | I <sub>BOOT</sub> = 100 mA and 50 mA                                                                                    | 3.9 | 4.8   | 9    | Ω    |

| CHARGE PU                     | JMP (BST)                                                                     |                                                                                                                         |     |       |      |      |

| V <sub>TCP</sub>              | Trickle charge pump output voltage                                            | V <sub>BST-SH</sub> , INH = High, SH = VDRAIN<br>= 20V, BST > GVDD, External load<br>I <sub>TRICKLE</sub> = 2uA         | 9.5 | 10.6  | 12   | V    |

| t <sub>TCP_DLY</sub>          | Trickle charge pump active delay time                                         | INL = Low                                                                                                               | 150 | 250   | 350  | μs   |

| GATE DRIVE                    | ERS (GH, GL, SH, SL)                                                          |                                                                                                                         |     |       | '    |      |

| V <sub>GSHx_LO</sub>          | High-side gate drive low level voltage (V <sub>GH</sub> - V <sub>SH</sub> )   | I <sub>GHx</sub> = -10 mA; V <sub>GVDD</sub> = 12V; IDRIVE = 1000mA, No FETs connected                                  | 0   | 0.022 | 0.2  | V    |

| V <sub>GSHx_HI</sub>          | High-side gate drive high level voltage (V <sub>BST</sub> - V <sub>GH</sub> ) | I <sub>GHx</sub> = 10 mA; V <sub>GVDD</sub> = 12V; IDRIVE = 500mA, No FETs connected                                    | 0   | 0.09  | 0.2  | V    |

| V <sub>GSLx_LO</sub>          | Low-side gate drive low level voltage (V <sub>GL</sub> - V <sub>SL</sub> )    | I <sub>GLx</sub> = -10 mA; V <sub>GVDD</sub> = 12V; IDRIVE = 1000mA, No FETs connected                                  | 0   | 0.022 | 0.2  | V    |

| V <sub>GSLx_HI</sub>          | Low-side gate drive high level voltage (V <sub>GVDD</sub> - V <sub>GL</sub> ) | I <sub>GLx</sub> = 10 mA; V <sub>GVDD</sub> = 12V; IDRIVE = 500mA, No FETs connected                                    | 0   | 0.09  | 0.2  | V    |

$V_{GVDD} = 12 \text{ V } V_{VDRAIN} = 48 \text{ V } T_1 = 25^{\circ}\text{C}$  (unless otherwise noted)

|                       | PARAMETER                | TEST CONDITIONS                                                         | MIN | TYP  | MAX  | UNIT |

|-----------------------|--------------------------|-------------------------------------------------------------------------|-----|------|------|------|

| I <sub>DRIVEP0</sub>  |                          | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C         | 9   | 16   | 26   | mA   |

| I <sub>DRIVEP1</sub>  |                          | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C       | 19  | 32   | 52   | mA   |

| I <sub>DRIVEP2</sub>  |                          | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C         | 38  | 64   | 103  | mA   |

| I <sub>DRIVEP3</sub>  |                          | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C         | 57  | 96   | 154  | mA   |

| I <sub>DRIVEP4</sub>  |                          | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C       | 76  | 128  | 205  | mA   |

| I <sub>DRIVEP5</sub>  |                          | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C       | 96  | 160  | 256  | mA   |

| I <sub>DRIVEP6</sub>  |                          | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C         | 115 | 192  | 308  | mA   |

| I <sub>DRIVEP7</sub>  | Dock course gets surrent | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C         | 134 | 224  | 359  | mA   |

| I <sub>DRIVEP8</sub>  | Peak source gate current | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C         | 153 | 256  | 410  | mA   |

| I <sub>DRIVEP9</sub>  |                          | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C       | 172 | 288  | 461  | mA   |

| I <sub>DRIVEP10</sub> |                          | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C       | 192 | 320  | 512  | mA   |

| I <sub>DRIVEP11</sub> |                          | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C         | 230 | 384  | 615  | mA   |

| I <sub>DRIVEP12</sub> | -                        | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C       | 268 | 448  | 717  | mA   |

| DRIVEP13              |                          | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C       | 307 | 512  | 820  | mA   |

| DRIVEP14              |                          | $V_{BST}-V_{SH} = V_{GVDD} = 12V, T_{J} = -40^{\circ}C$ to 150°C        | 460 | 768  | 1229 | mA   |

| DRIVEP15              |                          | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40^{\circ}C$ to 150°C | 614 | 1024 | 1639 | mA   |

V<sub>GVDD</sub> = 12 V V<sub>VDRAIN</sub> = 48 V T<sub>J</sub> = 25°C (unless otherwise noted)

|                               | 2 V V <sub>VDRAIN</sub> = 48 V T <sub>J</sub> = 25°C (unless<br>PARAMETER | TEST CONDITIONS                                                                                         | MIN  | TYP                                     | MAX  | UNIT |

|-------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-----------------------------------------|------|------|

| I <sub>DRIVEN0</sub>          |                                                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_{J}$ = -40°C to 150°C                                       | 19   | 32                                      | 52   | mA   |

| I <sub>DRIVEN1</sub>          |                                                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C                                       | 38   | 64                                      | 103  | mA   |

| I <sub>DRIVEN2</sub>          |                                                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 76   | 128                                     | 205  | mA   |

| I <sub>DRIVEN3</sub>          |                                                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 115  | 192                                     | 308  | mA   |

| I <sub>DRIVEN4</sub>          |                                                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 153  | 256                                     | 410  | mA   |

| I <sub>DRIVEN5</sub>          |                                                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 192  | 320                                     | 512  | mA   |

| I <sub>DRIVEN6</sub>          |                                                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 230  | 384                                     | 615  | mA   |

| I <sub>DRIVEN7</sub>          | Peak sink gate current                                                    | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 268  | 448                                     | 717  | mA   |

| I <sub>DRIVEN8</sub>          | eak sink gate current                                                     | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 307  | 512                                     | 820  | mA   |

| I <sub>DRIVEN9</sub>          |                                                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C                                       | 345  | 576                                     | 922  | mA   |

| I <sub>DRIVEN10</sub>         |                                                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C                                       | 384  | 640                                     | 1024 | mA   |

| I <sub>DRIVEN11</sub>         |                                                                           | $V_{BST}$ - $V_{SH}$ = $V_{GVDD}$ = 12V, $T_J$ = -40°C to 150°C                                         | 460  | 768                                     | 1229 | mA   |

| I <sub>DRIVEN12</sub>         |                                                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C                                       | 537  | 896                                     | 1434 | mA   |

| I <sub>DRIVEN13</sub>         |                                                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C                                       | 614  | 1024                                    | 1639 | mA   |

| I <sub>DRIVEN14</sub>         |                                                                           | $V_{BST}-V_{SH} = V_{GVDD} = 12V, T_{J} = -40^{\circ}C \text{ to}$<br>150°C                             | 921  | 1536                                    | 2458 | mA   |

| I <sub>DRIVEN15</sub>         |                                                                           | $V_{BST}$ - $V_{SH} = V_{GVDD} = 12V$ , $T_{J} = -40$ °C to 150°C                                       | 1228 | 2048                                    | 3277 | mA   |

| R <sub>PD_LS</sub>            | Low-side passive pull down                                                | GL to SL, V <sub>GL</sub> - V <sub>SL</sub> = 2V                                                        | 60   | 85                                      | 120  | kΩ   |

| R <sub>PDSA_HS</sub>          | High-side semiactive pull down                                            | $V_{GVDD} < V_{GVDD\_UV}$<br>GH to SH, $V_{GH} - V_{SH} = 2V$                                           | 2    | 4                                       | 8    | kΩ   |

| I <sub>PUHOLD_HS</sub>        | High-side pull-up hold current                                            | T <sub>J</sub> = -40°C to 150°C                                                                         | 307  | 512                                     | 820  | mA   |

| I <sub>PDHOLD</sub> HS        | High-side pull-down hold current                                          | T <sub>J</sub> = -40°C to 150°C                                                                         | 1228 | 2048                                    | 3277 | mA   |

| I <sub>PDSTRONG_L</sub><br>s  | Low-side pull-down strong current                                         | T <sub>J</sub> = -40°C to 150°C                                                                         | 1228 | 2048                                    | 3277 | mA   |

| I <sub>PDSTRONG_H</sub><br>s  | High-side pull-down strong current                                        | T <sub>J</sub> = -40°C to 150°C                                                                         | 1228 | 2048                                    | 3277 | mA   |

| I <sub>DRVIVENSD_L</sub><br>s | Low-side peak sink gate shutdown current                                  | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN13</sub> (1024mA Typ) or smaller settings                   |      | 32                                      |      | mA   |

| I <sub>DRVIVENSD_L</sub>      | Low-side peak sink gate shutdown current                                  | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN14</sub> (1536mA Typ) or I <sub>DRIVEN15</sub> (2048mA Typ) |      | 64                                      |      | mA   |

| I <sub>DRIVENSD_H</sub>       | High-side peak sink gate shutdown current                                 | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN13</sub> (1024mA Typ) or smaller settings                   |      | 32                                      |      | mA   |

| I <sub>DRIVENSD_H</sub>       | High-side peak sink gate shutdown current                                 | I <sub>DRIVENx</sub> is set to I <sub>DRIVEN14</sub> (1536mA Typ) or I <sub>DRIVEN15</sub> (2048mA Typ) |      | 64                                      |      | mA   |

| GATE DRIVE                    | ERS TIMINGS                                                               |                                                                                                         |      |                                         |      |      |

| t <sub>PDR_LS</sub>           | Low-side rising propagation delay                                         | INL to GL rising, V <sub>GVDD</sub> > 8V                                                                | 25   | 40                                      | 80   | ns   |

| t <sub>PDF LS</sub>           | Low-side falling propagation delay                                        | INL to GL falling, V <sub>GVDD</sub> > 8V                                                               | 25   | 41                                      | 80   | ns   |

| י טו _נט                      |                                                                           |                                                                                                         |      | • • • • • • • • • • • • • • • • • • • • |      |      |

$V_{GVDD} = 12 \text{ V } V_{VDRAIN} = 48 \text{ V } T_1 = 25^{\circ}\text{C}$  (unless otherwise noted)

|                                  | PARAMETER                                                                                      | TEST CONDITIONS                                                                                                                                                                                                | MIN    | TYP | MAX                           | UNIT   |

|----------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------------------------|--------|

| t <sub>PDR_HS</sub>              | High-side rising propagation delay                                                             | INH to GH rising, $V_{GVDD} = V_{BST} - V_{SH} > 8V$                                                                                                                                                           | 25     | 41  | 80                            | ns     |

| t <sub>PDF_HS</sub>              | High-side falling propagation delay                                                            | INH to GH falling, $V_{GVDD} = V_{BST} - V_{SH} > 8V$                                                                                                                                                          | 25     | 42  | 80                            | ns     |

| t <sub>PD_MATCH</sub>            | Matching propagation delay of low-side gate driver                                             | GL turning ON to GL turning OFF,<br>From $V_{GL-SL}$ = 1V to $V_{GL-SL}$ = $V_{GVDD}$ - 1V; $V_{GVDD}$ = $V_{BST}$ - $V_{SH}$ > 8V; $V_{SH}$ = 0V to 90V, no load on GH and GL                                 | -10    | ±4  | 10                            | ns     |

| PD_MATCH                         | Matching propagation delay of high-side gate driver                                            | GH turning ON to GH turning OFF, From $V_{GH-SH} = 1V$ to $V_{GH-SH} = V_{BST-SH} - 1V$ ; $V_{GVDD} = V_{BST} - V_{SH} > 8V$ ; $V_{SH} = 0V$ to 90V, no load on GH and GL                                      | -10    | ±4  | 10                            | ns     |

| <sup>t</sup> PD_MATCH_P          | Matching propagation delay per phase                                                           | Deadtime disabled. GL turning OFF to GH turning ON, From $V_{GL-SL} = V_{GVDD} - 1V$ to $V_{GH-SH} = 1V$ ; $V_{GVDD} = V_{BST} - V_{SH} > 8V$ ; $V_{SH} = 0V$ to 90V, no load on GH and GL, dead time disabled | -12    | ±4  | 12                            | ns     |

| н                                | matering propagation delay per priase                                                          | Deadtime disabled. GH turning OFF to GL turning ON, From $V_{GH-SH} = V_{BST-SH} - 1V$ to $V_{GL-SL} = 1V$ ; $V_{GVDD} = V_{BST} - V_{SH} > 8V$ ; $V_{SH} = 0V$ to 90V, no load on GH and GL                   | -10    | ±4  | 10                            | ns     |

| t <sub>DEAD</sub>                | Gate drive dead time                                                                           | $R_{DT}$ = 470 $\Omega$ 2-pin PWM mode;                                                                                                                                                                        |        | 20  |                               | ns     |

| t <sub>DEAD</sub>                | Gate drive dead time                                                                           | $R_{DT}$ = 1.3 K $\Omega$ 2-pin PWM mode;                                                                                                                                                                      | 97     | 100 | 120                           | ns     |

| t <sub>DEAD</sub>                | Gate drive dead time                                                                           | $R_{DT} = 3.3 \text{ K}\Omega$ 2-pin PWM mode;                                                                                                                                                                 | 316    | 370 | 422                           | ns     |

| t <sub>DEAD_CFG</sub>            | Gate drive dead time configuration range                                                       | Tdead linear setting $R_{DT}$ = 10 K $\Omega$ - 1 M $\Omega$ , 1-pin PWM mode                                                                                                                                  | 20     |     | 900                           | ns     |

| t <sub>DEAD</sub>                | Gate drive dead time                                                                           | $R_{DT}$ = 990 K $\Omega$ 1-pin PWM mode; $T_{J}$ = -40°C to 150°C                                                                                                                                             | 700    | 900 | 1250                          | ns     |

| t <sub>MINDEAD_</sub> VG<br>s_HS | Minimum gate drive dead time (shortest available) of VGS monitor mode; HS falling to LS rising | VGS monitor dead time insertion mode. $t_{DEAD\_CFG} < 130$ ns, $V_{GVDD} > 8V$ , $V_{BST-SH} > 8V$ , $0V < V_{SH} = <90V$                                                                                     |        | 215 |                               | ns     |

| t <sub>MINDEAD_</sub> VG<br>s_LS | Minimum gate drive dead time (shortest available) of VGS monitor mode; LS falling to HS rising | VGS monitor dead time insertion;<br>t <sub>DEAD_CFG</sub> < 130ns, V <sub>GVDD</sub> > 8V, V <sub>BST-SH</sub><br>> 8V; 0V < V <sub>SH</sub> = <90V                                                            |        | 225 |                               | ns     |

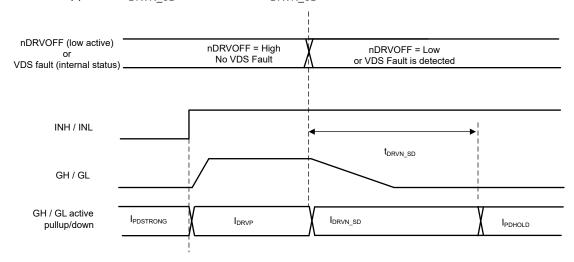

| t <sub>DRVN_SD</sub>             | Gate driver pulldown timing during shutdown                                                    |                                                                                                                                                                                                                |        | 20  |                               | μs     |

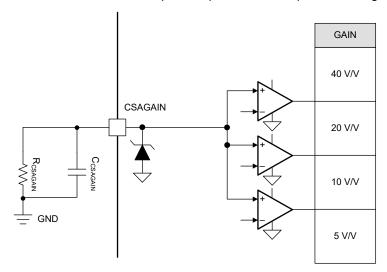

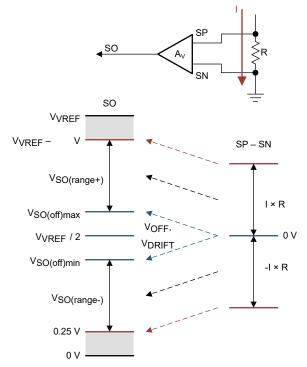

| CURRENT S                        | HUNT AMPLIFIERS (SN, SO, SP, CSARE                                                             | <b>=F</b> )                                                                                                                                                                                                    |        |     |                               |        |

|                                  |                                                                                                | CSAGAIN = Tied to GND (LEVEL0)                                                                                                                                                                                 |        | 5   |                               | V/V    |

| A <sub>CSA</sub>                 | Sense amplifier gain                                                                           | CSAGAIN = 10kΩ typ tied to GND (LEVEL1)                                                                                                                                                                        |        | 10  |                               | V/V    |

| CSA                              | g                                                                                              | CSAGAIN = 30kΩ typ tied to GND (LEVEL2)                                                                                                                                                                        |        | 20  |                               | V/V    |

|                                  |                                                                                                | CSAGAIN = open; (LEVEL3)                                                                                                                                                                                       |        | 40  |                               | V/V    |

| A <sub>CSA_ERR_D</sub><br>RIFT   | Sense amplifier gain error temperature drift                                                   | T <sub>J</sub> = -40°C to 150°C                                                                                                                                                                                | -70    |     | 70                            | ppm/°C |

| tosz                             | Settling time to ±1%                                                                           | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 5 V/V, C <sub>SO</sub> = 500pF                                                                                                                                   |        | 0.6 |                               | μs     |

| t <sub>SET</sub>                 | County unit to ±170                                                                            | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 40 V/V, C <sub>SO</sub> = 500pF                                                                                                                                  |        | 0.8 |                               | μs     |

| BW                               | Bandwidth                                                                                      | A <sub>CSA</sub> = 5 V/V, C <sub>LOAD</sub> = 60-pF, small signal -3 dB                                                                                                                                        | 3      | 5   | 7                             | MHz    |

| V <sub>SWING</sub>               | Output voltage range                                                                           | V <sub>CSAREF</sub> = 3 to 5.5 V                                                                                                                                                                               | 0.25   |     | V <sub>CSAREF</sub><br>- 0.25 | V      |

| V <sub>COM</sub>                 | Common-mode input range                                                                        |                                                                                                                                                                                                                | -0.225 |     | 0.225                         | V      |

V<sub>GVDD</sub> = 12 V V<sub>VDRAIN</sub> = 48 V T<sub>J</sub> = 25°C (unless otherwise noted)

|                         | $2 \text{ V V}_{\text{VDRAIN}} = 48 \text{ V T}_{\text{J}} = 25^{\circ}\text{C} \text{ (unless of PARAMETER)}$ | TEST CONDITIONS                                                                    | MIN   | TYP      | MAX   | UNIT     |

|-------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|----------|-------|----------|

| V <sub>OFF</sub>        | Input offset voltage                                                                                           | $V_{SP} = V_{SN} = GND; T_J = 25^{\circ}C, Gain A_{CSA}$<br>= 10, 20, 40 V/V       | -1.94 |          | 1.94  | mV       |

| V <sub>OFF</sub>        | Input offset voltage                                                                                           | $V_{SP} = V_{SN} = GND$ ; $T_J = 25^{\circ}C$ , Gain $A_{CSA} = 5V/V$              | -3.34 |          | 3.34  | mV       |

| V <sub>OFF_DRIFT</sub>  | Input drift offset voltage                                                                                     | V <sub>SP</sub> = V <sub>SN</sub> = GND                                            |       | 8        |       | μV/°C    |

| V <sub>BIAS</sub>       | Output voltage bias ratio                                                                                      | V <sub>SP</sub> = V <sub>SN</sub> = GND                                            |       | 0.5      |       |          |

| I <sub>BIAS</sub>       | Input bias current                                                                                             | $V_{SP} = V_{SN} = GND, V_{CSAREF} = 3V \text{ to } 5.5V$                          |       |          | 100   | μΑ       |

| I <sub>BIAS_OFF</sub>   | Input bias current offset                                                                                      | I <sub>SP</sub> - I <sub>SN</sub>                                                  | -1    |          | 1     | μΑ       |

| CMRR                    | Common-mode rejection ratio                                                                                    | DC<br>20 kHz                                                                       |       | 80<br>60 |       | dB<br>dB |

| I <sub>CSA SUP</sub>    | Supply current for CSA                                                                                         | CSAREF, V <sub>CSAREF</sub> = 3.V to 5.5V                                          |       | 1.5      |       | mA       |

| T <sub>CMREC</sub>      | Common mode recovery time                                                                                      |                                                                                    |       | 2        |       | us       |

| PROTECTIO               | N CIRCUITS                                                                                                     |                                                                                    |       |          |       |          |

| .,                      | OVDD and broad to see the see the                                                                              | V <sub>GVDD</sub> rising                                                           |       | 7.4      |       | V        |

| $V_{GVDD\_UV}$          | GVDD undervoltage threshold                                                                                    | V <sub>GVDD</sub> falling                                                          |       | 6.7      |       | V        |

| \ /                     | CVDD under seltere threehold                                                                                   | V <sub>GVDD</sub> rising, DRV8162L                                                 |       | 4.8      |       | V        |

| $V_{GVDD\_UV}$          | GVDD undervoltage threshold                                                                                    | V <sub>GVDD</sub> falling, DRV8162L                                                |       | 4.7      |       | V        |

| t <sub>GVDD_UV_DG</sub> | GVDD undervoltage deglitch time                                                                                |                                                                                    | 5     | 10       | 15    | μs       |

|                         | Bootstrap undervoltage threshold                                                                               | V <sub>BST</sub> - V <sub>SH</sub> ; V <sub>BST</sub> rising, GVDD = 12V           |       | 7.43     |       | V        |

|                         | Bootstrap undervoltage threshold                                                                               | $V_{BST}$ - $V_{SH}$ ; $V_{BST}$ falling, GVDD = 12V                               |       | 7.25     |       | V        |

| V <sub>BST_UV</sub>     | Bootstrap undervoltage threshold                                                                               | $V_{BST}$ - $V_{SH}$ ; $V_{BST}$ rising, GVDD = 5V, DRV8162L                       |       | 4.08     |       | V        |

|                         | Bootstrap undervoltage threshold                                                                               | V <sub>BST</sub> - V <sub>SH</sub> ; V <sub>BST</sub> falling, GVDD = 5V, DRV8162L |       | 3.94     |       | V        |

| V <sub>DS_LVL0-0</sub>  |                                                                                                                | $R_{VDSLVL} = 0.1 \text{ K}\Omega \text{ max (LEVEL0)}$                            | 0.087 | 0.1      | 0.116 |          |

| V <sub>DS_LVL1-1</sub>  |                                                                                                                | $R_{VDSLVL}$ = 2 K $\Omega$ typ (LEVEL1); one pulse detected on VDSLVL pin         | 0.136 | 0.15     | 0.166 |          |

| V <sub>DS_LVL1-0</sub>  |                                                                                                                | $R_{VDSLVL} = 2 K\Omega \text{ typ (LEVEL1); DC}$                                  | 0.187 | 0.2      | 0.217 |          |

| V <sub>DS_LVL2-1</sub>  |                                                                                                                | $R_{VDSLVL}$ = 5.6 KΩ typ (LEVEL2); one pulse detected on VDSLVL pin               | 0.28  | 0.3      | 0.319 |          |

| V <sub>DS_LVL2-0</sub>  |                                                                                                                | $R_{VDSLVL}$ = 5.6 KΩ typ (LEVEL2)                                                 | 0.38  | 0.4      | 0.42  |          |

| V <sub>DS_LVL3-1</sub>  |                                                                                                                | $R_{VDSLVL}$ = 12 K $\Omega$ typ (LEVEL3); one pulse detected on VDSLVL pin        | 0.482 | 0.5      | 0.53  |          |

| V <sub>DS_LVL3-0</sub>  | V <sub>DS</sub> overcurrent protection threshold level (DC)                                                    | $R_{VDSLVL}$ = 12 K $\Omega$ typ (LEVEL3)                                          | 0.575 | 0.6      | 0.623 | V        |

| V <sub>DS_LVL4-1</sub>  |                                                                                                                | $R_{VDSLVL}$ = 26 K $\Omega$ typ (LEVEL4); one pulse detected on VDSLVL pin        | 0.67  | 0.7      | 0.73  |          |

| V <sub>DS_LVL4-0</sub>  |                                                                                                                | $R_{VDSLVL} = 26 \text{ K}\Omega \text{ typ (LEVEL4)}$                             | 0.765 | 0.8      | 0.83  |          |

| V <sub>DS_LVL5-1</sub>  |                                                                                                                | $R_{VDSLVL}$ = 62 K $\Omega$ typ (LEVEL5); one pulse detected on VDSLVL pin        | 0.87  | 0.9      | 0.934 |          |

| V <sub>DS_LVL5-0</sub>  |                                                                                                                | $R_{VDSLVL} = 62 \text{ K}\Omega \text{ typ (LEVEL5)}$                             | 0.96  | 1.0      | 1.04  |          |

| V <sub>DS_LVL6-1</sub>  |                                                                                                                | $R_{VDSLVL}$ = 130 KΩ typ (LEVEL6); one pulse detected on VDSLVL pin VDSLVL        | 1.46  | 1.5      | 1.548 |          |

| V <sub>DS_LVL6-0</sub>  |                                                                                                                | $R_{VDSLVL}$ = 130 KΩ typ (LEVEL6);                                                | 1.945 | 2.0      | 2.05  |          |

| t <sub>DS_DG</sub>      | V <sub>DS</sub> protection deglitch time                                                                       |                                                                                    |       | 3        |       | μs       |

| t <sub>DS_BLK</sub>     | V <sub>DS</sub> overcurrent protection blanking time                                                           |                                                                                    |       | 1        |       | μs       |

| t <sub>CLRFLT</sub>     | V <sub>DS</sub> overcurrent protection fault clear time                                                        | INH=INL=Low                                                                        |       | 250      |       | μs       |

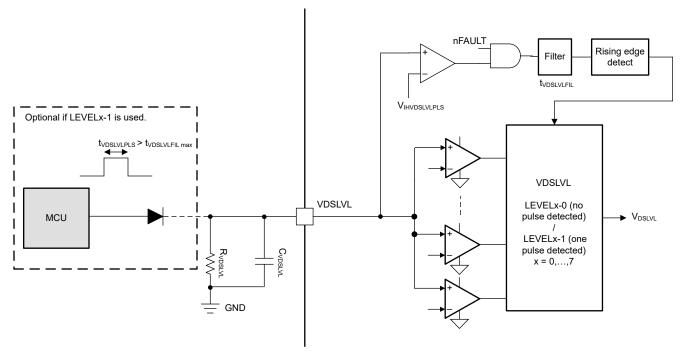

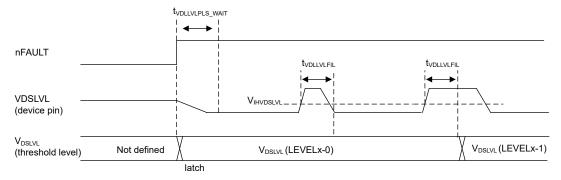

| t <sub>VDSLVLFIL</sub>  | VDSLVL one pulse filter time                                                                                   |                                                                                    |       | 4        | T     | μs       |

$V_{GVDD}$  = 12 V  $V_{VDRAIN}$  = 48 V  $T_J$  = 25°C (unless otherwise noted)

|                       | PARAMETER                                     | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------|------------------------|-----|-----|-----|------|

| V <sub>IHVDSLVL</sub> | VDSLVL one pulse high-level detection voltage |                        |     | 1   |     | V    |

| T <sub>OTSD</sub>     | Thermal shutdown temperature                  | T <sub>J</sub> rising; | 158 | 170 | 187 | °C   |

| T <sub>HYS</sub>      | Thermal shutdown hysteresis                   |                        | 7   | 8.5 | 10  | °C   |

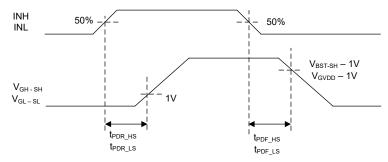

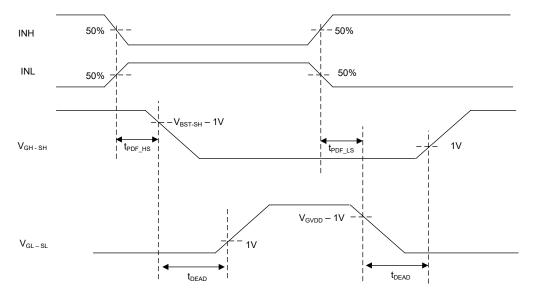

# **6.6 Timing Diagrams**

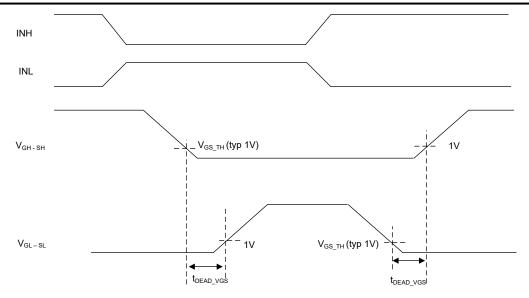

Figure 6-1. Gate Driver Propagation Delay Timing Diagram

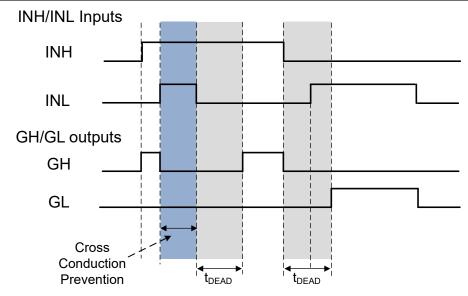

Figure 6-2. Gate Driver Dead Timing Insertion (INH and INL monitor mode)

Figure 6-3. Gate Driver Dead Timing Insertion (VGS monitor mode)

# 7 Detailed Description

## 7.1 Overview

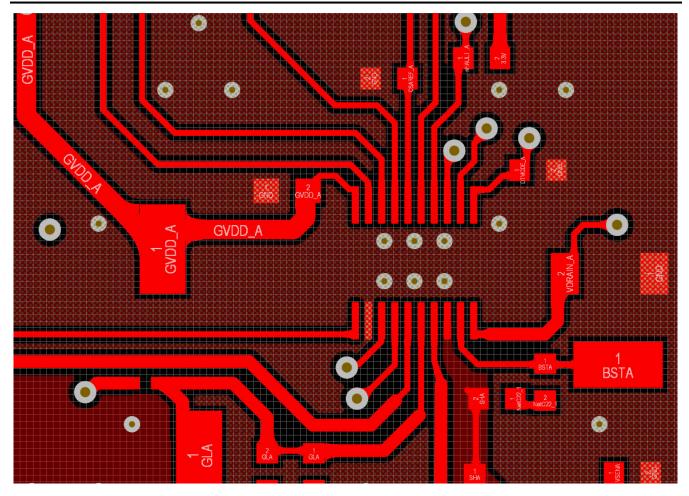

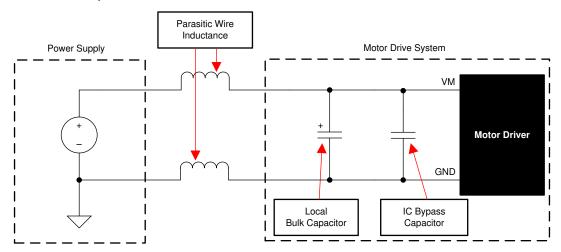

The DRV816x devices are integrated 100V gate drivers for various electromechanical loads including brushless DC (BLDC) motors, brushed DC motors, stepper motors, switched reluctance motors, and solenoids. These devices reduce system component count, cost, and complexity by integrating half-bridge gate drivers with a trickle charge pump, bootstrap diode, and FET VDS monitoring. The FET VDS monitors protect the external FETs against shorts to the supply, to ground, or across motor terminals. The DRV8161 integrates a bidirectional low-side current sense amplifier for current feedback to the controller ADC. The half-bridge architecture allows for the gate driver to be placed near the power stage FETs to simplify signal routing, reduce radiated EMI, and reduce overall PCB area.

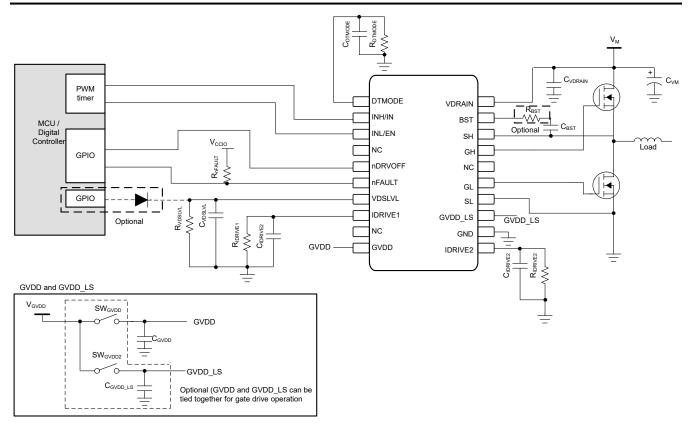

The gate drivers support external N-channel high-side and low-side power MOSFETs and can drive up to 1A source, 2A sink peak currents. The integrated bootstrap diode, external bootstrap capacitor, and integrated trickle charge pump generate the high-side gate drive supply voltage from the GVDD pin. The GVDD pin directly supplies the low-side gate drive supply voltage. The DRV8162 and DRV8162L device variants offer separate GVDD and GVDD LS pins to help the system design of safe torque off (STO).

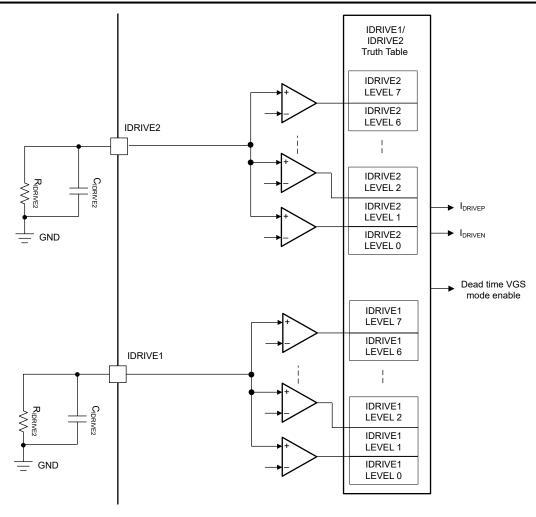

A smart gate-drive architecture provides the ability to adjust the output gate-drive current strength allowing for the gate driver to control the power MOSFET VDS switching speed. This allows for the removal of external gate drive resistors and diodes reducing BOM component count, cost, and PCB area. The architecture also uses an internal state machine to protect against gate-drive short-circuit events, control the half-bridge dead time, and protect against dV/dt parasitic turn on of the external power MOSFET.

In addition to the high level of device integration, the DRV816x devices provide a wide range of integrated protection features. These features include power-supply under voltage lockout (UVLO), VDS over current monitoring (OCP), and over temperature shutdown (OTSD). The nFAULT pin indicates fault events detected by the protection features.

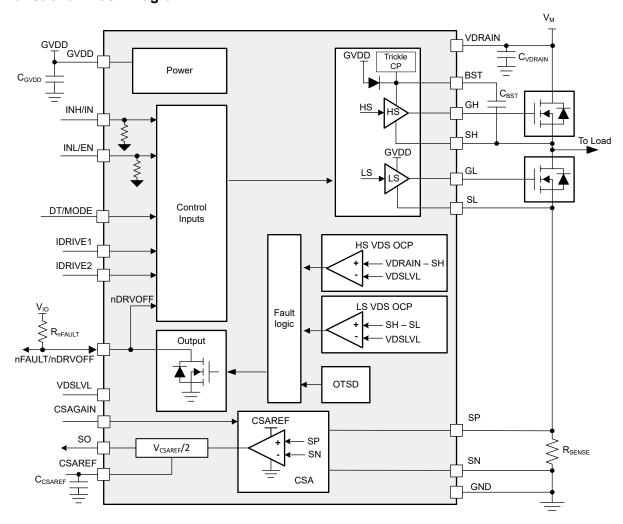

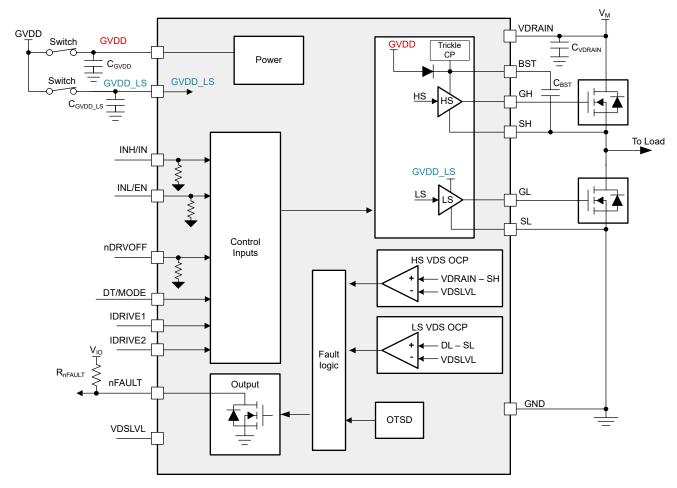

# 7.2 Functional Block Diagram

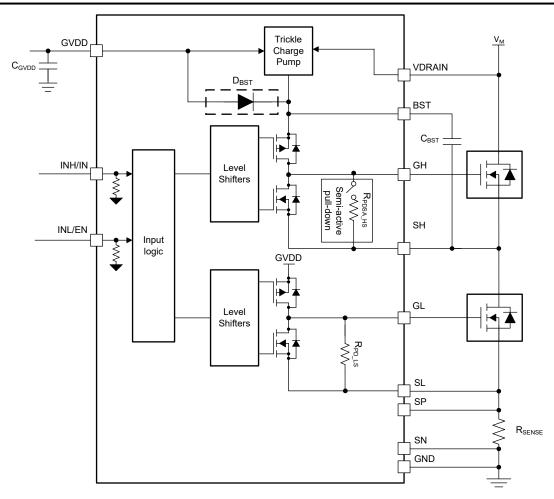

Figure 7-1. Block Diagram for DRV8161

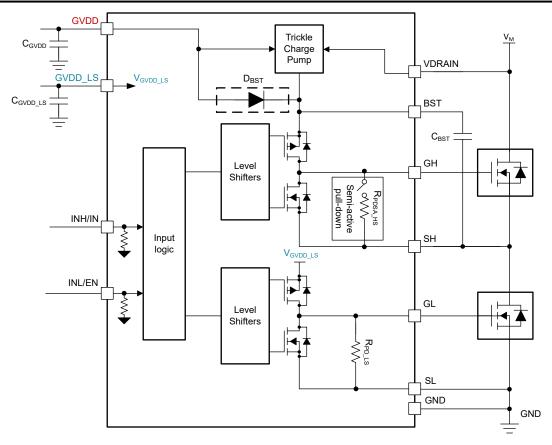

Figure 7-2. Block Diagram for DRV8162 and DRV8162L

## 7.3 Feature Description

## 7.3.1 Gate Drivers

The DRV816x family of devices integrates high-side and low-side FET gate drivers capable of driving N-channel power MOSFETs in half-bridge configuration. A bootstrap gate drive architecture generates the high-side gate driver voltage during PWM switching. The GVDD pin supplies both high-side and low-side gate drivers and sets the  $V_{GS}$  voltage for the FETs.

The DRV816x devices support half-bridge power stage architecture. In addition to the regular 2-pin PWM, 1-pin PWM control interface, the device offers an independent PWM mode by disabling shoot through protection and allowing the high-side and low-side FETs to be controlled independently. Independent FET control is useful for driving solenoids and switched reluctance motors. The DRV8162 and DRV8162L have separate supply pins (GVDD and GVDD\_LS) for high-side and low-side FET gate drive. This allows the system to support safe torque off (STO) function by adding external power switches to the gate drive supply pins.

#### 7.3.1.1 PWM Control Modes

The DRV816x family of devices provides three different PWM control modes to support various commutation and control methods. The PWM control modes are 1-pin PWM, 2-pin PWM and independent PWM mode. The modes are configured by DT/MODE pin.

DT/MODE pin is latched at power up, so to change the PWM control mode the device needs to be reset through power supply. Refer to Table 7-6 for the configuration of PWM control mode using the DT/MODE pin.

#### 7.3.1.1.1 2-pin PWM Mode

In 2-pin PWM mode, half-bridge driver supports three output states: low, high, or high-impedance (Hi-Z). The corresponding INH and INL signals control the output state as listed in Table 7-1.

INL INH GL GH SH 0 0 L L Hi-Z 1 0 L Н Н 1 0 Н L L 1 1 L L Hi-Z

Table 7-1. 2-pin PWM Mode Truth Table

#### 7.3.1.1.2 1-pin PWM Mode

In 1-pin PWM mode, the IN pin controls half-bridge and supports two output states: low or high. The EN pin is used to put the half bridge in the Hi-Z state. If the Hi-Z state is not required, tie INL/EN pin to logic high. The corresponding INH/IN and INL/EN signals control the output state as listed in Table 7-2.

Table 7-2. 1-pin PWM Mode Truth Table

| INL/EN | INH/IN | GL | GH | SH   |

|--------|--------|----|----|------|

| 0      | Х      | L  | L  | Hi-Z |

| 1      | 0      | Н  | L  | L    |

| 1      | 1      | L  | Н  | Н    |

#### 7.3.1.1.3 Independent PWM Mode

DRV816x supports independent PWM mode, the INH and INL pins control the outputs, GH and GL, respectively. This control mode lets the device drive separate high-side and low-side load. The independent PWM drive mode can be used for various type of loads including solenoids, Switched Reluctance Motor (SRM), unidirectional brushed DC motors, and low-side and high-side switches. In this mode, turning on both the high-side and low-side MOSFETs at the same time in a given half bridge gate driver is possible to use the device as a high-side or low-side driver. The shoot-through protection and dead time are bypassed in the mode.

**Table 7-3. Independent PWM Mode Truth Table**

| INL | INH | GL | GH |

|-----|-----|----|----|

| 0   | 0   | L  | L  |

| 0   | 1   | L  | Н  |

| 1   | 0   | Н  | L  |

| 1   | 1   | Н  | Н  |

Figure 7-3 shows how the device can be used to connect an inductive load where both the high-side and low-side MOSFETs can be turned on at the same time to drive the load without causing shoot-through. The external diodes for current recirculation are recommended. This configuration helps the design of solenoids or applications. The trickle charge pump is enabled all the time regardless of low-side PWM activity.

#### **Note**

The low-side VDS monitor of DRV816x is not available if independent PWM mode is configured. For DRV8161, the CSA output can be monitored by MCU to detect the over current condition.

Figure 7-3. Independent PWM mode for single load between high-side and low-side

Figure 7-4 shows how the device can be used to connect a high-side load and a low-side load at the same time with one half-bridge and drive the loads independently.

Figure 7-4. Independent PWM mode for high-side and low-side independent loads

## 7.3.1.2 Gate Drive Architecture

The gate driver device use a complimentary, push-pull topology for both the high-side and low-side drivers. This topology allows for both a strong pullup and pulldown of the external MOSFET gates. The low side gate driver is supplied directly from the GVDD regulator supply. For the high-side gate driver a bootstrap diode and capacitor are used to generate the floating high-side gate voltage supply. The bootstrap diode is integrated and an external bootstrap capacitor is used on the BST pin.

The high-side gate driver has semi-active pull down and low side gate has passive pull down to help prevent the external MOSFET from turning ON when power supply is disconnected.

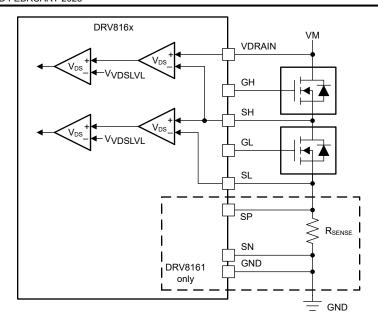

Figure 7-5. DRV8161 Gate Driver Block Diagram

Figure 7-6. DRV8162 and DRV8162L Gate Driver Block Diagram

# 7.3.1.2.1 Tickle Charge Pump (TCP)