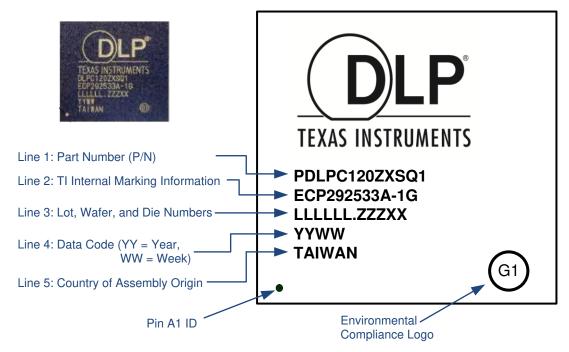

**DLPC120-Q1** DLPS096B - NOVEMBER 2017 - REVISED MAY 2022

## **DLPC120-Q1 Automotive DMD Controller**

#### 1 Features

- AEC-Q100 qualified for automotive applications:

- Temperature grade 2: -40°C to 105°C ambient

- Compatibility with three DMD devices:

- DLP3030-Q1: 0.3 WVGA S450

- DLP3020-Q1: 0.3 WVGA S247

- DLP3021-Q1: 0.3 WVGA S247

- Video input interface:

- 24-bit parallel (RGB888, RGB666, or RGB565)

- 60-Hz frame rate

- Input resolutions from QVGA through WVGA

- Pixel clock up to 40 MHz

- Video processing:

- Image scaling

- Programmable de-gamma curve

- Bezel adjustment

- Horizontal and vertical image flip

- DMD interface:

- 78-MHz DDR DMD interface

- Consistent DMD data loading and reset control overtemperature operating range

- Automatic DMD parking at power-down

- DMD temperature management

- External memory support

- DDR2: 312-MHz clock (624-MHz data rate)

- Serial flash 39-MHz clock

- System control

- I<sup>2</sup>C communication interface

- Programmable splash screens

- DMD power and reset driver control

- Programmable flash-based configuration

- Test support

- Built-in test pattern generator

- JTAG with boundary scan support

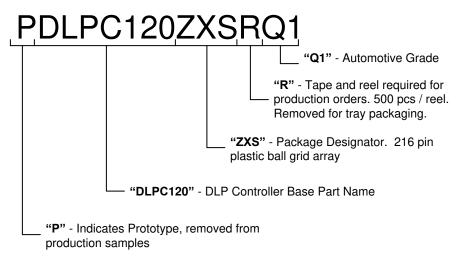

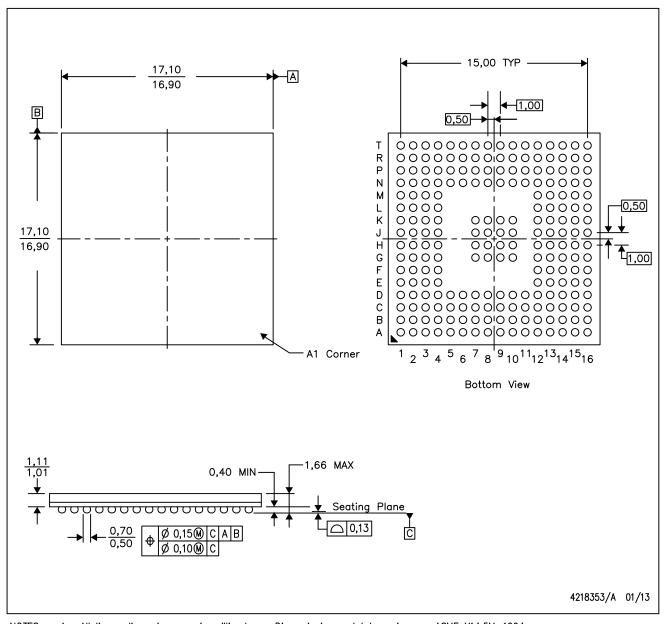

- Packaged in a 216-pin, 1.0-mm pitch BGA

### 2 Applications

- Wide field of view and augmented reality head-up display (HUD)

- Interior projection display and lighting

- Digital cluster, navigation, and infotainment windshield displays

- Automotive small light

- Dynamic ground projection

### 3 Description

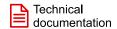

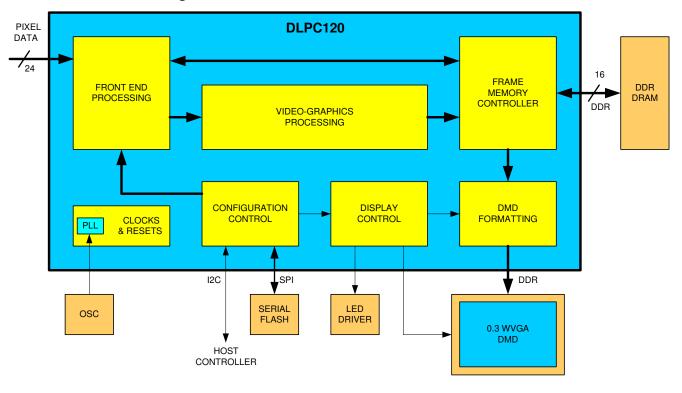

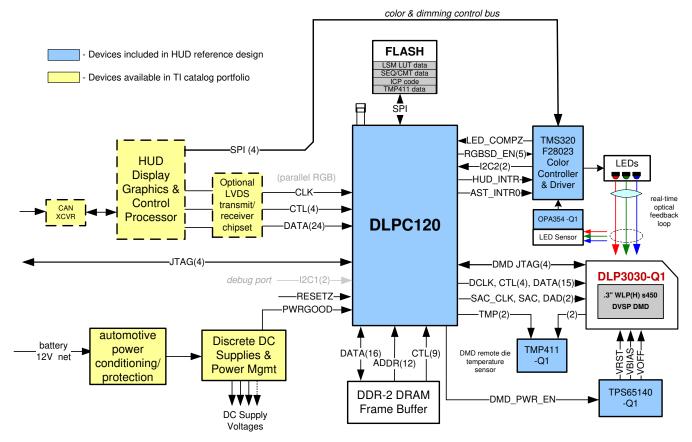

The DLPC120-Q1 DMD display controller for automotive applications is part of a chipset compatible with one of three digital micromirror devices (DMDs), DLP3030-Q1, DLP3020-Q1, or DLP3021-Q1. The core DLPC120-Q1 logic is responsible for accepting video input and formatting the data to display on the DMD while simultaneously controlling RGB LEDs in order to create a real-time image. The DLPC120-Q1 is also responsible for controlling the power-up and power-down events of the DMD, based on external system control or temperature input from the DMD. Combined with an external dimming circuit and microcontroller, the DLPC120-Q1 supports a wide dimming range > 5000:1 for HUD applications. Typically, the DLPC120-Q1 is a peripheral device in an I<sup>2</sup>C interface with a host processor.

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | PACKAGE     | BODY SIZE (NOM)     |

|----------------------------|-------------|---------------------|

| DLPC120-Q1                 | NFBGA (216) | 17.00 mm × 17.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

**Typical System Diagram**

| 1 Features1                                           | 6.13 JTAG Interface Timing Requirements              | 19 |

|-------------------------------------------------------|------------------------------------------------------|----|

| 2 Applications1                                       | 6.14 I <sup>2</sup> C Interface Timing Requirements  |    |

| 3 Description1                                        | 7 Parameter Measurement Information                  |    |

| Revision History2                                     | 7.1 Parallel Interface Input Source Timing           |    |

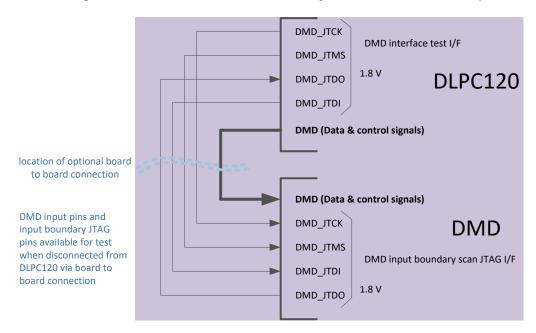

| 5 Pin Configuration and Functions3                    | 7.2 Design for Test Functions                        |    |

| 5.1 LED Driver Interface5                             | 8 Detailed Description                               |    |

| 5.2 DMD Temperature Interface5                        | 8.1 Overview                                         |    |

| General Purpose I/O6                                  | 8.2 Functional Block Diagram                         |    |

| 5.3 Main Video and Data Control Interface6            | 8.3 Feature Description                              |    |

| 5.4 DMD Interface7                                    | 8.4 Device Functional Modes                          |    |

| 5.5 Memory Interface8                                 | 9 Application and Implementation                     | 26 |

| Board Level Test and Debug9                           | 9.1 Application Information                          |    |

| Manufacturing Test Support9                           | 9.2 Typical Application                              |    |

| Test Point Interface9                                 | 10 Power Supply Recommendations                      |    |

| Power and Ground10                                    | 10.1 Power Supply Filtering                          |    |

| 6 Specifications12                                    | 11 Layout                                            |    |

| 6.1 Absolute Maximum Ratings12                        | 11.1 Layout Guidelines                               | 30 |

| 6.2 ESD Ratings12                                     | 12 Device and Documentation Support                  | 33 |

| 6.3 Recommended Operating Conditions12                | 12.1 Third-Party Products Disclaimer                 | 33 |

| 6.4 Thermal Information12                             | 12.2 Device Support                                  | 33 |

| 6.5 Electrical Characteristics13                      | 12.3 Documentation Support                           | 34 |

| 6.6 Electrical Characteristics for I/O13              | 12.4 Receiving Notification of Documentation Updates | 34 |

| 6.7 Power Supply and Reset Timing Requirements 13     | 12.5 Support Resources                               |    |

| 6.8 Reference Clock PLL Timing Requirements15         | 12.6 Trademarks                                      |    |

| 6.9 Parallel Interface General Timing Requirements 16 | 12.7 Electrostatic Discharge Caution                 | 34 |

| 6.10 Parallel Interface Frame Timing Requirements16   | 12.8 Glossary                                        | 34 |

| 6.11 Flash Memory Interface Timing Requirements 17    | 13 Mechanical, Packaging, and Orderable              |    |

| 6.12 DMD Interface Timing Requirements18              | Information                                          | 35 |

| 4 Revision History                                    |                                                      |    |

| С | hanges from Revision A (March 2018) to Revision B (April 2022)                                                                                                             | Page |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added DLP3020-Q1 and DLP3021-Q1 as supported devices. Removed DLP3000-Q1                                                                                                   |      |

| • | Included digital cluster, navigation and infotainment windshield displays, automotive small light and dyr ground projection applications                                   |      |

| • | This document is updated per the latest Texas Instruments and industry data sheet standards                                                                                |      |

| • | Updated the body size from 16 mm × 16 mm to 17 mm × 17 mm, and added the DLP3020-Q1 and DLF Q1 devices as supported devices. Removed DLP3000                               |      |

| • | This document is updated per the latest Texas Instruments and industry inclusive terminologies. All occurrences of MISO are now POCI; all occurrences of MOSI are now PICO |      |

| • | Updated LED Driver Interface                                                                                                                                               |      |

|   | Updated Design Requirements                                                                                                                                                |      |

|   | Updated General PCB Recommendations                                                                                                                                        |      |

| _ | •                                                                                                                                                                          |      |

| С | hanges from Revision * (November 2017) to Revision A (March 2018)                                    | Page |

|---|------------------------------------------------------------------------------------------------------|------|

| • | Changed the device status from Advance Information to Production Data                                | 1    |

| • | Changed case-to-junction thermal coefficient from 0.77°C/W: to 0.28°C/W in Thermal Information table | 12   |

| • | Updated Temperature Monitor Function                                                                 | 25   |

|   | Updated Application Information                                                                      |      |

|   |                                                                                                      |      |

# **5 Pin Configuration and Functions**

|   | 1            | 2             | 3                   | 4                   | 5                   | 6             | 7                    | 8            | 9            | 10           | 11             | 12            | 13            | 14               | 15               | 16                |   |

|---|--------------|---------------|---------------------|---------------------|---------------------|---------------|----------------------|--------------|--------------|--------------|----------------|---------------|---------------|------------------|------------------|-------------------|---|

| A | VSS          | VCCIO<br>_2   | DMD_<br>SAC_<br>CLK | DMD_<br>SAC_<br>BUS | DMD_<br>DAD_<br>OEZ | DMD_          | DMD_<br>D14          | DMD_<br>D11  | DMD_<br>D10  | DMD_D8       | DMD_D5         | DMD_D2        | DMD_D1        | HUD_<br>INTR     | AUX<br>BIT_2     | vss               | A |

| В | MEM_<br>A10  | VCCIO<br>_1   | vss                 | DMD_                | DMD_<br>DAD_<br>BUS | DMD_<br>SCTRL | DMD_<br>TRC          | DMD_<br>D12  | DMD_D9       | DMD_D7       | DMD_D3         | DMD_D0        | AUX<br>BIT_7  | AUX<br>BIT_1     | VCCIO            | LED_S<br>_EN      | В |

| С | MEM_A1       | MEM_<br>WEZ   | MEM_<br>RST         | DMD_<br>JTDO        | DMD_<br>JTMS        | vss           | DMD_<br>LOADB        | DMD_D1       | vss          | DMD_D4       | DMD_<br>PWR_EN | vss           | AUX<br>BIT_0  | HTR_<br>ENABLE   | LED_B<br>_EN     | LED_R<br>_EN      | С |

| D | MEM_<br>A11  | MEM_A3        | MEM_<br>RASZ        | VCCIO<br>_1         | DMD_<br>JTDI        | VCCIO<br>_2   | DMD_<br>DAD_<br>STRB | VCCIO<br>_2  | DMD_D6       | VCCIO<br>_2  | AUX<br>BIT_6   | VCCIO<br>_2   | LED_<br>COMPZ | LED_G<br>_EN     | LEDDRV<br>_ON    | LED_<br>B_PWM     | D |

| E | MEM_A9       | MEM_<br>A12   | vss                 | MEM_<br>ODT         |                     |               |                      |              |              |              |                | VCCIO         | LED_D<br>_EN  | LED_<br>R_PWM    | FLASH_<br>PICO   | FLASH_S<br>CLK    | E |

| F | MEM_<br>CLKZ | MEM_          | MEM_A8              | MEM_A2              |                     |               |                      |              |              |              |                | VSSA<br>(PLL) | LED_<br>G_PWM | FLASH_<br>POCI   | FLASH_<br>CSZ    | LED_EN            | F |

| G | MEM_A5       | MEM_A6        | MEM_A7              | VCCIO<br>_1         |                     |               | vss                  | VDD          | VDD          | vss          |                | VCCA<br>(PLL) | PWR<br>GOOD   | PLL_REF<br>CLK_O | PLL_REF<br>CLK_I | HW<br>TEST<br>_EN | G |

| н | MEM_A0       | MEM_A4        | VSS                 | MEM_<br>VREF0       |                     |               | VDD                  | vss          | vss          | VDD          |                | TSTPT<br>_6   | RESETZ        | <b>TSTPT</b> _7  | TSTPT<br>_5      | TSTPT<br>_4       | н |

| J | MEM_<br>BAO  | MEM_<br>BA1   | MEM_<br>CASZ        | MEM_ZQ              |                     |               | VDD                  | vss          | vss          | VDD          |                | VDDQ          | JTAG<br>RSTZ  | TSTPT<br>_1      | TSTPT<br>_2      | TSTPT<br>_3       | J |

| ĸ | MEM_<br>CKE  | MEM_<br>CSZ   | MEM_<br>ATO         | VCCIO<br>_1         |                     |               | vss                  | VDD          | VDD          | vss          |                | vss           | TMP<br>_SDA   | JTAG<br>TDO      | JTAG<br>TDI      | TSTPT<br>_0       | K |

| L | MEM_<br>DQ7  | MEM_<br>DQ6   | MEM_<br>DQ4         | VSS                 |                     |               |                      |              |              |              |                | AST_<br>CLR0  | AST_<br>INTR0 | VCCIO            | JTAG<br>TCK      | JTAG<br>TMS       | L |

| м | MEM_<br>DQ5  | MEM_<br>DQ3   | VCCIO<br>_1         | MEM_<br>DTO0        |                     |               |                      |              |              |              |                | AST_<br>CLR1  | AST_<br>HLD0  | AST_<br>INTR1    | I2C<br>_SCL_2    | TMP<br>_SCL       | М |

| N | MEM_<br>DQS0 | MEM_<br>DQSZ0 | vss                 | MEM_<br>DTO1        | VCCIO<br>_1         | MEM_<br>VREF1 | vss                  | P_<br>DATAEN | PDATA<br>[4] | VCCIO<br>_3  | PDATA<br>[14]  | PDATA<br>[19] | PDATA<br>[21] | vss              | I2C<br>_SDA_1    | 12C<br>_SDA_2     | N |

| P | MEM_<br>DQ2  | MEM_<br>DQ0   | VCCIO<br>_1         | vss                 | MEM_<br>DQ12        | vss           | P_<br>VSYNC          | P_<br>HSYNC  | vss          | PDATA<br>[7] | PDATA<br>[10]  | PDATA<br>[13] | VCCIO         | PDATA<br>[22]    | PDATA<br>[23]    | 12C<br>_SCL_1     | P |

| R | MEM_<br>DQ1  | vss           | MEM_<br>DQ15        | MEM_<br>DQS1        | MEM_<br>DQ11        | MEM_<br>DQ9   | VCCIO<br>_1          | PDATA<br>[0] | PDATA<br>[2] | PDATA<br>[5] | PDATA<br>[8]   | PDATA<br>[11] | PDATA<br>[15] | PDATA<br>[18]    | PDATA<br>[20]    | AST_<br>HLD1      | R |

| т | VSS          | MEM_<br>DQ14  | MEM_<br>DQ13        | MEM_<br>DQSZ1       | MEM_<br>DQ10        | MEM_<br>DQ8   | VSS                  | PCLK         | PDATA<br>[1] | PDATA<br>[3] | PDATA<br>[6]   | PDATA<br>[9]  | PDATA<br>[12] | PDATA<br>[16]    | PDATA<br>[17]    | vss               | т |

|   | 1            | 2             | 3                   | 4                   | 5                   | 6             | 7                    | 8            | 9            | 10           | 11             | 12            | 13            | 14               | 15               | 16                | - |

Figure 5-1. ZXS Package 216-Pin BGA Top View

Table 5-1. DLPC120-Q1 Device Initialization and Programming Pin Descriptions

| PIN          |     | I/O    | I/O            | CLOCK      | bit and Frogramming Fin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|-----|--------|----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO. | POWER  | TYPE           | SYSTEM     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RESETZ       | H13 |        | l <sub>2</sub> | Async      | Functional Reset (Active Low). Resets internal logic and causes PLL startup and PLL locking. Assertion is required after power supplies are within limits. See Section 6.7 for timing requirements.                                                                                                                                                                                                                                                                                                         |

| PWRGOOD      | G13 |        | I <sub>2</sub> | Async      | System Power Good indicator. Should be held low until all DLPC120-Q1 power has been within operating limits. See Section 6.7 for timing requirements. Must be set high to enable normal operation. When set low, the DLPC120-Q1 begins the parking routine for the DMD. Together with pin E14 (LED_R_PWM / PWRGOOD_CNTRL), this signal is critical for DLP30xx-Q1 parking as part of the Pre-Conditioning Sequence and subsequent un-parking. See DLPC120-Q1 Programmer's Guide for implementation details. |

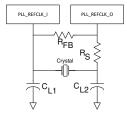

| PLL_REFCLK_I | G15 |        | l <sub>2</sub> | N/A        | Reference Clock Input (16 MHz). Can be driven by crystal across this pin and PLL_REFCLK_O or by external oscillator. See Section 6.7 for timing requirements.                                                                                                                                                                                                                                                                                                                                               |

| PLL_REFCLK_O | G14 |        | O <sub>6</sub> | N/A        | Crystal output. Used with PLL_REFCLK_I.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HUD_INTR     | A14 | 3.30 V | O <sub>6</sub> | N/A        | Interrupt signal. This active high signal indicates one of the interrupt sources in the controller has been triggered.                                                                                                                                                                                                                                                                                                                                                                                      |

| IIC_SCL_1    | P16 |        | B <sub>8</sub> | N/A        | I <sup>2</sup> C Clock for Device configuration and control. Requires external pull-up. Port 1 peripheral command/control interface.                                                                                                                                                                                                                                                                                                                                                                        |

| IIC_SDA_1    | N15 |        | B <sub>8</sub> | N/A        | I <sup>2</sup> C Data for Device configuration and control. Requires external pull-up. Port 1 peripheral command/control interface.                                                                                                                                                                                                                                                                                                                                                                         |

| IIC_SCL_2    | M15 |        | B <sub>8</sub> | N/A        | I <sup>2</sup> C Clock Debug Port. Requires external pull-up. Port 2 peripheral command/control interface.                                                                                                                                                                                                                                                                                                                                                                                                  |

| IIC_SDA_2    | N16 |        | B <sub>8</sub> | N/A        | I <sup>2</sup> C Data Debug Port. Requires external pull-up. Port 2 peripheral command/control interface.                                                                                                                                                                                                                                                                                                                                                                                                   |

| FLASH_POCI   | F14 |        | l <sub>2</sub> | FLASH_SCLK | Serial Data input from the external SPI Flash device. This provides device logical programming data as well as functional configuration parameter data.                                                                                                                                                                                                                                                                                                                                                     |

| FLASH_CSZ    | F15 | _      | O <sub>6</sub> | FLASH_SCLK | Chip Select output for the external SPI Flash device. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FLASH_SCLK   | E16 |        | O <sub>6</sub> | N/A        | Clock for the external SPI Flash device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FLASH_PICO   | E15 |        | O <sub>6</sub> | FLASH_SCLK | Serial Data output to the external SPI Flash device. This pin sends address and control information as well as data when programming.                                                                                                                                                                                                                                                                                                                                                                       |

### **5.1 LED Driver Interface**

| PIN                          |     | I/O    | I/O            | CLOCK  | DESCRIPTION                                                                                                                                                                                                                                           |

|------------------------------|-----|--------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | NO. | POWER  | TYPE           | SYSTEM | DESCRIPTION                                                                                                                                                                                                                                           |

| LED_B_PWM                    | D16 |        | O <sub>6</sub> | N/A    | Function reserved for future use.                                                                                                                                                                                                                     |

| LED_R_PWM<br>(PWRGOOD_CNTRL) | E14 |        | O <sub>6</sub> | N/A    | Repurposed for power good control. Together with pin G13 (PWRGOOD), this signal is used for DLP30xx-Q1 parking as part of the preconditioning sequence and subsequent unparking. See the DLPC120-Q1 Programmer's Guide for implementation details.    |

| LED_G_PWM                    | F13 |        | O <sub>6</sub> | N/A    | Function reserved for future use.                                                                                                                                                                                                                     |

| LED_B_EN                     | C15 |        | O <sub>6</sub> | N/A    | Blue LED enable strobe. Controlled by programmable DMD sequence timing (active high)                                                                                                                                                                  |

| LED_R_EN                     | C16 |        | O <sub>6</sub> | N/A    | Red LED enable strobe. Controlled by programmable DMD sequence timing (active high)                                                                                                                                                                   |

| LED_G_EN                     | D14 |        | O <sub>6</sub> | N/A    | Green LED enable strobe. Controlled by programmable DMD sequence timing (active high)                                                                                                                                                                 |

| LED_S_EN                     | B16 |        | O <sub>6</sub> | N/A    | LED shunt enable. Controlled by programmable DMD sequence timing (active high)                                                                                                                                                                        |

| LED_D_EN                     | E13 |        | O <sub>6</sub> | N/A    | LED drive enable. Controlled by programmable DMD sequence timing (active high)                                                                                                                                                                        |

| LEDDRV_ON                    | D15 | 3.30 V | O <sub>6</sub> | Async  | LED driver enable. Active high output control to external LED drive logic                                                                                                                                                                             |

| LED_EN                       | F16 |        | I <sub>2</sub> | Async  | LED enable (active high input). A logic low on this signal forces LEDDRV_ON low and RGB strobes low. These signals are enabled 100 ms after LED_EN transitions to a high (assuming corresponding SW parameters are also set to enable LED operation). |

| LED_COMPZ                    | D13 |        | l <sub>2</sub> | Async  | LED threshold compare (active low input). A logic low on this signal indicates a threshold is reached, and in discontinuous mode controls shunt enable (LED_S_EN).                                                                                    |

| AST_CLR0                     | L12 | -      | O <sub>6</sub> | N/A    | Function reserved for future use                                                                                                                                                                                                                      |

| AST_HLD0                     | M13 |        | O <sub>6</sub> | N/A    | Function reserved for future use                                                                                                                                                                                                                      |

| AST_INTR0                    | L13 |        | O <sub>6</sub> | N/A    | Sequence timer interrupt port                                                                                                                                                                                                                         |

| AST_CLR1                     | M12 |        | O <sub>6</sub> | N/A    | Function reserved for future use                                                                                                                                                                                                                      |

| AST_HLD1                     | R16 |        | O <sub>6</sub> | N/A    | Function reserved for future use                                                                                                                                                                                                                      |

| AST_INTR1                    | M14 |        | O <sub>6</sub> | N/A    | Function reserved for future use                                                                                                                                                                                                                      |

# **5.2 DMD Temperature Interface**

| PIN        |     | I/O    | I/O            | CLOCK  |                                                                                                                                                                               |

|------------|-----|--------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO. | POWER  | TYPE           | SYSTEM | DESCRIPTION                                                                                                                                                                   |

| TMP_SDA    | K13 |        | B <sub>8</sub> | Async  | Temperature control serial data. This signal is used to communicate with the TMP411 to read the temperature values. Follows I <sup>2</sup> C protocol as required by TMP411.  |

| TMP_SCL    | M16 | 3.30 V | В <sub>8</sub> | Async  | Temperature control serial clock. This signal is used to communicate with the TMP411 to read the temperature values. Follows I <sup>2</sup> C protocol as required by TMP411. |

| HTR_ENABLE | C14 |        | O <sub>6</sub> | Async  | Reserved pin                                                                                                                                                                  |

# General Purpose I/O

| PIN                          |     | I/O    | I/O            | CLOCK  |                                                                                                                                                                                                                                                                                                           |

|------------------------------|-----|--------|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | NO. | POWER  | TYPE           | SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                               |

| AUXBIT_0<br>(FLICKER_SELECT) | C13 |        | O <sub>6</sub> | Async  | This pin is configured by default to be asserted at the lowest brightness mode to activate flicker reduction logic in the LED driver circuit. It is deasserted, otherwise, to deactivate the flicker reduction logic for normal operation. Contact a TI Applications Engineer for implementation details. |

| AUXBIT_1                     | B14 | 3.30 V | O <sub>6</sub> | Async  | DMD sequencer reset AUX Bit 1. Intended for system debug. Can be routed to a testpoint or left unconnected                                                                                                                                                                                                |

| AUXBIT_2                     | A15 |        | O <sub>6</sub> | Async  | DMD sequencer reset AUX Bit 2. Intended for system debug. Can be routed to a testpoint or left unconnected                                                                                                                                                                                                |

| AUXBIT_6                     | D11 |        | O <sub>6</sub> | Async  | DMD sequencer reset AUX Bit 6. Intended for system debug. Can be routed to a testpoint or left unconnected                                                                                                                                                                                                |

| AUXBIT_7                     | B13 |        | O <sub>6</sub> | Async  | DMD sequencer reset AUX Bit 7. Intended for system debug. Can be routed to a testpoint or left unconnected                                                                                                                                                                                                |

### 5.3 Main Video and Data Control Interface

| PIN       |     | I/O    | I/O            | CLOCK  |                                |

|-----------|-----|--------|----------------|--------|--------------------------------|

| NAME      | NO. | POWER  | TYPE           | SYSTEM | DESCRIPTION                    |

| PCLK      | T8  |        | l <sub>2</sub> | N/A    | Pixel clock <sup>(1)</sup>     |

| P_VSYNC   | P7  |        | l <sub>2</sub> |        | Vertical sync <sup>(2)</sup>   |

| P_HSYNC   | P8  |        | l <sub>2</sub> |        | Horizontal sync <sup>(2)</sup> |

| P_DATAEN  | N8  |        | l <sub>2</sub> |        | Data valid <sup>(2)</sup>      |

| PDATA[0]  | R8  |        | l <sub>2</sub> |        |                                |

| PDATA[1]  | Т9  |        | l <sub>2</sub> |        |                                |

| PDATA[2]  | R9  |        | l <sub>2</sub> |        |                                |

| PDATA[3]  | T10 |        | l <sub>2</sub> |        |                                |

| PDATA[4]  | N9  |        | l <sub>2</sub> |        |                                |

| PDATA[5]  | R10 |        | l <sub>2</sub> |        |                                |

| PDATA[6]  | T11 |        | l <sub>2</sub> |        |                                |

| PDATA[7]  | P10 |        | l <sub>2</sub> |        |                                |

| PDATA[8]  | R11 |        | l <sub>2</sub> |        |                                |

| PDATA[9]  | T12 | 3.30 V | l <sub>2</sub> |        |                                |

| PDATA[10] | P11 | 0.00 V | l <sub>2</sub> | PCLK   |                                |

| PDATA[11] | R12 |        | l <sub>2</sub> |        | Data <sup>(3)</sup>            |

| PDATA[12] | T13 |        | l <sub>2</sub> |        | Data                           |

| PDATA[13] | P12 |        | l <sub>2</sub> |        |                                |

| PDATA[14] | N11 |        | l <sub>2</sub> |        |                                |

| PDATA[15] | R13 |        | l <sub>2</sub> |        |                                |

| PDATA[16] | T14 |        | l <sub>2</sub> |        |                                |

| PDATA[17] | T15 |        | l <sub>2</sub> |        |                                |

| PDATA[18] | R14 |        | l <sub>2</sub> |        |                                |

| PDATA[19] | N12 |        | l <sub>2</sub> |        |                                |

| PDATA[20] | R15 |        | l <sub>2</sub> |        |                                |

| PDATA[21] | N13 |        | l <sub>2</sub> |        |                                |

| PDATA[22] | P14 |        | l <sub>2</sub> |        |                                |

| PDATA[23] | P15 |        | l <sub>2</sub> |        |                                |

(1) Pixel clock capture edge is software programmable.

www.ti.com

- VSYNC, HSYNC, and data valid polarity are software programmable. The 24-bit PDATA bus can be mapped based on pixel format. By default PDATA[23-16]=Red[7-0], PDATA[15-8]=Green[7-0], and PDATA[7-0]=Blue[7-0]. See the *DLPC120-Q1 Programmer's Guide* for more information. (3)

### 5.4 DMD Interface

| PIN          |     | I/O    | I/O            | CLOCK       |                                                                                                                                                                                                          |

|--------------|-----|--------|----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO. | POWER  | TYPE           | SYSTEM      | DESCRIPTION                                                                                                                                                                                              |

| DMD_D0       | B12 |        |                |             |                                                                                                                                                                                                          |

| DMD_D1       | A13 |        |                |             |                                                                                                                                                                                                          |

| DMD_D2       | A12 |        |                |             |                                                                                                                                                                                                          |

| DMD_D3       | B11 |        |                |             |                                                                                                                                                                                                          |

| DMD_D4       | C10 |        |                |             |                                                                                                                                                                                                          |

| DMD_D5       | A11 |        |                |             |                                                                                                                                                                                                          |

| DMD_D6       | D9  |        |                |             |                                                                                                                                                                                                          |

| DMD_D7       | B10 |        | O <sub>5</sub> | DMD_DCLK    | DMD data pins. DMD data pins are DDR (Double Data Rate) signals that are clocked on both edges of DMD DCLK.                                                                                              |

| DMD_D8       | A10 |        |                |             | signals that are discissed on both edges of binb_both.                                                                                                                                                   |

| DMD_D9       | В9  |        |                |             |                                                                                                                                                                                                          |

| DMD_D10      | A9  |        |                |             |                                                                                                                                                                                                          |

| DMD_D11      | A8  |        |                |             |                                                                                                                                                                                                          |

| DMD_D12      | B8  |        |                |             |                                                                                                                                                                                                          |

| DMD_D13      | C8  |        |                |             |                                                                                                                                                                                                          |

| DMD_D14      | A7  |        |                |             |                                                                                                                                                                                                          |

| DMD_DCLK     | A6  |        | O <sub>5</sub> | N/A         | DMD data clock (DDR)                                                                                                                                                                                     |

| DMD_LOADB    | C7  |        | O <sub>5</sub> | DMD_DCLK    | DMD data load signal (active low)                                                                                                                                                                        |

| DMD_SCTRL    | B6  | 1.80 V | O <sub>5</sub> | DMD_DCLK    | DMD data serial control signal                                                                                                                                                                           |

| DMD_TRC      | B7  |        | O <sub>5</sub> | DMD_DCLK    | DMD data toggle rate control                                                                                                                                                                             |

| DMD_DAD_OEZ  | A5  |        | O <sub>5</sub> | Async       | DMD DAD output enable (active low). A pullup (10 k $\Omega$ to 100 k $\Omega$ ) to the 1.8-V rail for the DMD interface is needed to keep this signal inactive when tristated.                           |

| DMD_DAD_BUS  | B5  |        | O <sub>5</sub> | DMD_SAC_CLK | DMD DAD bus data                                                                                                                                                                                         |

| DMD_DAD_STRB | D7  |        | O <sub>5</sub> | DMD_DCLK    | DMD DAD bus strobe.                                                                                                                                                                                      |

| DMD_SAC_BUS  | A4  |        | O <sub>5</sub> | DMD_SAC_CLK | DMD SAC bus data                                                                                                                                                                                         |

| DMD_SAC_CLK  | A3  |        | O <sub>5</sub> | N/A         | DMD SAC bus clock                                                                                                                                                                                        |

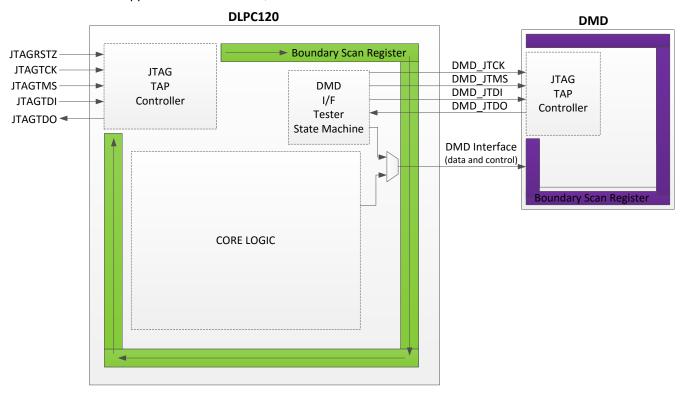

| DMD_JTCK     | B4  |        | O <sub>4</sub> | N/A         | DMD interface test clock. Signal connected to DMD JTAG interface to allow the verification of the interface. The interface is tristated when not active.                                                 |

| DMD_JTMS     | C5  |        | O <sub>4</sub> | N/A         | DMD interface test mode. Signal connected to DMD JTAG interface to allow the verification of the interface. The interface is tristated when not active.                                                  |

| DMD_JTDI     | D5  |        | O <sub>4</sub> | N/A         | DMD interface test data output. Signal connected to DMD JTAG interface to allow the verification of the interface. This signal connects to the DMD JTAG TDI. The interface is tristated when not active. |

| DMD_JTDO     | C4  |        | I <sub>1</sub> | N/A         | DMD interface test data input. Signal connected to DMD JTAG interface to allow the verification of the interface. This signal connects to the DMD JTAG TDO. Internal pulldown.                           |

| DMD_PWR_EN   | C11 | 3.30 V | O <sub>6</sub> | Async       | DMD power regulator enable (active high)                                                                                                                                                                 |

# **5.5 Memory Interface**

| PIN       |     | I/O    | I/O             | CLOCK       |                                                                                                                                                                                |

|-----------|-----|--------|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. | POWER  | TYPE            | SYSTEM      | DESCRIPTION                                                                                                                                                                    |

| MEM_CLK   | F2  |        |                 | <b>N1/A</b> | DDD                                                                                                                                                                            |

| MEM_CLKZ  | F1  | 1      | Os              | N/A         | DDR memory, Differential Memory Clock.                                                                                                                                         |

| MEM_A0    | H1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A1    | C1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A2    | F4  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A3    | D2  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A4    | H2  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A5    | G1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A6    | G2  | 1      | Os              | MEM_CLK     | DDR memory, Multiplexed Row and Column Address.                                                                                                                                |

| MEM_A7    | G3  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A8    | F3  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A9    | E1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A10   | B1  |        |                 |             |                                                                                                                                                                                |

| MEM_A11   | D1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_A12   | E2  | 1      |                 |             |                                                                                                                                                                                |

| MEM_BA0   | J1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_BA1   | J2  | 1      | O <sub>s</sub>  | MEM_CLK     | DDR memory, Bank Select.                                                                                                                                                       |

| MEM_RASZ  | D3  | 1      | Os              | MEM_CLK     | DDR memory, Row Address Strobe (Active low).                                                                                                                                   |

| MEM_CASZ  | J3  | 1.80 V | Os              | MEM_CLK     | DDR memory, Column Address Strobe (Active low).                                                                                                                                |

| MEM_WEZ   | C2  | 1.00 V | Os              | MEM_CLK     | DDR memory, Write Enable (Active low).                                                                                                                                         |

| MEM_CSZ   | K2  |        | O <sub>s</sub>  | MEM_CLK     | DDR memory, Chip Select (Active low).                                                                                                                                          |

| MEM_CKE   | K1  | 1      | Os              | MEM_CLK     | DDR memory, Clock Enable (Active high).                                                                                                                                        |

| MEM_ODT   | E4  |        | O <sub>s</sub>  | MEM_CLK     | DDR memory, On die termination (ODT). ODT is not verified and supported operational mode. This pin should be left open or connected to corresponding DDR2 pin.                 |

| MEM_RST   | C3  |        | Os              | MEM_CLK     | DDR memory, Reset. Do Not connect.                                                                                                                                             |

| MEM_ZQ    | J4  |        | Os              | MEM_CLK     | DDR memory, External pad where to connect the external impedance calibration resistor. The user connects the PAD pin through an external 240 $\Omega$ ± 1% resistor to ground. |

| MEM_DQS0  | N1  | 1      | B <sub>SD</sub> | N/A         | DDR memory, Lower Byte, R/W Data Strobe.                                                                                                                                       |

| MEM_DQSZ0 | N2  | 1      | B <sub>SD</sub> | N/A         | DDR memory, Lower Byte, R/W Data Strobe, inverted.                                                                                                                             |

| MEM_DQ0   | P2  | 1      |                 |             |                                                                                                                                                                                |

| MEM_DQ1   | R1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_DQ2   | P1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_DQ3   | M2  |        |                 | MEM DOCC    | DDD mamon, Lawer Bute, Biding History J. DAM Date                                                                                                                              |

| MEM_DQ4   | L3  | 1      | B <sub>s</sub>  | MEM_DQS0    | DDR memory, Lower Byte, Bidirectional R/W Data.                                                                                                                                |

| MEM_DQ5   | M1  | 1      |                 |             |                                                                                                                                                                                |

| MEM_DQ6   | L2  | 1      |                 |             |                                                                                                                                                                                |

| MEM_DQ7   | L1  | 1      |                 |             |                                                                                                                                                                                |

PIN I/O I/O CLOCK **SYSTEM** NAME NO. **POWER TYPE DESCRIPTION** MEM DQS1 R4  $\mathsf{B}_\mathsf{s}$ N/A DDR memory, Upper Byte, R/W Data Strobe. MEM\_DQSZ1 T4  $\mathsf{B}_{\mathsf{SD}}$ N/A DDR memory, Upper Byte, R/W Data Strobe, inverted. MEM\_DQ8 T6 MEM\_DQ9 R6 MEM\_DQ10 T5 1.80 V MEM\_DQ11 R5  $B_s$ MEM\_DQS1 DDR memory, Upper Byte, Bidirectional R/W Data. MEM\_DQ12 P5 MEM\_DQ13 Т3 MEM\_DQ14 T2 MEM\_DQ15 R3

### **Board Level Test and Debug**

| PIN I/O  |     | I/O    | I/O            | CLOCK   |                                                                                                                                                                                                                                |

|----------|-----|--------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | POWER  | TYPE           | SYSTEM  | DESCRIPTION                                                                                                                                                                                                                    |

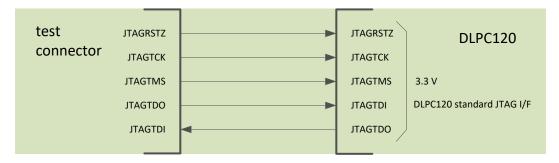

| JTAGRSTZ | J13 |        | l <sub>2</sub> | Async   | JTAG, Reset. Includes weak internal pull-up. Holds TAP controller and associated JTAG logic in idle state under normal operation. This pin should be pulled down with a 5 k $\Omega$ or smaller resistor for normal operation. |

| JTAGTDI  | K15 | 3.30 V | l <sub>2</sub> | JTAGTCK | JTAG, Serial Data In. Includes weak internal pull-up.                                                                                                                                                                          |

| JTAGTCK  | L15 |        | l <sub>2</sub> | N/A     | JTAG, Serial Data Clock. Includes weak internal pull-up.                                                                                                                                                                       |

| JTAGTMS  | L16 |        | l <sub>2</sub> | JTAGTCK | JTAG, Test Mode Select. Includes weak internal pull-up.                                                                                                                                                                        |

| JTAGTDO  | K14 |        | O <sub>6</sub> | JTAGTCK | JTAG, Serial Data Out.                                                                                                                                                                                                         |

### **Manufacturing Test Support**

| PIN       |     | I/O    | I/O            | CLOCK  |                                                                                                                                   |

|-----------|-----|--------|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. | POWER  | TYPE           | SYSTEM | DESCRIPTION                                                                                                                       |

| HWTEST_EN | G16 | 3.30 V | l <sub>2</sub> | N/A    | Manufacturing Test Enable signal. Should be connected directly to ground on the PCB for normal operation. Weak Internal Pulldown. |

| MEM_ATO   | K3  | N/A    | 0              | N/A    | Memory Controller Analog Test Output. Factory Test purposes only, should be left unconnected in system.                           |

| MEM_DTO0  | M4  | 3.30 V | Os             | N/A    | Memory Controller Digital Test Output #1. Factory Test purposes only, should be left unconnected in system.                       |

| MEM_DTO1  | N4  | 3.30 V | O <sub>s</sub> | N/A    | Memory Controller Digital Test Output #2. Factory Test purposes only, should be left unconnected in system.                       |

### **Test Point Interface**

| PIN     |     | I/O    | I/O    | CLOCK  |                                                                                                                            |                |                |                |       |                                                              |

|---------|-----|--------|--------|--------|----------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|-------|--------------------------------------------------------------|

| NAME    | NO. | POWER  | TYPE   | SYSTEM | DESCRIPTION                                                                                                                |                |                |                |       |                                                              |

| TSTPT_0 | K16 |        |        |        |                                                                                                                            |                |                |                |       |                                                              |

| TSTPT_1 | J14 |        |        |        |                                                                                                                            |                |                |                |       |                                                              |

| TSTPT_2 | J15 |        |        |        | Reserved for Test Outputs. These test I/O should be left open or unconnected for normal operation in final product design. |                |                |                |       |                                                              |

| TSTPT_3 | J16 | 3.30 V | 3.30 V | 3.30 V | B <sub>8</sub>                                                                                                             | B <sub>8</sub> | B <sub>8</sub> | B <sub>8</sub> | Async | (DO NOT tie to GND), Internal Pullup on all signals. TSTPT_4 |

| TSTPT_4 | H16 |        |        |        | should be pulled up using external 10 kΩ resistor to ensure proper initialization.                                         |                |                |                |       |                                                              |

| TSTPT_5 | H15 |        |        |        | propor minanzation.                                                                                                        |                |                |                |       |                                                              |

| TSTPT_6 | H12 |        |        |        |                                                                                                                            |                |                |                |       |                                                              |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

| PIN             |     | I/O    | I/O            | CLOCK  |                                                                                                                                                                                                                                     |

|-----------------|-----|--------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | POWER  | TYPE           | SYSTEM | DESCRIPTION                                                                                                                                                                                                                         |

| TSTPT_7 (CM_DM) | H14 | 3.30 V | В <sub>8</sub> | Async  | This pin is configured by default to indicate whether the system is in Continuous Mode (High) or Discontinuous Mode (Low). Contact a TI Applications Engineer for implementation details. It can also be reserved as a Test Output. |

### **Power and Ground**

|           | PIN                                                                                                                   | I/O |                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------|

| NAME      | NO.                                                                                                                   | 1/0 | DESCRIPTION                                                                         |

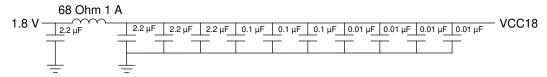

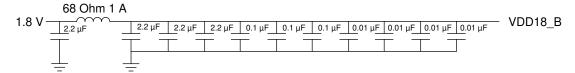

| VCCIO_1   | B2, D4, G4, K4, M3, N5, P3, R7                                                                                        | PWR | 1.8 V (DDR2 MEM).                                                                   |

| VCCIO_2   | BA2, D10, D12, D6, D8                                                                                                 | PWR | 1.8 V (DMD I/F).                                                                    |

| VCCIO_3   | B15, E12, L14, N10, P13                                                                                               | PWR | 3.3 V (MISC IO).                                                                    |

| MEM_VREF0 | H4                                                                                                                    |     | Voltage Referenced Input (50% of DDR Memory Voltage).                               |

| MEM_VREF1 | N6                                                                                                                    |     | Voltage Referenced Input (50% of DDR Memory Voltage).                               |

| VCCA      | G12                                                                                                                   | PWR | PLL Power Input.                                                                    |

| VSSA      | F12                                                                                                                   |     | PLL R-C Return Path (NOT a GND).                                                    |

| VDD       | G8, G9, H7, H10, J7, J10, K8, K9                                                                                      | PWR | 1.2-V core logic power supply.                                                      |

| VDDQ      | J12                                                                                                                   | GND | EFUSE Programming voltage (Used in Manufacturing Test only.) Should be tied to GND. |

| GND       | A1, A16, B3, C6, C9, C12, E3, G7, G10, H3, H8, H9, J8, J9, K7, K10, K12, L4, N3, N7, N14, P4, P6, P9, R2, T1, T7, T16 | GND | Common Ground (I/O Ground).                                                         |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

GND

Ground return

Table 5-2. I/O Type Subscript Definition

| Table 3-2. I/O Type Subscript Definition |                      |                   |  |  |  |  |

|------------------------------------------|----------------------|-------------------|--|--|--|--|

|                                          | I/O                  | SUPPLY REFERENCE  |  |  |  |  |

| SUBSCRIPT                                | DESCRIPTION          | SOFFEI KEI EKENGE |  |  |  |  |

| 1                                        | 1.8 V                | VDD               |  |  |  |  |

| 2                                        | 3.3 V                | VCCIO_3           |  |  |  |  |

| 4                                        | 8 mA                 | VDD               |  |  |  |  |

| 5                                        | 6, 10, or 12 mA      | VCCIO_2           |  |  |  |  |

| 6                                        | 8 mA                 | VCCA              |  |  |  |  |

| S                                        | SSTL_18              | VCCIO_1           |  |  |  |  |

| 8                                        | 8 mA                 | VCCIO_3           |  |  |  |  |

| SD                                       | SSTL_18 Differential | VCCIO_1           |  |  |  |  |

| TYPE                                     |                      |                   |  |  |  |  |

| I                                        | Input                |                   |  |  |  |  |

| 0                                        | Output               |                   |  |  |  |  |

| В                                        | Bidirectional        | N/A               |  |  |  |  |

| PWR                                      | Power                |                   |  |  |  |  |

### Table 5-3. Internal Pullup and Pulldown Characteristics

| INTERNAL PULL-UP AND PULL-DOWN RESISTOR CHARACTERISTICS | VCCIO | MIN | ТҮР | MAX | UNIT |

|---------------------------------------------------------|-------|-----|-----|-----|------|

| Weak pull-up resistance                                 | 3.3 V | 27  | 39  | 61  | kΩ   |

| Weak pull-down resistance                               | 3.3 V | 32  | 46  | 79  | kΩ   |

| weak pull-down resistance                               | 1.8 V | 52  | 91  | 180 | kΩ   |

### **6 Specifications**

### **6.1 Absolute Maximum Ratings**

over operating free-air temperature (unless otherwise noted) (1)

|                                               | MIN | MAX  | UNIT |

|-----------------------------------------------|-----|------|------|

| SUPPLY VOLTAGE <sup>(2)</sup>                 |     |      |      |

| VCCIO_1                                       | 0   | 1.98 | V    |

| VCCIO_2                                       | 0   | 3.6  | V    |

| VCCIO_3                                       | 0   | 3.6  | V    |

| VCCA (PLL)                                    | 0   | 1.32 | V    |

| VDD                                           | 0   | 1.32 | V    |

| GENERAL                                       |     |      |      |

| T <sub>J</sub> Operating junction temperature | -40 | 125  | °C   |

| T <sub>stg</sub> Storage temperature          | -40 | 150  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                                            |                                          |                                     |          | VALUE | UNIT |

|--------------------------------------------|------------------------------------------|-------------------------------------|----------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 | ±2000                               |          |       |      |

|                                            | Flectrostatic discharge                  | Charged device model (CDM), per AEC | All pins | ±500  | V    |

|                                            | Q 100-011                                | Corner pins (A1, A16, T1, and T16)  | ±750     |       |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                                              | MIN   | NOM | MAX   | UNIT |

|----------------|----------------------------------------------|-------|-----|-------|------|

| VDD            | 1.2-V supply voltage, core logic             | 1.14  | 1.2 | 1.26  | V    |

| VCCA           | Analog voltage for PLL                       | 1.14  | 1.2 | 1.26  | V    |

| VCCIO_0        | DDR2 memory interface                        | 1.71  | 1.8 | 1.89  | V    |

| VCCIO_1        | 1.8-V supply voltage for DMD                 | 1.71  | 1.8 | 1.89  | V    |

| VCCIO_2        | Pixel interface supply voltage               | 3.135 | 3.3 | 3.465 | V    |

| VDDQ           | EFuse programming voltage                    | 0.0   | 0.0 | 0.0   | V    |

| T <sub>J</sub> | Operating junction temperature               | -40   |     | 125   | °C   |

| T <sub>A</sub> | Operating ambient temperature <sup>(1)</sup> | -40   |     | 105   | °C   |

<sup>(1)</sup> Operating ambient temperature is dependent on system thermal design. Operating junction temperature may not exceed its specified range across ambient temperature conditions.

### 6.4 Thermal Information

|                                                      | DLPC120-Q1 |      |

|------------------------------------------------------|------------|------|

| THERMAL METRIC <sup>(1)</sup>                        | ZXS (BGA)  | UNIT |

|                                                      | 216 PINS   |      |

| ψ <sub>JT</sub> Case-to-junction thermal coefficient | 0.28       | °C/W |

Submit Document Feedback

<sup>(2)</sup> All voltage values are with respect to GND.

### 6.4 Thermal Information (continued)

|          |                                         | DLPC120-Q1 |      |

|----------|-----------------------------------------|------------|------|

|          | THERMAL METRIC(1)                       | ZXS (BGA)  | UNIT |

|          |                                         | 216 PINS   |      |

| $T_{JA}$ | Junction-to-ambient thermal coefficient | 26.32      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the , Semiconductor and IC Package Thermal Metrics Application Report (SPRA953).

### **6.5 Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------|-----------------|-----|-----|-----|------|

| I <sub>VDD</sub>       | Logic core power (1.2 V)                        |                 |     | 140 | 186 | mA   |

| I <sub>VCCA</sub>      | PLL power (1.2 V)                               |                 |     | 3   | 10  | mA   |

| I <sub>VCCIO_0/1</sub> | DDR2 memory and DMD interface I/O power (1.8 V) |                 |     | 180 | 245 | mA   |

| I <sub>VCCIO_2</sub>   | Pixel data input power (3.3 V)                  |                 |     | 4   | 10  | mA   |

|                        | Total power                                     |                 |     | 469 | 724 | mW   |

### 6.6 Electrical Characteristics for I/O

|                 |                                   | PARAMETER                                  | TEST CONDITIONS | MIN          | TYP MAX     | UNIT |

|-----------------|-----------------------------------|--------------------------------------------|-----------------|--------------|-------------|------|

|                 | High-level                        | 1.8-V LVCMOS (I/O Type 1)                  |                 | 1.17         | VCCIO + 0.3 |      |

| V <sub>IH</sub> | input<br>threshold                | 3.3-V LVCMOS (I/O Type 2, 8)               |                 | 2.0          | VCCIO + 0.3 | V    |

|                 | voltage                           | SSTL_18 (I/O Type S, SD)                   |                 | 1.08         | VCCIO + 0.3 |      |

|                 | Low-level input threshold voltage | 1.8-V LVCMOS (I/O Type 1)                  |                 | -0.3         | 0.63        |      |

| V <sub>IL</sub> |                                   | 3.3-V LVCMOS (I/O Type 2, 8)               |                 | -0.3         | 0.8         | V    |

|                 |                                   | SSTL_18 (I/O Type S, SD)                   |                 | -0.3         | 0.73        |      |

|                 |                                   | 1.8-V LVCMOS fixed current (I/O Type 4)    |                 | 1.35         |             |      |

| V <sub>OH</sub> | High-level output                 | 1.8-V LVCMOS variable current (I/O Type 5) |                 | 1.35         |             | V    |

|                 | voltage                           | 3.3-V LVCMOS fixed current (I/O Type 6, 8) |                 | 2.4          |             |      |

|                 |                                   | SSTL_18 (I/O Type S, SD)                   |                 | VCCIO - 0.28 |             |      |

|                 |                                   | 1.8-V LVCMOS fixed current (I/O Type 4)    |                 |              | 0.45        |      |

| V <sub>OL</sub> | Low-level output                  | 1.8-V LVCMOS variable current (I/O Type 5) |                 |              | 0.45        | V    |

|                 | voltage                           | 3.3-V LVCMOS fixed current (I/O Type 6, 8) |                 |              | 0.4         |      |

|                 |                                   | SSTL_18 (I/O Type S, SD)                   |                 |              | 0.28        |      |

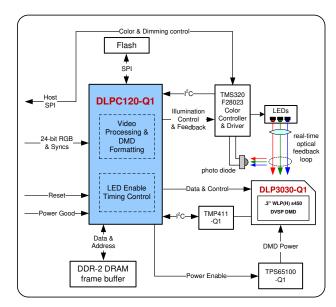

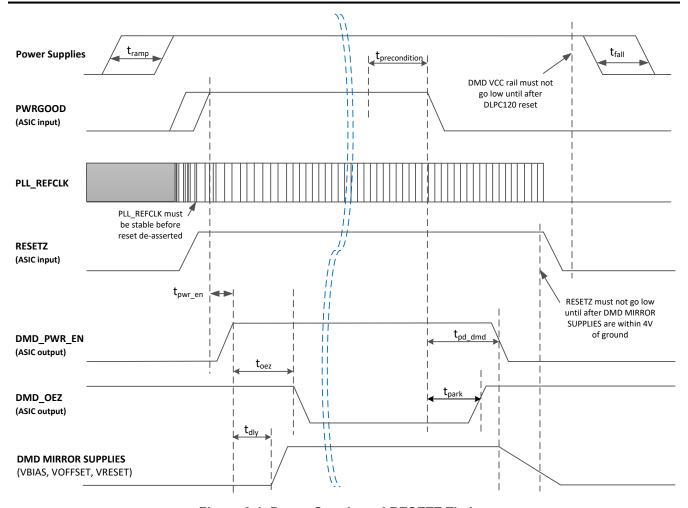

### 6.7 Power Supply and Reset Timing Requirements

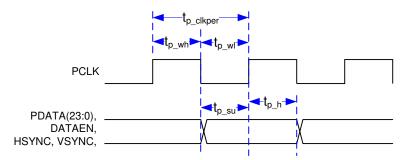

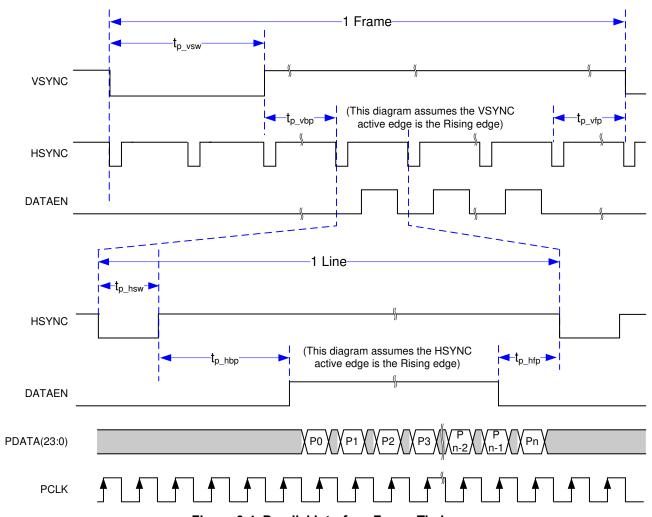

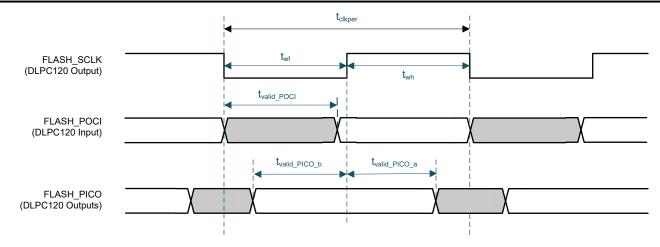

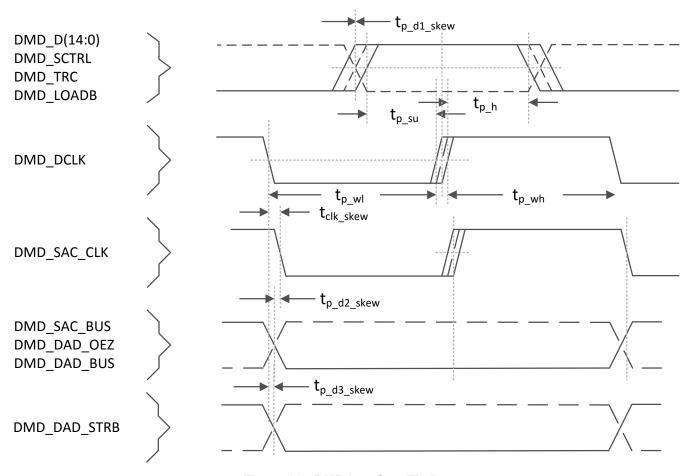

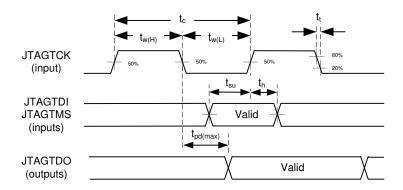

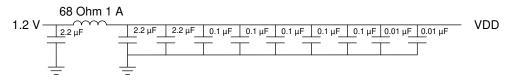

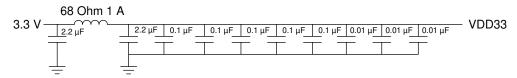

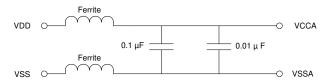

|                     |                                                                                              |                                                                                                                                                                                | MIN | MAX | UNIT |