DAC8581

SLAS481C - AUGUST 2005-REVISED OCTOBER 2012

www.ti.com

# 16-BIT, HIGH-SPEED, LOW-NOISE, VOLTAGE OUTPUT DIGITAL-TO-ANALOG CONVERTER

Check for Samples: DAC8581

#### **FEATURES**

- **16-Bit Monotonic**

- ±5-V Bipolar Output

- Very Low Glitch: 0.5 nV-s

- Fast Settling: 0.65 µs

- Fast Slew Rate: 35 V/µs

- Low Noise: 20 nV/√Hz

- ±25-mA Load Drive

- ±5-V Dual Power Supply

- **Single External Reference**

- **Power-On Reset to Midscale**

- 3-MSPS Update Rate

- SPI™ Interface, Up to 50 MHz

- 1.8-V-5-V Logic Compatible

- **Twos Complement Data Format**

- **Hardware Reset to Midscale**

- TSSOP-16 Package

#### **APPLICATIONS**

- **Industrial Process Control**

- **CRT Projection TV Digital Convergence**

- **Waveform Generation**

- **Automated Test Equipment**

- **Ultrasound**

# DESCRIPTION

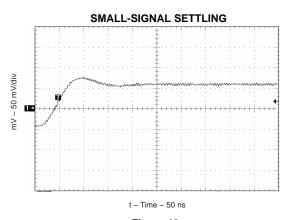

The DAC8581 is a 16-bit, high-speed, low-noise DAC operating from dual ±5-V power supplies. The DAC8581 is monotonic, and has exceptionally low noise and exceptionally low glitch. The DAC8581 high-performance, bipolar output buffer is capable of settling within 0.65 µs for a 10-V step. Small-signal settling time is well under 0.3 µs, supporting data update rates up to 3 MSPS. A power-on-reset circuit sets the output at midscale voltage on power up.

The DAC8581 is simple to use, with a single external reference and a standard 3-wire SPI interface that allows clock rates up to 50 MHz.

Also see the DAC8580, a member of the same family. The DAC8580 combines DAC8581 performance with an on-chip, 16x over-sampling digital filter.

The DAC8581 is specified over the -40°C to +85°C temperature range.

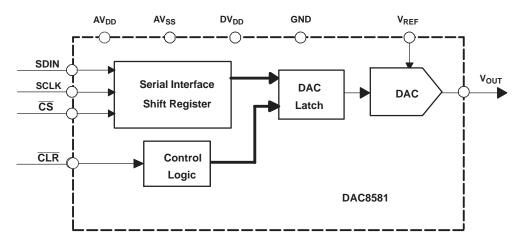

#### **FUNCTIONAL BLOCK DIAGRAM OF DAC8581**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI is a trademark of Motorola.

All other trademarks are the property of their respective owners.

#### DAC8581

SLAS481C - AUGUST 2005-REVISED OCTOBER 2012

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT | PACKAGE  | PACKAGE<br>DRAWING<br>NUMBER | SPECIFICATION<br>TEMPERATURE<br>RANGE | PACKAGE<br>ORDERING<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|---------|----------|------------------------------|---------------------------------------|--------------------------------|--------------------|------------------------------|

| DAC8581 | TSSOP-16 | PW                           | -40°C to +85°C                        | D8581I                         | DAC8581IPW         | Tube, 90-Piece               |

| DAC6561 | 1330P-16 | PVV                          | -40°C 10 +65°C                        | D02011                         | DAC8581IPWR        | Tape and Reel, 2000-Piece    |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

## ABSOLUTE MAXIMUM RATINGS(1)

|                                                          |                                      | UNIT            |

|----------------------------------------------------------|--------------------------------------|-----------------|

| AV <sub>DD</sub> or DV <sub>DD</sub> to AV <sub>SS</sub> |                                      | -0.3 V to 12 V  |

| Digital input voltage to AV <sub>SS</sub>                |                                      | -0.3 V to 12 V  |

| V <sub>OUT</sub> or V <sub>REF</sub> to AV <sub>SS</sub> |                                      | -0.3 V to 12 V  |

| DGND and AGND to AV <sub>SS</sub>                        |                                      | −0.3 V to 6 V   |

| Operating temperature range                              |                                      | -40°C to +85°C  |

| Storage temperature range                                |                                      | −65°C to +150°C |

| Junction temperature range (T <sub>J</sub> max           | ()                                   | +150°C          |

| Paragraphic in all an                                    | Thermal impedance (θ <sub>JA</sub> ) | 118°C/W         |

| Power dissipation                                        | Thermal impedance (θ <sub>JC</sub> ) | 29°C/W          |

<sup>(1)</sup> Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

www.ti.com

SLAS481C - AUGUST 2005 - REVISED OCTOBER 2012

### **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $+AV_{DD} = +5$  V,  $-AV_{DD} = -5$  V,  $DV_{DD} = +5$  V (unless otherwise noted).

| PARAMETER                     | TEST CONDITIONS                                                                                     | MIN               | TYP   | MAX                    | UNIT               |

|-------------------------------|-----------------------------------------------------------------------------------------------------|-------------------|-------|------------------------|--------------------|

| STATIC PERFORMANCE            |                                                                                                     | *                 |       | ·                      |                    |

| Resolution                    |                                                                                                     | 16                |       |                        | Bits               |

| Linearity error               | V <sub>REF</sub> = 4.096 V                                                                          |                   | ±0.03 | ±0.1                   | %FS                |

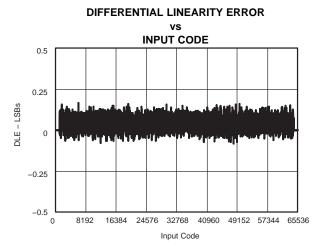

| Differential linearity error  |                                                                                                     |                   | ±0.25 | ±0.5                   | LSB                |

| Gain error                    |                                                                                                     | 1                 | 2     | 3                      | %FS                |

| Gain drift                    |                                                                                                     |                   | ±5    |                        | ppm/°C             |

| Bipolar zero error            |                                                                                                     |                   | -5    | ±25                    | mV                 |

| Bipolar zero drift            |                                                                                                     |                   | ±20   |                        | μV/°C              |

| Total drift                   |                                                                                                     |                   | ±10   |                        | ppm/°C             |

| OUTPUT CHARACTERISTICS        |                                                                                                     |                   |       | -                      |                    |

| Voltage output                | $V_{REF}$ up to 5.5 V, when $AV_{DD} = 6$ V, $AV_{SS} = -6$ V                                       | -V <sub>REF</sub> |       | $V_{REF}$              | V                  |

| Output impedance              |                                                                                                     |                   | 1     |                        | Ω                  |

| Maximum output current        |                                                                                                     |                   | ±25   |                        | mA                 |

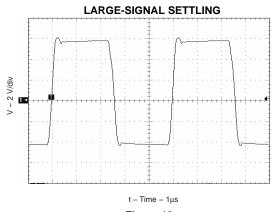

| 0.00                          | $C_L < 200 \text{ pF}, R_L = 2 \text{ k}\Omega, \text{ to } 0.1\% \text{ FS}, 8-\text{V step}$      |                   | 0.65  |                        |                    |

| Settling time                 | To 0.003% FS                                                                                        |                   | 1     |                        | μs                 |

| Slew rate <sup>(1)</sup>      |                                                                                                     |                   | 35    |                        | V/µs               |

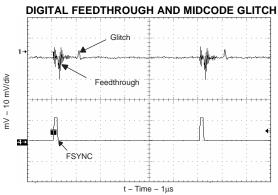

| Code change glitch            | 1 LSB change around major carry                                                                     |                   | 0.5   |                        | nV-S               |

| Overshoot                     | Full-scale change                                                                                   |                   | 50    |                        | mV                 |

| Digital feedthrough (2)       |                                                                                                     |                   | 0.5   |                        | nV-S               |

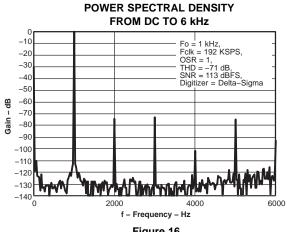

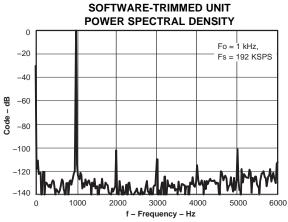

| SNR                           | Digital sine wave input, f <sub>OUT</sub> = 1 kHz,<br>BW = 10 kHz, 2-MSPS update rate               |                   | 108   |                        | dB                 |

| THD                           | Digital sine wave input, f <sub>OUT</sub> = 20 kHz,<br>8-V <sub>PP</sub> output, 2-MSPS update rate |                   | -72   |                        | dB                 |

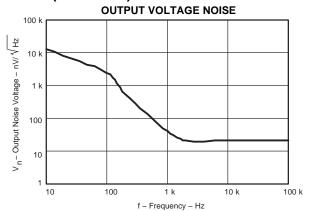

|                               | 0.1 Hz to 10 Hz                                                                                     |                   | 25    |                        | $\mu V_{PP}$       |

| Output voltage noise          | At 10-kHz offset frequency                                                                          |                   | 25    |                        | nV/√ <del>Hz</del> |

|                               | At 100-kHz offset frequency                                                                         |                   | 20    |                        | nV/√ <del>Hz</del> |

| Power supply rejection        | VDD varies ±10%                                                                                     |                   | 0.75  |                        | mV/V               |

| REFERENCE                     |                                                                                                     |                   |       |                        |                    |

| Defenses in set handwidth     | Large signal: 2-V <sub>PP</sub> sine wave on 4 V DC                                                 |                   | 3     |                        | MHz                |

| Reference input bandwidth     | Small signal: 100-mV <sub>PP</sub> sine wave on 4 V DC                                              |                   | 10    |                        | MHz                |

| Reference input voltage range |                                                                                                     | 3                 |       | $AV_{DD}$              | V                  |

| Reference input impedance     |                                                                                                     |                   | 5     |                        | kΩ                 |

| Reference input capacitance   |                                                                                                     |                   | 5     |                        | pF                 |

| DIGITAL INPUTS                |                                                                                                     |                   |       |                        |                    |

| V <sub>IH</sub>               |                                                                                                     |                   |       | 0.7 x DV <sub>DD</sub> | V                  |

| $V_{IL}$                      |                                                                                                     | GND               |       | 0.3 x DV <sub>DD</sub> | V                  |

| Input current                 |                                                                                                     |                   |       | ±1                     | μA                 |

| Input capacitance             |                                                                                                     |                   |       | 10                     | pF                 |

| Power-on delay                | From V <sub>DD</sub> high to $\overline{\text{CS}}$ low                                             |                   | 20    |                        | μs                 |

<sup>(1)</sup> Slew rate is measured from 10% to 90% of transition when the output changes from 0 to full-scale.

<sup>(2)</sup> Digital feedthrough is defined as the impulse injected into the analog output from the digital input. It is measured when the DAC output does not change, CS is held high, and while SCLK and SDIN signals are toggled.

TEXAS INSTRUMENTS

SLAS481C - AUGUST 2005 - REVISED OCTOBER 2012

www.ti.com

## **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ , +AV<sub>DD</sub> = +5 V, -AV<sub>DD</sub> = -5 V, DV<sub>DD</sub> = +5 V (unless otherwise noted).

|                       |                                                 |      | DAC8581    |         |      |  |

|-----------------------|-------------------------------------------------|------|------------|---------|------|--|

| PARAMETER             | TEST CONDITIONS                                 | MIN  | TYP MAX    |         | UNIT |  |

| POWER SUPPLY          | •                                               |      | •          |         |      |  |

| +AV <sub>DD</sub>     |                                                 | 4.0  | 5          | 6.0     | V    |  |

| -AV <sub>DD</sub>     |                                                 | -4.0 | <b>-</b> 5 | -6.0    | V    |  |

| $DV_DD$               |                                                 | 1.8  |            | $AV_DD$ | V    |  |

| $I_{DVDD}$            |                                                 |      | 10         | 20      | μΑ   |  |

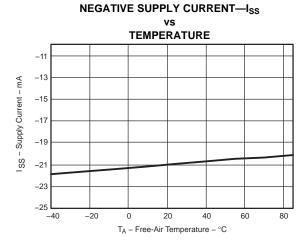

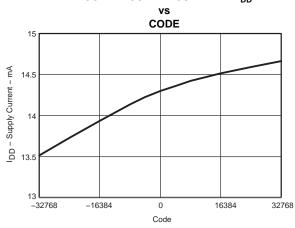

| $I_{DD}$              | I <sub>REF</sub> and IDV <sub>DD</sub> included |      | 17         | 24      | mA   |  |

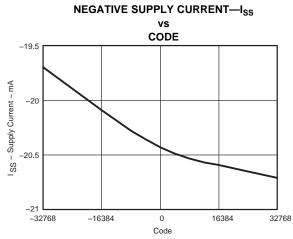

| I <sub>SS</sub>       |                                                 |      | -23        | -32     | mA   |  |

| TEMPERATURE RANGE     | ·                                               |      |            |         |      |  |

| Specified performance |                                                 | -40  |            | +85     | °C   |  |

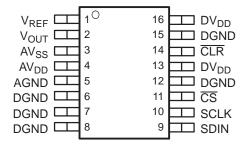

### **PIN CONFIGURATION**

#### PW PACKAGE TSSOP-16 (TOP VIEW)

## **TERMINAL FUNCTIONS**

| TERMINAL         |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>REF</sub> | 1           | Reference input voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VOUT             | 2           | DAC output voltage. Output swing is ±V <sub>REF</sub>                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AV <sub>SS</sub> | 3           | Negative analog supply voltage, tie to -5 V                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $AV_{DD}$        | 4           | Positive analog supply voltage, tie to +5 V                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AGND             | 5           | The ground reference point of all analog circuitry of the device. Tie to 0 V.                                                                                                                                                                                                                                                                                                                                                                                              |

| DGND             | 6, 7, 8, 15 | Tie to DGND to ensure correct operation.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SDIN             | 9           | Digital input, serial data. Ignored when $\overline{\text{CS}}$ is high.                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCLK             | 10          | Digital input, serial bit clock. Ignored when $\overline{\text{CS}}$ is high.                                                                                                                                                                                                                                                                                                                                                                                              |

| <del>CS</del>    | 11          | Digital input. Chip Select ( $\overline{CS}$ ) signal. Active low. When $\overline{CS}$ is high, SCLK and SDI are ignored. When $\overline{CS}$ is low, data can be transferred into the device.                                                                                                                                                                                                                                                                           |

| DGND             | 12          | Ground reference for digital circuitry. Tie to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $DV_DD$          | 13          | Positive digital supply, 1.8 V–5.5 V compatible                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLR              | 14          | Digital input for forcing the output to midscale. Active low. When pin $\overline{\text{CLR}}$ is low during 16 <sup>th</sup> SCLK following the falling edge of $\overline{\text{CS}}$ , the falling edge of 16 <sup>th</sup> SCLK sets DAC Latch to midcode, and the DAC output to 0 V. When pin $\overline{\text{CLR}}$ is High, the falling edge of 16th SCLK updates DAC latch with the value of input shift register, and changes DAC output to corresponding level. |

| $DV_DD$          | 16          | Tie to DV <sub>DD</sub> to ensure correct operation.                                                                                                                                                                                                                                                                                                                                                                                                                       |

www.ti.com

## SLAS481C - AUGUST 2005 - REVISED OCTOBER 2012

## TIMING REQUIREMENTS(1)

|                    | PARAMETER                                          | MIN MA | UNIT |

|--------------------|----------------------------------------------------|--------|------|

| t <sub>SCK</sub>   | SCLK period                                        | 20     | ns   |

| t <sub>WSCK</sub>  | SCLK high or low time                              | 10     | ns   |

| t <sub>Lead</sub>  | Delay from falling CS to first rising SCLK         | 20     | ns   |

| t <sub>TD</sub>    | CS High between two active Periods                 | 20     | ns   |

| t <sub>SU</sub>    | Data setup time (Input)                            | 5      | ns   |

| t <sub>H</sub> I   | Data hold time (input)                             | 5      | ns   |

| t <sub>R</sub>     | Rise time                                          | 3      | ) ns |

| t <sub>F</sub>     | Fall time                                          | 3      | ) ns |

| t <sub>WAIT</sub>  | Delay from 16th falling edge of SCLK to CS low     | 100    | ns   |

| t <sub>UPDAC</sub> | Delay from 16th falling edge of SCLK to DAC output | 1      | μs   |

|                    | V <sub>DD</sub> High to CS Low (power-up delay)    | 100    | μs   |

## (1) Assured by design. Not production tested.

Figure 1. DAC8581 Timing Diagram

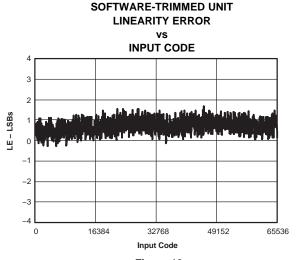

## TYPICAL CHARACTERISTICS

Figure 2.

Figure 3.

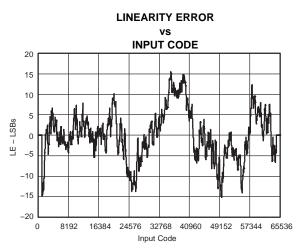

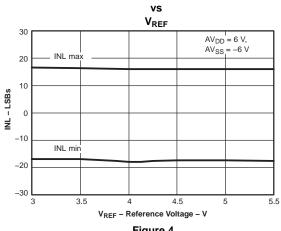

INTEGRAL NONLINEARITY ERROR

### INTEGRAL NONLINEARITY ERROR

Figure 4.

## **SUPPLY VOLTAGE** 30 $AV_{SS} = -AV_{DD}$ , $V_{REF} = AV_{DD} - 0.3 V$ 20 INL max 10 INL - LSBs 0 -10 INL min -20 -30 3.5 AV<sub>DD</sub> – Supply Voltage – V Figure 5.

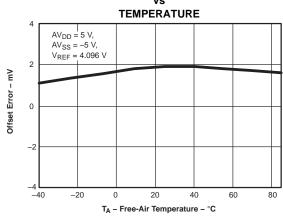

# **OFFSET ERROR**

Figure 6.

Figure 7.

Submit Documentation Feedback

Copyright © 2005-2012, Texas Instruments Incorporated

**NSTRUMENTS**

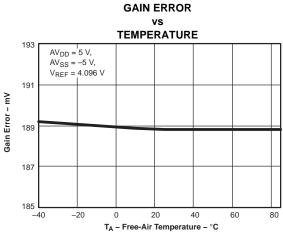

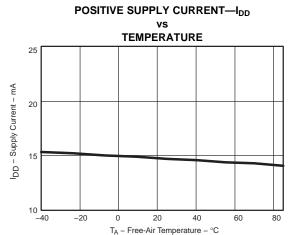

## **TYPICAL CHARACTERISTICS (continued)**

Figure 8.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

Figure 13.

## **TYPICAL CHARACTERISTICS (continued)**

Figure 14.

Figure 15.

Figure 16.

Figure 17.

Figure 18.

**NSTRUMENTS**

#### THEORY OF OPERATION

The DAC8581 uses a proprietary, monotonic, high-speed resistor string architecture. The 16-bit input data are coded in twos complement, MSB-first format and transmitted using a 3-wire serial interface. The serial interface sends the input data to the DAC latch. The digital data are then decoded to select a tap voltage of the resistor string. The resistor string output is sent to a high-performance output amplifier. The output buffer has bipolar ( $\pm$ 5 V) swing capability on a 600- $\Omega$ , 200-pF load. The resistor string DAC architecture provides exceptional differential linearity and temperature stability whereas the output buffer provides fast-settling, low-glitch, and exceptionally low idle-channel noise. The DAC8581 settles within 1  $\mu$ s for large input signals. Exceptionally low glitch (0.5 nV-s) is attainable for small-signal, code-to-code output changes. The resistor string architecture also provides code-independent power consumption and code-independent settling time. The DAC8581 resistor string needs an external reference voltage to set the output voltage range of the DAC. To aid fast settling, V<sub>REF</sub> input is internally buffered.

### **Supply Pins**

The DAC8581 uses  $\pm 5$ -V analog power supplies (AV<sub>DD</sub>, AV<sub>SS</sub>) and a 1.8-V to 5.5-V digital supply (DV<sub>DD</sub>). Analog and digital ground pins (AGND and DGND) are also provided. For low-noise operation, analog and digital power and ground pins should be separated. Sufficient bypass capacitors, at least 1  $\mu$ F, should be placed between AV<sub>DD</sub> and AV<sub>SS</sub>, AV<sub>SS</sub> and DGND, and DV<sub>DD</sub> and DGND pins. Series inductors are *not* recommended on the supply paths. The digital input pins should not exceed the ground potential during power up. During power up, AGND and DGND are first applied with all digital inputs and the reference input kept at 0 V. Then, AV<sub>DD</sub>, DV<sub>DD</sub>, AV<sub>SS</sub>, and V<sub>REF</sub> should be applied together. Care should be taken to avoid applying V<sub>REF</sub> before AV<sub>DD</sub> and AV<sub>SS</sub>. All digital pins must be kept at ground potential before power up.

## **Reference Input Voltage**

The reference input pin  $V_{REF}$  is typically tied to a +3.3-V, +4.096-V, or +5.0-V external reference. A bypass capacitor (0.1  $\mu F$  or less) is recommended, depending on the load-driving capability of the voltage reference. To reduce crosstalk and improve settling time, the  $V_{REF}$  pin is internally buffered by a high-performance amplifier. The  $V_{REF}$  pin has constant 5-k $\Omega$  impedance to AGND. The output range of the DAC8581 is equal to  $\pm V_{REF}$  voltage. The  $V_{REF}$  pin should be powered at the same time, or after the supply pins. REF3133 and REF3140 are recommended to set the DAC8581 output range to  $\pm 3.3$  V and  $\pm 4.096$  V, respectively.

### **Output Voltage**

The input data format is in twos-complement format as shown in Table 1. The DAC8581 uses a high-performance, bipolar output buffer capable of driving a 600- $\Omega$ , 200-pF load with fast 0.65- $\mu$ s settling. The buffer has exceptional noise performance ( $20 \text{ nV}/\sqrt{\text{Hz}}$ ) and fast slew rate ( $35 \text{ V/}\mu$ s). The small-signal settling time is under 300 ns, allowing update rates up to 3 MSPS. Loads of  $50 \Omega$  or  $75 \Omega$  could be driven as long as output current does not exceed  $\pm 25 \text{ mA}$  continuously. Long cables, up to 1 nF in capacitance, can be driven without the use of external buffers. To aid stability under large capacitive loads (>1 nF), a small series resistor can be used at the output.

Table 1. Data Format

|                      | DIGITAL CODE    |      |

|----------------------|-----------------|------|

| DAC OUTPUT           | BINARY          | HEX  |

| +V <sub>REF</sub>    | 01111111111111  | 7FFF |

| +V <sub>REF</sub> /2 | 010000000000000 | 4000 |

| 0                    | 00000000000000  | 0000 |

| -V <sub>REF</sub> /2 | 10111111111111  | BFFF |

| -V <sub>REF</sub>    | 100000000000000 | 8000 |

#### **DAC8581**

SLAS481C - AUGUST 2005 - REVISED OCTOBER 2012

www.ti.com

Glitch area is low at 0.5 nV-s, with peak glitch amplitude under 10 mV, and the glitch duration under 100 ns. Low glitch is obtained for code-to-code (small signal) changes across the entire transfer function of the device. For large signals, settling characteristics of the reference and output amplifiers are observed in terms of overshoot and undershoot.

Combined with ±5-V output range, and extremely good noise performance, the outstanding differential linearity performance of this device becomes significant. That is, each DAC step can be clearly observed at the DAC output, without being corrupted by wideband noise.

#### **SERIAL INTERFACE**

The DAC8581 serial interface consists of the serial data input pin SDIN, bit clock pin SCLK, and chip-select pin,  $\overline{\text{CS}}$ . The serial interface is designed to support the industry standard SPI interface up to 50 MHz. The serial inputs are 1.8-V to 5.5-V logic compatible.

$\overline{\text{CS}}$  operates as an active-low, chip-select signal. The falling edge of  $\overline{\text{CS}}$  initiates the data transfer. Each rising edge of SCLK following the falling edge of  $\overline{\text{CS}}$  shifts the SDIN data into a 16-bit shift register, MSB-first. At the 16th rising edge of SCLK, the shift register becomes full and the DAC data updates on the falling edge that follows the 16th rising edge. After the data update, further clocking gets ignored. The sequence restarts at the next falling edge of  $\overline{\text{CS}}$ . If the  $\overline{\text{CS}}$  is brought high before the DAC data are updated, the data are ignored. See the timing diagram (Figure 1) for details.

#### Pin CLR

Pin CLR is implemented to set the DAC output to 0 V. When the CS pin is low during the 16th SCLK cycle following the falling edge of CS, the falling edge of the 16th SCLK sets the DAC latch to midcode, and the DAC output to 0 V. If the CLR pin is high during the 16th clock, the falling edge of the 16th clock updates the DAC latch with the input data. Therefore, if the CLR pin is brought back to High from Low during serial communication, the DAC output stays at 0 V until the falling edge of the next 16th clock is received. The CLR pin is active low. CLR low does not affect the serial data transfer. The serial data input doe not get interrupted or lost while the output is set at midscale.

#### **SCLK**

This digital input pin is the serial bit-clock. Data are clocked into the device at the rising edge of SCLK.

## CS

This digital input pin is the chip-select signal. When  $\overline{CS}$  is low, the serial port is enabled and data can be transferred into the device. When  $\overline{CS}$  is high, all SCLK and SDIN signals are ignored.

#### SDIN

This digital input is the serial data input. Serial data are shifted on the rising edge of the SCLK when  $\overline{\text{CS}}$  is low.

Copyright © 2005–2012, Texas Instruments Incorporated Product Folder Links: *DAC8581*

#### APPLICATION INFORMATION

#### **IMPROVING DAC8581 LINEARITY USING EXTERNAL CALIBRATION**

At output frequencies up to 50 kHz, DAC8581 linearity error and total harmonic distortion are dominated by resistor mismatches in the string. These resistor mismatches are fairly insensitive to temperature and aging effects and also to reference voltage changes. Therefore, it is possible to use a piece-wise linear (PWL) approximation to cancel linearity errors, and the calibration remains effective for different supply and  $V_{REF}$  voltages, etc. The cancellation of linearity errors also improves the total harmonic distortion (THD) performance. It is possible to improve the integral linearity errors from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm 25$  LSB to  $\pm 1$  LSB and the THD from  $\pm$

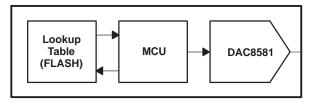

Figure 19. A Simple Printed-Circuit Board Scheme for Calibrated Use of DAC8581

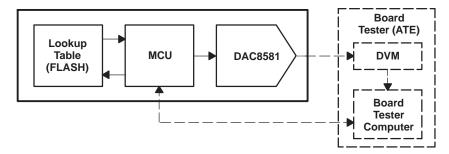

Figure 20. Production Test Setup for a DAC8581 Board With Calibration

The PWL calibration scheme uses a DAC8581 and a microcontroller unit (MCU) with flash memory, on a printed-circuit board as seen in Figure 19. Calibration is done during board test, and the calibration coefficients are stored permanently in flash memory as seen in Figure 20. An automated board tester is assumed to have a precision digital voltmeter (DVM) and a tester computer. The test flow for a 1024-segment, piece-wise linear calibration is as follows:

- 1. Use the tester computer to load software into the MCU to ramp the DAC8581 and:

- Take a reading at each step after a short wait time

- Store 65,536 readings in the tester computer volatile memory

- 2. Use the tester computer to:

- Search the 65,536-point capture data and find the actual DAC8581 codes which would generate ideal DAC outputs for DAC input codes 0, 64, 128, 192, ....

- Store these actual codes in the onboard microcontroller's flash memory in a 1025-point array called COEFF[].

- 3. Use the tester computer to program the MCU such that, when the end-user provides new 16-bit input data D0 to the MCU:

- The 10 MSBs of D0 directly index the array COEFF[].

- The content of indexed memory of COEFF[] and the content of the next higher memory location are placed in variables I1 and I2.

- The six LSBs of the user data D0 with two variables I1 and I2 are used for computing Equation 1 (see Figure 21).

- Instead of D0, I0 is loaded to DAC8581

Figure 21. The Geometry Behind the PWL Calibration

$$I0 = \frac{I1 + (I2 - I1)(D0 - VI1)}{VI2 - VI1}$$

(1)

Where both x-axis and y-axis are normalized from 0 to 65535, and:

- VIO: Desired ideal DAC voltage corresponding to input code D0.

- VIOB: DAC8581 output voltage, which approximates VIO after PWL calibration. This is the actual DAC8581 output for input code D0 after PWL calibration.

- I0: DAC8581 code generating VI0B, an approximation to the desired voltage VI0. This is actual code loaded into DAC latch for input code D0, after PWL calibration.

- I0B: DAC8581 code, which generates output VI0. This code is approximated by the N-segment PWL calibration.

- I1: Contents of memory COEFF[], addressed by the 10 MSBs of user input code D0.

- 12: Contents of the next memory location in COEFF[].

- VI1: DAC8581 output voltage corresponding to code I1. Notice that (D0–VI1) is nothing but the six LSBs of the input code D0, given that the y-axis is normalized from 0 to 65,536.

- VI2: DAC8581 output voltage corresponding to code I2. Notice that (VI2–VI1) is always equal to number 64, given that the y-axis is normalized from 0 to 65,536. Division becomes a 6-bit arithmetic right shift.

Other similar PWL calibration implementations exist. This particular algorithm does not need digital division, and it does not accumulate measurement errors at each segment.

Submit Documentation Feedback

www.ti.com

SLAS481C - AUGUST 2005 - REVISED OCTOBER 2012

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (August, 2005) to      | Revision B                       | Page |

|------------------------------------------------|----------------------------------|------|

| Updated document format to current stylistic   | standards                        | 1    |

| Deleted lead temperature specifications from   | n Absolute Maximum Ratings table | 2    |

| • Deleted footnote 1 from Electrical Character | ristics table                    | 3    |

| Revised test conditions for voltage output sp  | pecification                     | 3    |

| Changes from Revision B (December 2009) t      | o Revision C                     | Page |

| Changed "rail-to-rail" to "bipolar"            |                                  | 1    |

| Changed "rail-to-rail" to "bipolar"            |                                  | 9    |

|                                                |                                  |      |

11-Nov-2025 www.ti.com

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                |              |              |

| DAC8581IPW            | NRND   | Production    | TSSOP (PW)   16 | 90   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | D8581I       |

| DAC8581IPW.B          | NRND   | Production    | TSSOP (PW)   16 | 90   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | D8581I       |

| DAC8581IPWR           | NRND   | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | D8581I       |

| DAC8581IPWR.B         | NRND   | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | D8581I       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

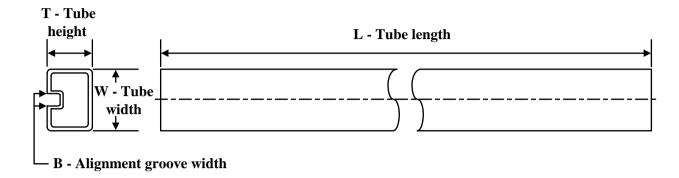

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

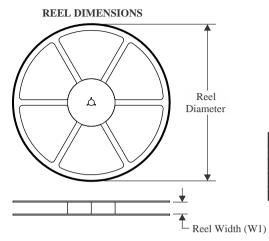

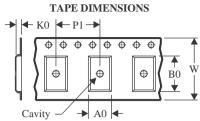

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

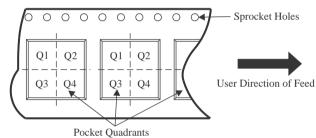

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DAC8581IPWR | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

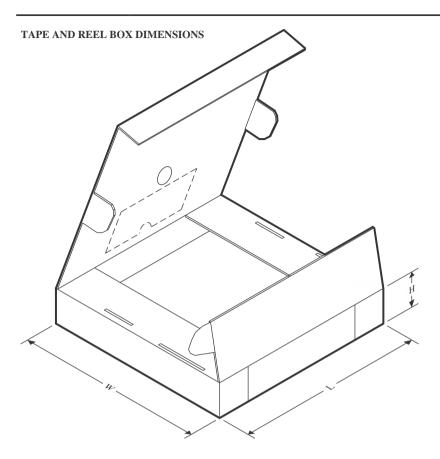

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

### \*All dimensions are nominal

| Ì | Device Package Type |       | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|---------------------|-------|-----------------|------|------|-------------|------------|-------------|

| ı | DAC8581IPWR         | TSSOP | PW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

## **TUBE**

### \*All dimensions are nominal

|   | Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| ĺ | DAC8581IPW   | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600   | 3.5    |

| ĺ | DAC8581IPW.B | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600   | 3.5    |

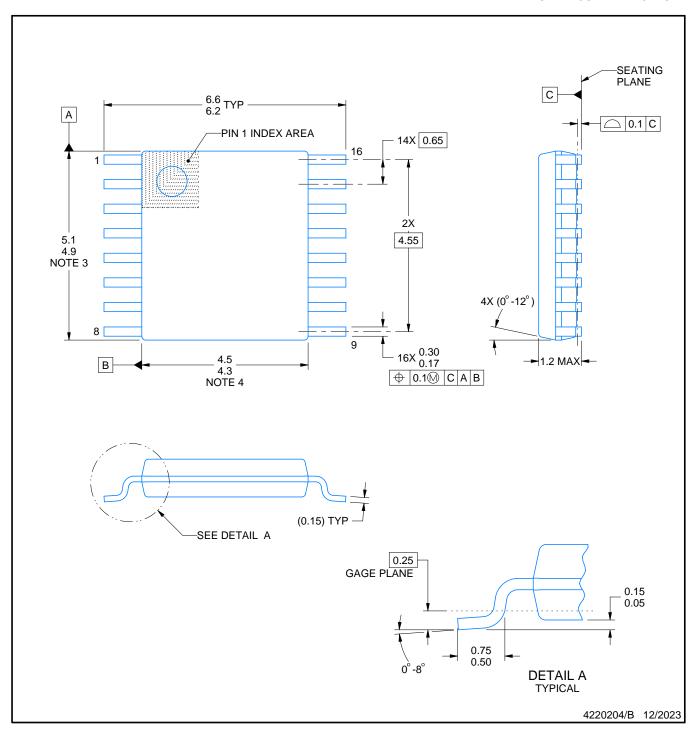

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

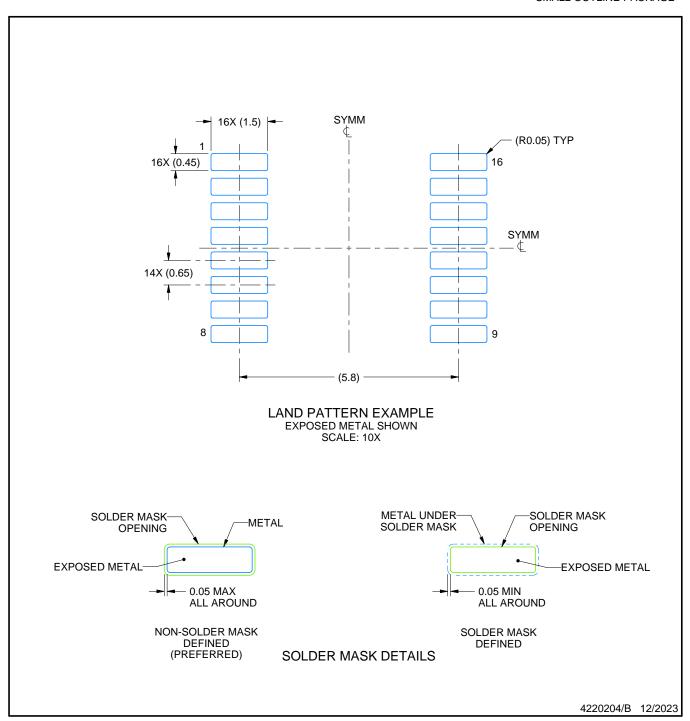

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

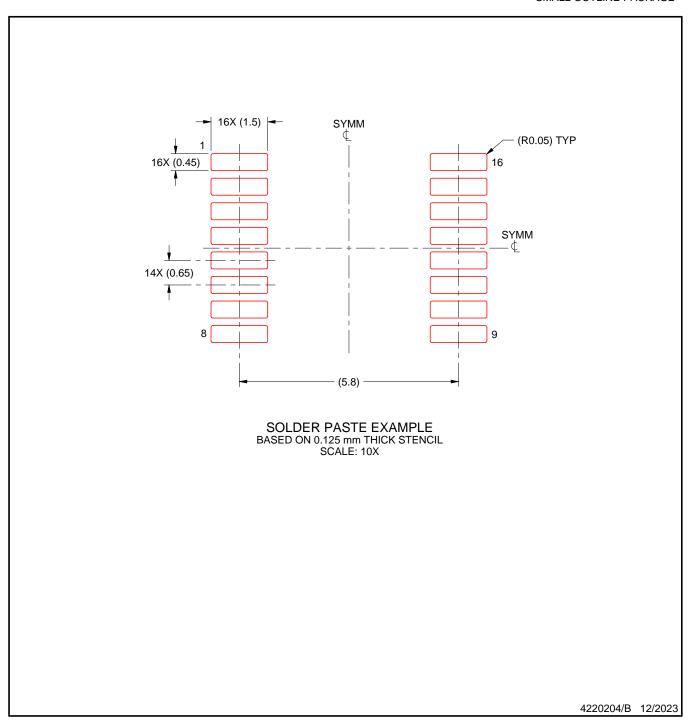

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025