# CC274xR-Q1, CC274xP-Q1 AutomotiveSimpleLink™ Bluetooth® Low Energy Wireless MCU

#### 1 Features

#### Wireless MCU processing elements

- Arm® Cortex®-M33 processor (96MHz) with FPU (floating point unit), TrustZone®-M support, and CDE (custom datapath extension) for machine learning acceleration

- Algorithm Processing Unit (APU) (96MHz)

- Mathematical accelerator for efficient vector and matrix operations

- Bluetooth® Channel Sounding post-processing support for IFFT and advanced superresolution algorithms such as MUltiple SIgnal Classification (MUSIC)

#### Wireless MCU memory

- Up to 1MB of in-system programmable flash

- Up to 162KB of SRAM

- 32KB of System ROM with secure boot root of trust (RoT) and a serial (SPI/UART) bootloader

- Serial wire debug (SWD)

#### Qualified for automotive application

- AEC-Q100 Grade 2 qualified:

- –40°C to +125°C junction temperature

- HBM ESD Classification Level 2 (ESD HBM level 1C on RF pin, per AEC-Q100 Rev. J)

- · CDM ESD Classification Level C2A (ESD CDM level C1 on RF pin, per AEC-Q100 Rev. J)

#### MCU peripherals

- 23 GPIOs, digital peripherals can be routed to multiple GPIOs:

- Two SWD IO pads, multiplexed with GPIOs

- Two LFXT IO pads, multiplexed with GPIOs

- 19 DIOs (analog or digital IOs)

- All GPIOs with wakeup and interrupt capabilities

- $3 \times 16$ -bit and  $1 \times 32$ -bit general-purpose timers, quadrature decode mode support

- Real-time clock (RTC)

- Watchdog timer

- System timer for radio, RTOS, and application operations for Bluetooth® channel sounding postprocessing

- 12-bit ADC, up to 1.2MSPS, eight external inputs

- Temperature sensor and battery monitor

- 1× low-power comparator

- 2× UART with LIN capability

- 2× SPI

- 1× I<sup>2</sup>C

- 1× I<sup>2</sup>S

1× CAN-FD controller with CAN/CAN-FD ISO 16845-1:2016 certification compliance

## Security enablers

- ISO21434 Automotive Cybersecurity Compliant

- Hardware Security Module (HSM) with proprietary controller and dedicated memories supporting accelerated cryptographic operations and secure key storage:

- AES (up to 256 bits) crypto accelerator

- ECC (up to 521 bits), RSA (up to 3072 bits) public key accelerator

- SHA-2 (up to 512 bits) accelerator

- True random number generator

- HSM firmware update support

- Differential power analysis (DPA) countermeasures for AES and ECC

- Separate AES 128-bit cryptographic accelerator (LAES) for latency-critical link-layer operations

- Secure boot and secure firmware updates

- Cortex®-M33 TrustZone-M, MPU, memory firewalls for software isolation

- Voltage glitch monitor (VGM)

#### Low-power consumption (VDDS at 3.3V)

- On-chip buck DC/DC converter

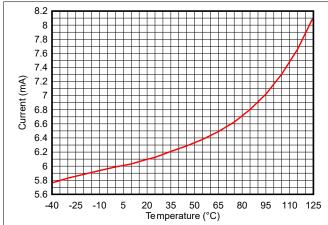

- RX current: 6.1mA

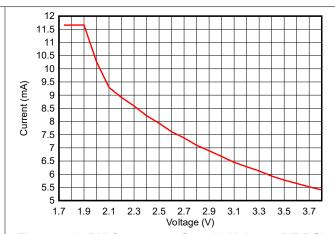

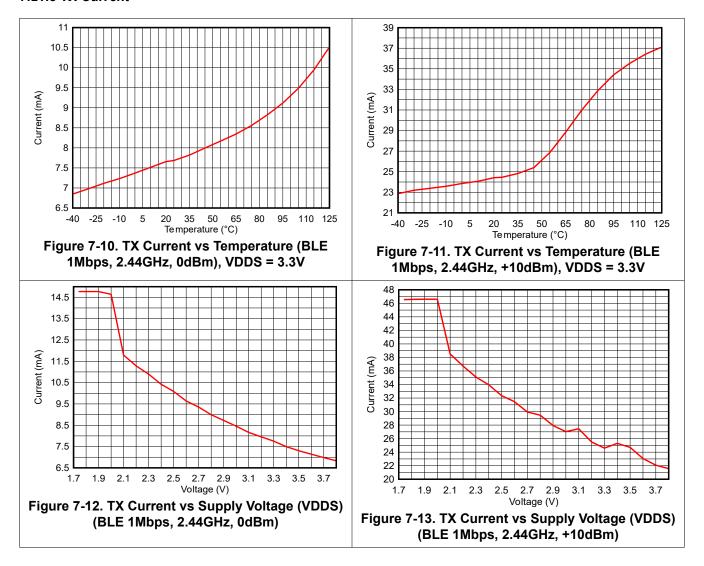

- TX current at 0dBm: 7.7mA

- TX current at +10dBm: 24.5mA (R variant)

- TX current at +20dBm: 143mA (P variant)

- Active mode MCU 96MHz (CoreMark®): 6.8mA

- Standby: 0.9µA (low power mode, RTC on, full SRAM retention)

- Shutdown: 160nA

#### Wireless protocol support

- Bluetooth® Core 6.0 Qualified

- Support for Bluetooth® Channel Sounding (High Accuracy Distance Measurement)

#### High-performance radio

- 2.4GHz RF transceiver compatible with Bluetooth® Low Energy specification

- Output power up to +10dBm (R variant)

- Output power up to +20dBm (P variant)

- Integrated BALUN

- Integrated RF switch

- Receiver sensitivity:

- Bluetooth® LE 125kbps: -103.5dBm

- Bluetooth® LE 1Mbps: –97dBm

#### Regulatory compliance

- Designed for systems targeting compliance with worldwide radio frequency regulations

- EN 300 328 (Europe)

- FCC CFR47 Part 15 (US)

- ARIB STD-T66 (Japan)

#### **Development tools and software**

- LP-EM-CC2745R10-Q1, LP-EM-CC2755P10 LaunchPad™ Development Kit

- BP-EM-CS Multiple antenna board for Bluetooth<sup>®</sup> Channel Sounding

- SimpleLink™ Low Power F3 Software Development Kit (SDK)

- Fully qualified Bluetooth® software protocol stack in the SDK

- Up to 32 concurrent multirole connections

- Bluetooth® Low Energy 6.0 Support

- CCC Digital Key 3 / ICCE Bluetooth<sup>®</sup> APIs support for secure car access systems

- Automotive SPICE (ASPICE) compliance for SDK components, including the Bluetooth<sup>®</sup> LE stack

- SysConfig system configuration tool

- SmartRF<sup>™</sup> Studio for simple radio configuration

## **Operating ranges**

- Junction temperature T<sub>J</sub>: –40°C to 125°C

- Wide supply voltage range 1.71V to 3.8V

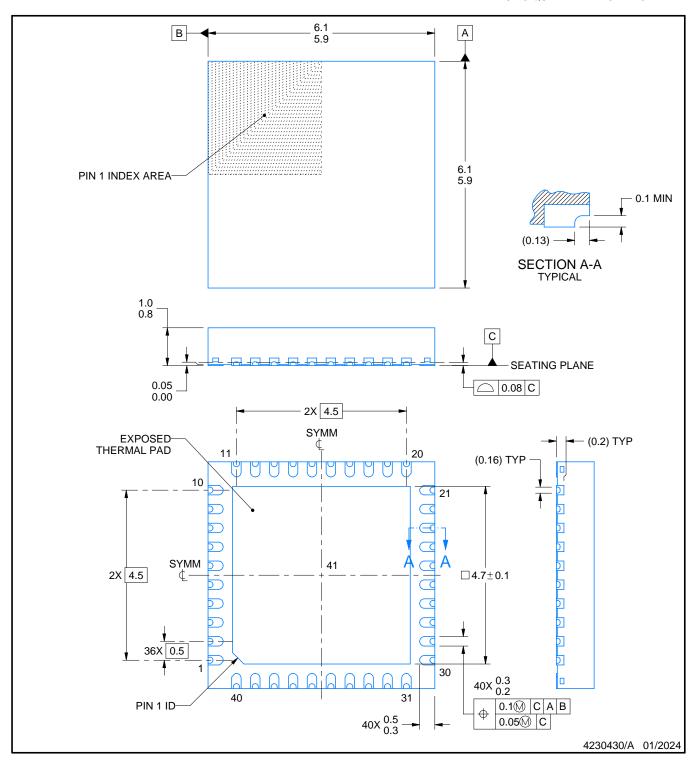

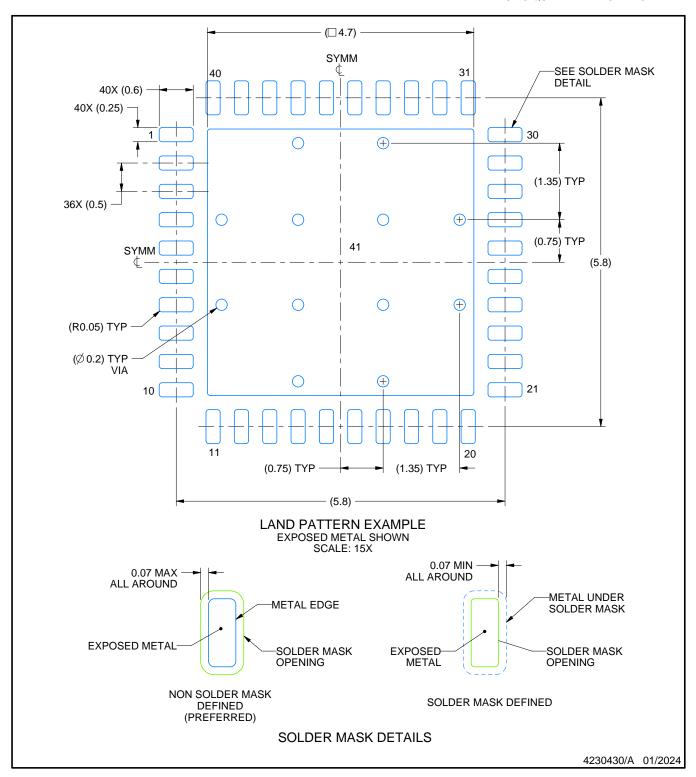

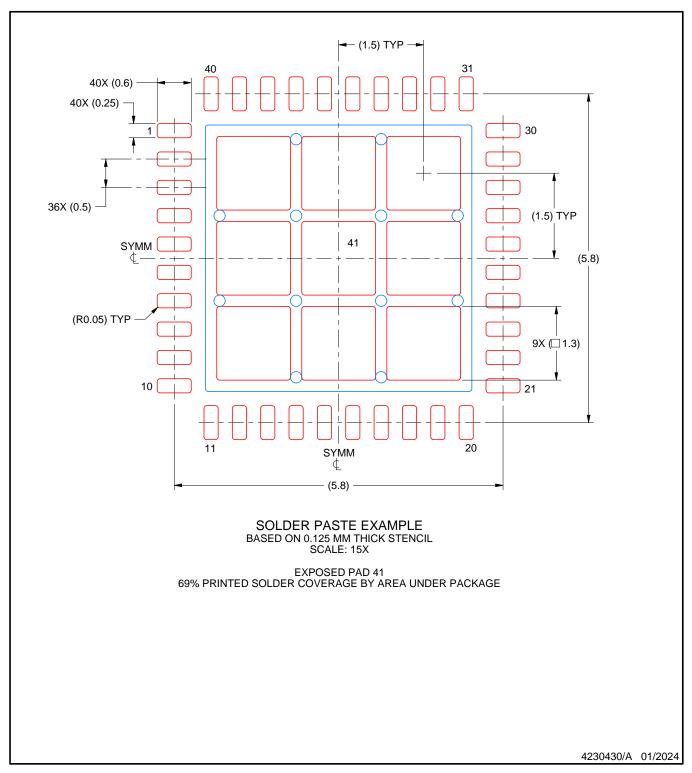

### **Package**

- 6mm × 6mm QFN40 with wettable flanks

- RoHS-compliant package

# 2 Applications

- Automotive

- Car access and security systems

- Digital key

- Phone as a key (PaaK)

- Passive entry passive start (PEPS)

- Remote keyless entry (RKE)

# 3 Description

The SimpleLink™ CC274xR-Q1 and CC274xP-Q1 devices are AEC-Q100 complaint wireless microcontrollers (MCUs) supporting Bluetooth® Low Energy 6.0 for automotive applications. These devices are optimized for low-power wireless communication in applications such as car access, including passive entry passive start (PEPS), phone as a key (PaaK), and remote keyless entry (RKE). The key features of this device include:

- Support for features in Bluetooth® 6.0 and earlier versions:

- LE Coded PHYs (Long Range), LE 2Mbit PHY (high speed), advertising extensions, multiple advertisement sets, CSA#2, as well as backward compatibility with earlier Bluetooth<sup>®</sup> Low Energy specifications

- Bluetooth® Channel Sounding technology support and an Algorithm Processing Unit (APU) to enable high accuracy, low cost, and a secure phase-based ranging mechanism for distance estimation

- APU enables latency and power-efficient execution of distance-ranging signal processing algorithms, including FFT, super-resolution complex algorithms like MUltiple SIgnal Classification (MUSIC), and neural network algorithms.

- Arm®Custom Data Extension (CDE) instruction support for machine learning acceleration

- Fully qualified Bluetooth® software protocol stack included with the SimpleLink™ Low Power F3 Software Development Kit (SDK)

- Advanced security features for connected wireless MCUs:

- An isolated HSM environment with a dedicated controller handling accelerated cryptographic and random number generation operations

- Secure boot and firmware updates with the root of trust enabled by an immutable system ROM

- Arm® Cortex M33 TrustZone-M based trusted execution environment support

- Secure key storage support with HSM and TrustZone-M

- Hardware fault sensors to mitigate low-cost, low-effort, non-invasive physical attack threats like voltage glitch injection

- Dedicated AES-128 HW accelerator for handling timing-critical link-layer encryption/decryption operations

- Ultra-low standby current with full 162KB SRAM retention and RTC operation that enables significant battery life extension, especially for applications with longer sleep intervals

- Extended temperature support with the lowest standby current

- Integrated BALUN and integrated RF switch to support both transmit and receive operations on the same RF pin, even in the P version; thereby, enabling a reduced bill-of-material (BOM) board layout

- Excellent radio sensitivity and robustness (selectivity and blocking) performance for Bluetooth® Low Energy

The CC274xR/P-Q1 devices are part of the SimpleLink<sup>™</sup> MCU platform, which consists of Wi-Fi®, Bluetooth® Low Energy, Thread, Zigbee, Sub1GHz MCUs, and host MCUs that all share a common, easy-to-use development environment with a single core software development kit (SDK) and a rich toolset. A one-time integration of the SimpleLink™ platform enables you to add any combination of the portfolio's devices into your design, allowing 100 percent code reuse when your design requirements change. For more information, visit SimpleLink™ MCU platform.

**Table 3-1. Device Information**

| PART NUMBER        | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|--------------------|------------------------|-----------------------------|

| CC2745R10E0WRHARQ1 | QFN40                  | 6.0mm × 6.0mm               |

| CC2745R10E1WRHARQ1 | QFN40                  | 6.0mm × 6.0mm               |

| CC2745P10E0WRHARQ1 | QFN40                  | 6.0mm × 6.0mm               |

| CC2745R74E0WRHARQ1 | QFN40                  | 6.0mm × 6.0mm               |

| CC2744R74E0WRHARQ1 | QFN40                  | 6.0mm × 6.0mm               |

For more information, see the Mechanical, Packaging, and Orderable addendum.

The package size (length × width) is a nominal value and includes pins, where applicable.

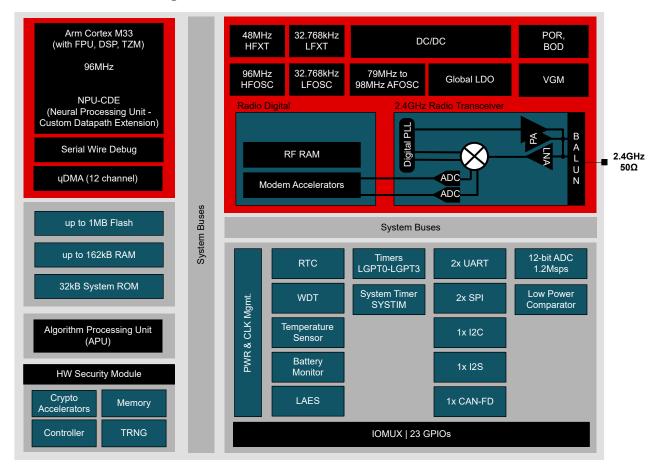

# 4 Functional Block Diagram

Figure 4-1. Functional Block Diagram

# **Table of Contents**

| 1 Features                                       | 1 8 Detailed Description                    | 52              |

|--------------------------------------------------|---------------------------------------------|-----------------|

| 2 Applications                                   | .2 8.1 Overview                             | 52              |

| 3 Description                                    | .2 8.2 System CPU                           | 52              |

| 4 Functional Block Diagram                       | . 4 8.3 Radio (RF Core)                     | 53              |

| 5 Device Comparison                              | .6 8.4 Memory                               | 53              |

| 6 Pin Configuration and Functions                | .7 8.5 Hardware Security Module (HSM)       | 53              |

| 6.1 Pin Diagrams                                 | . 7 8.6 Cryptography                        | 55              |

| 6.2 Signal Descriptions                          | . 8 8.7 Timers                              | 55              |

| 6.3 Connections for Unused Pins and Modules      | .9 8.8 Algorithm Processing Unit (APU)      | 56              |

| 6.4 Peripheral Pin Mapping1                      |                                             |                 |

| 6.5 Peripheral Signal Descriptions1              |                                             | <mark>57</mark> |

| 7 Specifications2                                |                                             |                 |

| 7.1 Absolute Maximum Ratings2                    |                                             |                 |

| 7.2 ESD and MSL Ratings2                         | 21 8.13 Debug                               | 58              |

| 7.3 Recommended Operating Conditions2            | 8.14 Power Management                       | 59              |

| 7.4 DC/DC2                                       |                                             | 60              |

| 7.5 GLDO2                                        | 8.16 Network Processor                      | 60              |

| 7.6 Power Supply and Modules2                    | 8.17 Integrated BALUN, High Power PA (Power |                 |

| 7.7 Battery Monitor2                             |                                             | 60              |

| 7.8 BATMON Temperature Sensor2                   | 9 Application, Implementation, and Layout   | 61              |

| 7.9 Power Consumption—Power Modes2               | 9.1 Reference Designs                       | 61              |

| 7.10 Power Consumption—Radio Modes (R variant)2  | 9.2 Junction Temperature Calculation        | 62              |

| 7.11 Power Consumption-Radio Modes (P variant) 2 | 25 10 Device and Documentation Support      | 63              |

| 7.12 Nonvolatile (Flash) Memory Characteristics2 | 10.1 Device Nomenclature                    |                 |

| 7.13 Thermal Resistance Characteristics          | 26 10.2 Tools and Software                  | 63              |

| 7.14 RF Frequency Bands2                         | 27 10.3 Documentation Support               | 65              |

| 7.15 Bluetooth Low Energy—Receive (RX)2          |                                             | 65              |

| 7.16 Bluetooth Low Energy—Transmit (TX)          |                                             | 66              |

| 7.17 Bluetooth Channel Sounding3                 |                                             | 66              |

| 7.18 2.4GHz RX/TX CW3                            |                                             |                 |

| 7.19 Timing and Switching Characteristics3       | 32 11 Revision History                      | 66              |

| 7.20 Peripheral Characteristics3                 | <del>_</del>                                |                 |

| 7.21 Typical Characteristics4                    |                                             | 67              |

# **5 Device Comparison**

| IP                                                                            | CC2745P10-Q1        | CC2745R10-Q1        | CC2745R7-Q1        | CC2744R7-Q1        |

|-------------------------------------------------------------------------------|---------------------|---------------------|--------------------|--------------------|

| CM33 (MCU)                                                                    | ✓                   | <b>✓</b>            | ✓                  | ✓                  |

| APU (Algorithm Processing Unit) (Bluetooth Channel Sounding Post- processing) | 1                   | 1                   | 1                  | 1                  |

| CAN-FD Controller                                                             | ✓                   | ✓                   | ✓                  |                    |

| HSM                                                                           | 1                   | ✓                   | ✓                  | ✓                  |

| VGM                                                                           | ✓                   | <b>✓</b>            | ✓                  | ✓                  |

| 2x UART, 2x SPI, 1x I <sup>2</sup> C,<br>1x I <sup>2</sup> S                  | 1                   | 1                   | 1                  | 1                  |

| +10dBm PA                                                                     | ✓                   | <b>✓</b>            | ✓                  | ✓                  |

| +20dBm PA                                                                     | ✓                   |                     |                    |                    |

| ADC12                                                                         | 1                   | ✓                   | ✓                  | ✓                  |

| Flash (KB)                                                                    | 1024 <sup>(1)</sup> | 1024 <sup>(1)</sup> | 864 <sup>(1)</sup> | 864 <sup>(1)</sup> |

| SRAM (KB) (parity disabled)                                                   | 162                 | 162                 | 128                | 128                |

| SRAM (KB) (parity enabled)                                                    | 144                 | 144                 | 128                | 128                |

| GPIO                                                                          | 23                  | 23                  | 23                 | 23                 |

| QFN PKG Size (mm x mm)                                                        | 6 x 6               | 6 x 6               | 6 x 6              | 6 x 6              |

<sup>(1) 96</sup>KB of the device flash memory is reserved for HSM firmware.

# 6 Pin Configuration and Functions

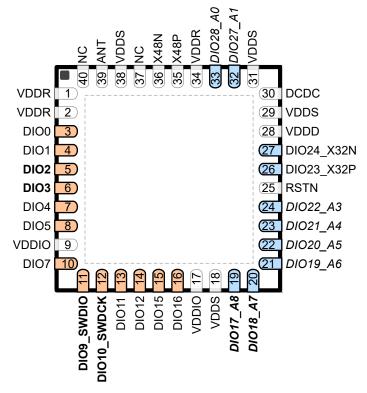

# 6.1 Pin Diagrams

#### 6.1.1 Pin Diagram—RHA package

Figure 6-1. RHA (6mm × 6mm) Pinout, 0.5mm Pitch (Top View)

The following I/O pins marked in Figure 6-1 in **bold** have high-drive capabilities:

- Pin 5, DIO2

- Pin 6, DIO3

- Pin 11, DIO9\_SWDIO

- Pin 12, DIO10\_SWDCK

- Pin 19, DIO17 A8

- Pin 20, DIO18\_A7

The following I/O pins marked in Figure 6-1 in *italics* have analog capabilities:

- Pin 19, DIO17 A8

- Pin 20, DIO18\_A7

- Pin 21, DIO19\_A6

- Pin 22, DIO20\_A5

- Pin 23, DIO21\_A4

- Pin 24, DIO22 A3

- Pin 32, DIO27\_A1

- Pin 33, DIO28\_A0

The following I/O pins marked in Figure 6-1 in orange color are supplied by VDDIO:

- Pin 3, DIO0

- Pin 4, DIO1

- Pin 5, DIO2

- Pin 6, DIO3

- Pin 7, DIO4

- Pin 8, DIO5

- Pin 10, DIO7

- Pin 11, DIO9\_SWDIO

- Pin 12, DIO10\_SWDCK

- Pin 13, DIO11

- Pin 14. DIO12

- Pin 15, DIO15

- Pin 16, DIO16

The following I/O pins marked in Figure 6-1 in *blue color* are supplied by VDDS:

- Pin 19, DIO17 A8

- Pin 20, DIO18\_A7

- Pin 21, DIO19 A6

- Pin 22, DIO20\_A5

- Pin 23, DIO21\_A4

- Pin 24, DIO22\_A3

- Pin 26, DIO23 X32P

- Pin 27, DIO24\_X32N

- Pin 32, DIO27\_A1

- Pin 33, DIO28\_A0

# 6.2 Signal Descriptions

#### 6.2.1 Signal Descriptions—RHA Package

Table 6-1. Signal Descriptions—RHA Package

| Table 6-1. Digital Descriptions—INTA Lackage |     |          |         |                                                                                                               |  |  |  |

|----------------------------------------------|-----|----------|---------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN                                          |     | I/O TYPE |         | DESCRIPTION                                                                                                   |  |  |  |

| NAME                                         | NO. | 1/0      | 1112    | DESCRIPTION                                                                                                   |  |  |  |

| VDDR                                         | 1   | _        | Power   | Internal supply, must be powered from the internal DC/DC converter or the GLDO <sup>(1)</sup> (2) (3)         |  |  |  |

| VDDR                                         | 2   | _        | Power   | Internal supply, must be powered from the internal DC/DC converter or the internal LDO <sup>(1)</sup> (2) (3) |  |  |  |

| DIO0                                         | 3   | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| DIO1                                         | 4   | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| DIO2                                         | 5   | I/O      | Digital | GPIO, high-drive capability                                                                                   |  |  |  |

| DIO3                                         | 6   | I/O      | Digital | GPIO, high-drive capability                                                                                   |  |  |  |

| DIO4                                         | 7   | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| DIO5                                         | 8   | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| VDDIO                                        | 9   | _        | Power   | 1.71V to 3.8V split rail I/O supply <sup>(4)</sup>                                                            |  |  |  |

| DIO7                                         | 10  | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| DIO9_SWDIO                                   | 11  | I/O      | Digital | GPIO, SWD interface: mode select or SWDIO, high-drive capability                                              |  |  |  |

| DIO10_SWDCK                                  | 12  | I/O      | Digital | GPIO, SWD interface: serial wire clock, high-drive capability                                                 |  |  |  |

| DIO11                                        | 13  | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| DIO12                                        | 14  | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| DIO15                                        | 15  | I/O      | Digital | GPIO                                                                                                          |  |  |  |

| DIO16                                        | 16  | I/O      | Digital | GPIO                                                                                                          |  |  |  |

Table 6-1. Signal Descriptions—RHA Package (continued)

| PIN        |     | Table 6-1. Signal Descriptions |                   |                                                                                                                                                                                           |  |

|------------|-----|--------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO. | I/O                            | TYPE              | DESCRIPTION                                                                                                                                                                               |  |

| VDDIO      | 17  | _                              | Power             | 1.71V to 3.8V split rail I/O supply <sup>(4)</sup>                                                                                                                                        |  |

| VDDS       | 18  | _                              | Power             | 1.71V to 3.8V supply <sup>(4)</sup>                                                                                                                                                       |  |

| DIO17_A8   | 19  | I/O                            | Digital or Analog | GPIO, analog capability, high-drive capability                                                                                                                                            |  |

| DIO18_A7   | 20  | I/O                            | Digital or Analog | GPIO, analog capability, high-drive capability                                                                                                                                            |  |

| DIO19_A6   | 21  | I/O                            | Digital or Analog | GPIO, analog capability                                                                                                                                                                   |  |

| DIO20_A5   | 22  | I/O                            | Digital or Analog | GPIO, analog capability                                                                                                                                                                   |  |

| DIO21_A4   | 23  | I/O                            | Digital or Analog | GPIO, analog capability                                                                                                                                                                   |  |

| DIO22_A3   | 24  | I/O                            | Digital or Analog | GPIO, analog capability                                                                                                                                                                   |  |

| RSTN       | 25  | I                              | Digital           | Reset, active low. No internal pullup resistor                                                                                                                                            |  |

| DIO23_X32P | 26  | I/O                            | Digital or Analog | GPIO, 32kHz crystal oscillator pin 1, optional TCXO input                                                                                                                                 |  |

| DIO24_X32N | 27  | I/O                            | Digital or Analog | GPIO, 32kHz crystal oscillator pin 2                                                                                                                                                      |  |

| VDDD       | 28  | _                              | Power             | Internal 1.32V regulated core-supply. Connect an external 1µF decoupling capacitor. <sup>(1)</sup>                                                                                        |  |

| VDDS       | 29  | _                              | Power             | 1.71V to 3.8V supply <sup>(4)</sup>                                                                                                                                                       |  |

| DCDC       | 30  | _                              | Power             | Switching node of internal DC/DC converter <sup>(4)</sup>                                                                                                                                 |  |

| VDDS       | 31  | _                              | Power             | 1.71V to 3.8V supply. Connect an external 10µF decoupling capacitor. (4)                                                                                                                  |  |

| DIO27_A1   | 32  | I/O                            | Digital or Analog | GPIO, analog capability                                                                                                                                                                   |  |

| DIO28_A0   | 33  | I/O                            | Digital or Analog | GPIO, analog capability                                                                                                                                                                   |  |

| VDDR       | 34  | _                              | Power             | Internal supply, must be powered from the internal DC/DC converter or the internal LDO. Connect an external 10µF decoupling capacitor. <sup>(1)</sup> ( <sup>(2)</sup> ( <sup>(3)</sup> ) |  |

| X48P       | 35  | _                              | Analog            | 48MHz crystal oscillator pin 1                                                                                                                                                            |  |

| X48N       | 36  | _                              | Analog            | 48MHz crystal oscillator pin 2                                                                                                                                                            |  |

| NC         | 37  | _                              | _                 | No Connect                                                                                                                                                                                |  |

| VDDS       | 38  | _                              | Power             | 1.71V to 3.8V supply <sup>(4)</sup>                                                                                                                                                       |  |

| ANT        | 39  | _                              | RF                | 2.4GHz TX, RX                                                                                                                                                                             |  |

| NC         | 40  | _                              | _                 | No Connect <sup>(6)</sup>                                                                                                                                                                 |  |

| EGP        | _   | _                              | GND               | Ground – exposed ground pad <sup>(5)</sup>                                                                                                                                                |  |

- (1) Do not supply external circuitry from this pin.

- (2) VDDR pins 1, 2, and 34 must be tied together on the PCB.

- (3) Output from internal DC/DC and LDO is trimmed to 1.5V.

- (4) For more details, see the technical reference manual listed in Documentation Support.

- (5) EGP is the only ground connection for the device. A good electrical connection to the device ground on the printed circuit board (PCB) is imperative for proper device operation.

- (6) This pin is not connected to the die. In the LP-EM-CC2745R10-Q1, LP-EM-CC2755P10 reference design, this pin is connected to ground to give better shielding on the antenna path.

#### 6.3 Connections for Unused Pins and Modules

#### 6.3.1 Connections for Unused Pins and Modules—RHA Package

Table 6-2. Connections for Unused Pins—RHA Package

| FUNCTION       | SIGNAL NAME | PIN NUMBER         | ACCEPTABLE PRACTICE(1) | PREFERRED<br>PRACTICE <sup>(1)</sup> |

|----------------|-------------|--------------------|------------------------|--------------------------------------|

| GPIO (digital) | DIOn        | 3–8<br>10<br>13–16 | NC, GND, or VDDS       | NC                                   |

Table 6-2. Connections for Unused Pins—RHA Package (continued)

| FUNCTION                       | SIGNAL NAME | PIN NUMBER     | ACCEPTABLE PRACTICE(1) | PREFERRED PRACTICE(1) |

|--------------------------------|-------------|----------------|------------------------|-----------------------|

| CIMD                           | DIO9_SWDIO  | 11             | NC, GND, or VDDS       | NC <sup>(3)</sup>     |

| SWD                            | DIO10_SWDCK | 12             | NC, GND, or VDDS       | NC <sup>(4)</sup>     |

| GPIO (digital or analog)       | DIOn_Am     | 19–24<br>32–33 | NC, GND, or VDDS       | NC                    |

| 32.768kHz crystal              | DIO23_X32P  | 26             | NC or GND              | NC                    |

| 32.7 OOKI 12 GI yStai          | DIO24_X32N  | 27             | INC OF CIND            | 140                   |

| DC/DC converter <sup>(2)</sup> | DCDC        | 30             | NC                     | NC                    |

| DC/DC converter                | VDDS        | 18, 29, 31, 38 | VDDS                   | VDDS                  |

| Split Rail I/O supply          | VDDIO       | 9, 17          | VDDS                   | VDDS                  |

<sup>(1)</sup> NC = No connect

## 6.4 Peripheral Pin Mapping

## 6.4.1 RHA Peripheral Pin Mapping

Table 6-3. RHA (QFN40) Peripheral Pin Mapping

| PIN NO. | PIN NAME   | SIGNAL NAME | SIGNAL TYPE(1) | PIN MUX ENCODING | SIGNAL DIDECTION |

|---------|------------|-------------|----------------|------------------|------------------|

| QFN40   | PIN NAIVIE | SIGNAL NAME | SIGNAL ITPE    | PIN MUX ENCODING | SIGNAL DIRECTION |

| 1       | VDDR       | VDDR        | _              | N/A              | N/A              |

| 2       | VDDR       | VDDR        | _              | N/A              | N/A              |

|         |            | GPIO0       |                | 0                | I/O              |

|         |            | T0C0        |                | 1                | I/O              |

| 3       | DIO0       | T1F         | I/O            | 2                | 0                |

| 3       | DIOU       | T3C0N       |                | 3                | 0                |

|         |            | LPCO        |                | 4                | 0                |

|         |            | T1C0        |                | 5                | I/O              |

|         |            | GPIO1       |                | 0                | I/O              |

|         |            | CAN0TX      |                | 1                | 0                |

|         |            | T1C0        |                | 2                | I/O              |

| 4       | DIO1       | T2C0        | I/O            | 3                | I/O              |

|         |            | UART0TXD    |                | 4                | 0                |

|         |            | T1C1        |                | 5                | I/O              |

|         |            | DTB15       |                | 7                | 0                |

|         |            | GPIO2       |                | 0                | I/O              |

|         |            | CAN0RX      |                | 1                | I                |

|         |            | T1C1        |                | 2                | I/O              |

| 5       | DIO2       | T0PE        | I/O            | 3                | 0                |

|         |            | UART0RXD    |                | 4                | I                |

|         |            | T1C2        |                | 5                | I/O              |

|         |            | DTB14       |                | 7                | 0                |

<sup>(2)</sup> When the DC/DC converter is not used, the inductor between DCDC and VDDR can be removed. VDDR must still be connected, and the 10μF decoupling capacitor must be kept on the VDDR net.

<sup>(3)</sup> By default, an internal pullup is enabled on SWDIO.

<sup>(4)</sup> By default, an internal pulldown is enabled on SWDCK.

| PIN NO. |               |             |                | PIN MUY ENGORING | CIONAL DIDECTION |

|---------|---------------|-------------|----------------|------------------|------------------|

| QFN40   | PIN NAME      | SIGNAL NAME | SIGNAL TYPE(1) | PIN MUX ENCODING | SIGNAL DIRECTION |

|         |               | GPIO3       |                | 0                | I/O              |

|         |               | SPI0SCLK    |                | 1                | I/O              |

|         |               | I2S0SCLK    |                | 2                | I/O              |

| 6       | DIO3          | T2PE        | I/O            | 3                | 0                |

|         |               | UART1TXD    |                | 4                | 0                |

|         |               | T2C0        |                | 5                | I/O              |

|         |               | DTB13       |                | 7                | 0                |

|         |               | GPIO4       |                | 0                | I/O              |

|         |               | SPI0PICO    |                | 1                | I/O              |

|         |               | SPI0POCI    |                | 2                | I/O              |

| 7       | DIO4          | T1C2        | I/O            | 3                | I/O              |

|         |               | UART1RXD    |                | 4                | I                |

|         |               | T2C1        |                | 5                | I/O              |

|         |               | DTB12       |                | 7                | 0                |

|         |               | GPIO5       |                | 0                | I/O              |

|         |               | SPI0POCI    |                | 1                | I/O              |

|         |               | SPI0PICO    |                | 2                | I/O              |

| 8       | DIO5          | T2C1        | I/O            | 3                | I/O              |

|         |               | T3C1N       |                | 4                | 0                |

|         |               | T2C2        |                | 5                | I/O              |

|         |               | DTB11       |                | 7                | 0                |

| 9       | VDDIO         | VDDIO       | _              | N/A              | N/A              |

|         |               | GPI07       |                | 0                | I/O              |

|         |               | SPI0CSN     |                | 1                | I/O              |

| 40      | DIO7          | T2C2        |                | 2                | I/O              |

| 10      | DIO7          | I2S0WS      | I/O            | 3                | I/O              |

|         |               | T3C2N       |                | 4                | 0                |

|         |               | DTB10       |                | 7                | 0                |

|         |               | GPIO9       |                | 0                | I/O              |

|         |               | T0C1        |                | 1                | I/O              |

| 44      | DIOC OWDIO    | T2C0N       |                | 2                | 0                |

| 11      | DIO9_SWDIO    | 12S0SD0     | I/O            | 3                | I/O              |

|         |               | T0PE        |                | 4                | 0                |

|         |               | I2C0SCL     |                | 5                | I/O              |

|         |               | GPIO10      |                | 0                | I/O              |

|         |               | T0C2        |                | 1                | I/O              |

|         | DIO 40 CHIEST | T2C1N       |                | 2                | 0                |

| 12      | DIO10_SWDCK   | I2S0SD1     | I/O            | 3                | I/O              |

|         |               | T2PE        |                | 4                | 0                |

|         |               | I2C0SDA     |                | 5                | I/O              |

| PIN NO. |          | 0-3. KITA (QI 1440) F |                |                  |                  |

|---------|----------|-----------------------|----------------|------------------|------------------|

| QFN40   | PIN NAME | SIGNAL NAME           | SIGNAL TYPE(1) | PIN MUX ENCODING | SIGNAL DIRECTION |

|         |          | GPIO11                |                | 0                | I/O              |

|         |          | SPI1POCI              |                | 1                | I/O              |

|         |          | SPI1PICO              |                | 2                | I/O              |

| 13      | DIO11    | SWO                   | I/O            | 3                | 0                |

|         |          | T3C0                  |                | 4                | I/O              |

|         |          | T1F                   |                | 5                | 0                |

|         |          | DTB9                  |                | 7                | 0                |

|         |          | GPIO12                |                | 0                | I/O              |

|         |          | SPI1PICO              |                | 1                | I/O              |

|         |          | SPI1POCI              |                | 2                | I/O              |

| 14      | DIO12    | T2C2N                 | I/O            | 3                | 0                |

|         |          | T3C1                  |                | 4                | I/O              |

|         |          | T3C2                  |                | 5                | I/O              |

|         |          | DTB8                  |                | 7                | 0                |

|         |          | GPIO15                |                | 0                | I/O              |

|         | DIO15    | SPI1SCLK              |                | 1                | I/O              |

| 15      |          | T3C2                  | I/O            | 2                | I/O              |

| 15      |          | T1C0N                 |                | 3                | 0                |

|         |          | LPCO                  |                | 4                | 0                |

|         |          | T3C1                  |                | 5                | I/O              |

|         |          | GPIO16                |                | 0                | I/O              |

|         |          | I2S0MCLK              |                | 1                | 0                |

|         |          | SPI1CSN               |                | 2                | I/O              |

| 16      | DIO16    | EXTCI                 | I/O            | 3                | ı                |

|         |          | T1F                   |                | 4                | I                |

|         |          | T3C0                  |                | 5                | I/O              |

|         |          | DTB7                  |                | 7                | 0                |

| 17      | VDDIO    | VDDIO                 | _              | N/A              | N/A              |

| 18      | VDDS     | VDDS                  | _              | N/A              | N/A              |

|         |          | GPIO17                |                | 0                | I/O              |

|         |          | I2S0SCLK              |                | 1                | I/O              |

|         |          | UART0RTS              |                | 2                | 0                |

| 10      | DIO17 A9 | CAN0TX                | 1/0            | 3                | 0                |

| 19      | DIO17_A8 | T0C0                  | I/O            | 4                | I/O              |

|         |          | LRFD0                 |                | 5                | 0                |

|         |          | ADC8                  |                | 6                | I                |

|         |          | DTB6                  |                | 7                | 0                |

| PIN NO. |          | CICNAL NAME    |                |                  | CICNAL DIDECTION |

|---------|----------|----------------|----------------|------------------|------------------|

| QFN40   | PIN NAME | SIGNAL NAME    | SIGNAL TYPE(1) | PIN MUX ENCODING | SIGNAL DIRECTION |

|         |          | GPIO18         |                | 0                | I/O              |

|         |          | I2S0WS         |                | 1                | I/O              |

|         |          | UART0CTS       |                | 2                | I                |

| 20      | DIO19 A7 | CAN0RX         | I/O            | 3                | I                |

| 20      | DIO18_A7 | T0C1           | - 1/0          | 4                | I/O              |

|         |          | LRFD1          |                | 5                | 0                |

|         |          | ADC7           |                | 6                | I                |

|         |          | DTB5           |                | 7                | 0                |

|         |          | GPIO19         |                | 0                | I/O              |

|         |          | SPI0CSN        |                | 1                | I/O              |

|         |          | UART0TXD       |                | 2                | 0                |

| 0.4     | DIO40 40 | UART0RXD       | - 1/0          | 3                | I                |

| 21      | DIO19_A6 | I2S0SD0        | I/O            | 4                | I/O              |

|         |          | LRFD2          |                | 5                | 0                |

|         |          | ADC6/LPC+      |                | 6                | I                |

|         |          | DTB4           |                | 7                | 0                |

|         |          | GPIO20         |                | 0                | I/O              |

|         | DIO20_A6 | SPI0SCLK       |                | 1                | I/O              |

|         |          | UART0RXD       | =              | 2                | I                |

|         |          | UART0TXD       |                | 3                | 0                |

| 22      |          | I2S0SD1        | I/O            | 4                | I/O              |

|         |          | LRFD3          |                | 5                | 0                |

|         |          | ADC5/LPC+/LPC- |                | 6                | I                |

|         |          | DTB3           |                | 7                | 0                |

|         |          | GPIO21         |                | 0                | I/O              |

|         |          | SPI0PICO       |                | 1                | I/O              |

|         |          | UART1TXD       |                | 2                | 0                |

|         |          | I2C0SCL        |                | 3                | I/O              |

| 23      | DIO21_A4 | T1C1N          | I/O            | 4                | 0                |

|         |          | LRFD4          |                | 5                | 0                |

|         |          | ADC4/LPC+/LPC- |                | 6                | I                |

|         |          | DTB2           |                | 7                | 0                |

|         |          | GPIO22         |                | 0                | I/O              |

|         |          | SPI0POCI       |                | 1                | I/O              |

|         |          | UART1RXD       |                | 2                | I                |

| _       |          | I2C0SDA        |                | 3                | I/O              |

| 24      | DIO22_A3 | T1C2N          | I/O            | 4                | 0                |

|         |          | LRFD5          |                | 5                | 0                |

|         |          | ADC3           |                | 6                | I                |

|         |          | DTB1           |                | 7                | 0                |

| 25      | RTSN     | RSTN           | _              | N/A              | N/A              |

| PIN NO. |            | 5-3. KHA (QFN4U) P |                |                  |                  |

|---------|------------|--------------------|----------------|------------------|------------------|

| QFN40   | PIN NAME   | SIGNAL NAME        | SIGNAL TYPE(1) | PIN MUX ENCODING | SIGNAL DIRECTION |

|         |            | GPIO23             |                | 0                | I/O              |

|         |            | SPI1CSN            |                | 1                | I/O              |

|         |            | UART1RTS           |                | 2                | 0                |

| 26      | DIO23_X32P | LFCI               | I/O            | 3                | I                |

|         |            | T0C2               |                | 4                | I/O              |

|         |            | T1C0               |                | 5                | I/O              |

|         |            | LFXT_P             |                | 6                | I                |

|         |            | GPIO24             |                | 0                | I/O              |

|         |            | SPI1SCLK           |                | 1                | I/O              |

|         |            | UART1CTS           |                | 2                | I                |

| 27      | DIO24_X32N | TOCON              | I/O            | 3                | 0                |

|         | _          | LPCO               |                | 4                | 0                |

|         |            | T0C0               |                | 5                | I/O              |

|         |            | LFXT_N             |                | 6                | I                |

| 28      | VDDD       | VDDD               | _              | N/A              | N/A              |

| 29      | VDDS       | VDDS               | _              | N/A              | N/A              |

| 30      | DCDC       | DCDC               | _              | N/A              | N/A              |

| 31      | VDDS       | VDDS               | _              | N/A              | N/A              |

|         |            | GPIO27             |                | 0                | I/O              |

|         |            | SPI1PICO           |                | 1                | I/O              |

|         |            | I2C0SCL            |                | 2                | I/O              |

|         |            | CKMIN              |                | 3                | I                |

| 32      | DIO27_A1   | T0C1N              | I/O            | 4                | 0                |

|         |            | LRFD6              |                | 5                | 0                |

|         |            | ADC1/AREF+         | -              | 6                | I                |

|         |            | DTB0               |                | 7                | 0                |

|         |            | GPIO28             |                | 0                | I/O              |

|         |            | SPI1POCI           |                | 1                | I/O              |

|         |            | I2C0SDA            |                | 2                | I/O              |

| 33      | DIO28_A0   | T3C0N              | I/O            | 3                | 0                |

|         | _          | T0C2N              |                | 4                | 0                |

|         |            | LRFD7              |                | 5                | 0                |

|         |            | ADC0/AREF-         |                | 6                | I                |

| 34      | VDDR       | VDDR               | _              | N/A              | N/A              |

| 35      | X48P       | X48P               | _              | N/A              | N/A              |

| 36      | X48N       | X48N               | _              | N/A              | N/A              |

| 37      | NC         | NC                 | _              | N/A              | N/A              |

| 38      | VDDS       | VDDS               | _              | N/A              | N/A              |

| 39      | ANT        | ANT                | _              | N/A              | N/A              |

| 40      | NC         | NC                 | _              | N/A              | N/A              |

| _       | EGP        | GND                | _              | N/A              | N/A              |

<sup>(1)</sup> Signal Types: I = Input, O = Output, I/O = Input or Output.

# 6.5 Peripheral Signal Descriptions

# 6.5.1 RHA Peripheral Signal Descriptions

Table 6-4. RHA (QFN40) Peripheral Signal Descriptions

|               |             |                     |             | , compriorar c      |                                                                                        |  |  |

|---------------|-------------|---------------------|-------------|---------------------|----------------------------------------------------------------------------------------|--|--|

| FUNCTION      | SIGNAL NAME | Pin<br>No.<br>QFN40 | PIN<br>TYPE | SIGNAL<br>DIRECTION | DESCRIPTION                                                                            |  |  |

|               | ADC0        | 33                  |             |                     | ADC channel 0 input                                                                    |  |  |

|               | ADC1        | 32                  |             |                     | ADC channel 1 input                                                                    |  |  |

|               | ADC3        | 24                  |             |                     | ADC channel 3 input                                                                    |  |  |

| 450           | ADC4        | 23                  | I/O         |                     | ADC channel 4 input                                                                    |  |  |

| ADC           | ADC5        | 22                  | 1/0         | ı                   | ADC channel 5 input                                                                    |  |  |

|               | ADC6        | 21                  |             |                     | ADC channel 6 input                                                                    |  |  |

|               | ADC7        | 20                  |             |                     | ADC channel 7 input                                                                    |  |  |

|               | ADC8        | 19                  |             |                     | ADC channel 8 input                                                                    |  |  |

| ADC Deference | AREF+       | 32                  | I/O         |                     | ADC external voltage reference, positive terminal                                      |  |  |

| ADC Reference | AREF-       | 33                  | 1/0         | I                   | ADC external voltage reference, negative terminal                                      |  |  |

| 041155        | CAN0TX      | 4<br>19             | I/O         | 0                   | CAN0 transmit data output                                                              |  |  |

| CAN-FD        | CANORX      | 5<br>20             | I/O         | ı                   | CAN0 receive data input                                                                |  |  |

|               | X32P        | 26                  | I/O         | I                   | 32kHz crystal oscillator pin 1                                                         |  |  |

|               | X32N        | 27                  | I/O         | I                   | 32kHz crystal oscillator pin 2                                                         |  |  |

|               | X48P        | 35                  | _           | I                   | 48MHz crystal oscillator pin 1, Optional TCXO input                                    |  |  |

| Clock         | X48N        | 36                  | _           | I                   | 48MHz crystal oscillator pin 2                                                         |  |  |

|               | CKMIN       | 32                  | I/O         | 1                   | HFOSC tracking loop reference clock input                                              |  |  |

|               | LFCI        | 26                  | I/O         | 1                   | GPIO input for low frequency clock input (LFXT bypass clock from pin) or optional TCXO |  |  |

|               |             | 3                   |             |                     |                                                                                        |  |  |

|               | LPCO        | 15                  | I/O         | 0                   | Low power comparator output                                                            |  |  |

|               |             | 27                  |             |                     |                                                                                        |  |  |

| Comparator    |             | 21                  |             |                     |                                                                                        |  |  |

| LPC+          |             | 22                  |             |                     | Low power comparator positive input terminal                                           |  |  |

|               |             | 23                  | I/O         | I                   |                                                                                        |  |  |

|               | LPC-        | 22                  |             |                     | Lower power comparator negative input terminal                                         |  |  |

|               | LFG-        | 23                  |             |                     | Lower power comparator negative input terminal                                         |  |  |

|                  | 144.00 4111117 | Pin   |             |                     | Descriptions (continued)        |  |  |

|------------------|----------------|-------|-------------|---------------------|---------------------------------|--|--|

| FUNCTION         | SIGNAL NAME    | No.   | PIN<br>TYPE | SIGNAL<br>DIRECTION | DESCRIPTION                     |  |  |

|                  |                | QFN40 | ITPE        | DIRECTION           |                                 |  |  |

|                  | DTB0           | 32    |             |                     | Digital test bus output 0       |  |  |

|                  | DTB1           | 24    |             |                     | Digital test bus output 1       |  |  |

|                  | DTB2           | 23    |             |                     | Digital test bus output 2       |  |  |

|                  | DTB3           | 22    |             |                     | Digital test bus output 3       |  |  |

|                  | DTB4           | 21    |             |                     | Digital test bus output 4       |  |  |

|                  | DTB5           | 20    |             |                     | Digital test bus output 5       |  |  |

|                  | DTB6           | 19    |             |                     | Digital test bus output 6       |  |  |

| Digital Test Bus | DTB7           | 16    | I/O         | О                   | Digital test bus output 7       |  |  |

| Digital 103t Bus | DTB8           | 14    | 1/0         | O                   | Digital test bus output 8       |  |  |

|                  | DTB9           | 13    |             |                     | Digital test bus output 9       |  |  |

|                  | DTB10          | 10    |             |                     | Digital test bus output 10      |  |  |

|                  | DTB11          | 8     |             |                     | Digital test bus output 11      |  |  |

|                  | DTB12          | 7     |             |                     | Digital test bus output 12      |  |  |

|                  | DTB13          | 6     |             |                     | Digital test bus output 13      |  |  |

|                  | DTB14          | 5     |             |                     | Digital test bus output 14      |  |  |

|                  | DTB15          | 4     |             |                     | Digital test bus output 15      |  |  |

|                  | GPIO0          | 3     |             |                     |                                 |  |  |

|                  | GPIO1          | 4     |             |                     |                                 |  |  |

|                  | GPIO2          | 5     |             |                     |                                 |  |  |

|                  | GPIO3          | 6     |             |                     |                                 |  |  |

|                  | GPIO4          | 7     |             |                     |                                 |  |  |

|                  | GPIO5          | 8     |             |                     |                                 |  |  |

|                  | GPI07          | 10    |             |                     |                                 |  |  |

|                  | GPIO9          | 11    |             |                     |                                 |  |  |

|                  | GPIO10         | 12    |             |                     |                                 |  |  |

|                  | GPIO11         | 13    |             |                     |                                 |  |  |

|                  | GPIO12         | 14    |             |                     |                                 |  |  |

| GPIO             | GPIO15         | 15    | I/O         | I/O                 | General-purpose input or output |  |  |

|                  | GPIO16         | 16    |             |                     |                                 |  |  |

|                  | GPIO17         | 19    |             |                     |                                 |  |  |

|                  | GPIO18         | 20    |             |                     |                                 |  |  |

|                  | GPIO19         | 21    |             |                     |                                 |  |  |

|                  | GPIO20         | 22    |             |                     |                                 |  |  |

|                  | GPIO21         | 23    |             |                     |                                 |  |  |

|                  | GPIO22         | 24    |             |                     |                                 |  |  |

|                  | GPIO23         | 26    |             |                     |                                 |  |  |

|                  | GPIO24         | 27    |             |                     |                                 |  |  |

|                  | GPIO27         | 32    |             |                     |                                 |  |  |

|                  | GPIO28         | 33    |             |                     |                                 |  |  |

|                  | Tubic C II II II            | 1                   | ,           | ipiioiai oigiiai    |                                                         |  |  |

|------------------|-----------------------------|---------------------|-------------|---------------------|---------------------------------------------------------|--|--|

| FUNCTION         | SIGNAL NAME                 | Pin<br>No.<br>QFN40 | PIN<br>TYPE | SIGNAL<br>DIRECTION | DESCRIPTION                                             |  |  |

|                  |                             | 11                  |             |                     |                                                         |  |  |

|                  | I2C0SCL                     | 23                  | I/O         | I/O                 | I <sup>2</sup> C clock                                  |  |  |

| I <sup>2</sup> C |                             | 32                  |             |                     |                                                         |  |  |

|                  |                             | 12                  |             |                     |                                                         |  |  |

|                  | I2C0SDA                     |                     | I/O         | I/O                 | I <sup>2</sup> C data                                   |  |  |

|                  |                             | 33                  |             |                     |                                                         |  |  |

|                  | I2S0MCLK                    | 16                  | I/O         | 0                   | I <sup>2</sup> S main clock                             |  |  |

|                  | I2S0SCLK                    | 6                   | I/O         | I/O                 | I <sup>2</sup> S serial clock                           |  |  |

|                  | 12000211                    | 19                  | .,,         | ., 0                | 1 C contai cicol                                        |  |  |

| l <sup>2</sup> S | 12S0WS                      | 10<br>20            | I/O         | I/O                 | I <sup>2</sup> S word select                            |  |  |

| 1-5              | I2S0SD0                     | 11<br>21            | I/O         | I/O                 | I <sup>2</sup> S serial data 0                          |  |  |

|                  | I2S0SD1                     | 12                  | I/O         | I/O                 | I <sup>2</sup> S serial data 1                          |  |  |

|                  | EXTCI                       | 16                  | I/O         | I                   | I <sup>2</sup> S external clock                         |  |  |

|                  | LRFD0                       | 19                  |             |                     | LRF digital output 0                                    |  |  |

|                  | LRFD1 LRFD2 F Digital LRFD3 |                     |             | 0                   | LRF digital output 1                                    |  |  |

|                  |                             |                     |             |                     | LRF digital output 2                                    |  |  |

| LRF Digital      |                             |                     | 1/0         |                     | LRF digital output 3                                    |  |  |

| Output           |                             |                     | I/O         |                     | LRF digital output 4                                    |  |  |

|                  | LRFD5                       | 24                  |             |                     | LRF digital output 5                                    |  |  |

|                  | LRFD6                       | 32                  |             |                     | LRF digital output 6                                    |  |  |

|                  | LRFD7                       | 33                  |             |                     | LRF digital output 7                                    |  |  |

|                  |                             | 1                   |             |                     |                                                         |  |  |

|                  | VDDR                        | 2                   | _           | _                   | Internal supply                                         |  |  |

|                  |                             | 34                  |             |                     |                                                         |  |  |

|                  |                             | 18                  |             |                     |                                                         |  |  |

|                  | VDDS                        | 29                  |             | _                   | 1.71V to 3.8V DIO supply                                |  |  |

| Power            | V555                        | 31<br>38            |             |                     | то со ото выруч                                         |  |  |

|                  | VDDD                        | 28                  | _           | _                   | For decoupling of internal 1.32V regulated core-supply. |  |  |

| V 000            |                             | 9                   |             | _                   |                                                         |  |  |

|                  | VDDIO                       | 17                  | _           | _                   | 1.71V to 3.8V split rail I/O supply                     |  |  |

|                  | DCDC                        | 30                  | _           | _                   | Switching node of internal DC/DC converter              |  |  |

| Reset            | RSTN                        | 25                  | _           | _                   | Global master device reset (active low)                 |  |  |

| RF               | ANT                         | 39                  | _           | _                   | 50-ohm RF port                                          |  |  |

| FUNCTION | SIGNAL NAME | Pin<br>No. | PIN<br>TYPE | SIGNAL<br>DIRECTION | DESCRIPTION                       |

|----------|-------------|------------|-------------|---------------------|-----------------------------------|

|          |             | QFN40      | IIFE        | DIRECTION           |                                   |

| SPI      | SPI0SCLK    | 6          | I/O         | I/O                 | SPI0 clock                        |

|          |             | 22         | 1/0         | 1/0                 |                                   |

|          | SPI0POCI    | 7          |             |                     | SPI0 peripheral out controller in |

|          |             | 8          | I/O         | I/O                 |                                   |

|          |             | 24         |             |                     |                                   |

|          | SPI0CSN     | 10         | I/O         | I/O                 | SPI0 chip-select                  |

|          |             | 21         | 1/0         | 1/0                 |                                   |

|          | SPI0PICO    | 7          |             |                     | SPI0 peripheral in controller out |

|          |             | 8          | I/O         | I/O                 |                                   |

|          |             | 23         |             |                     |                                   |

|          | SPI1SCLK    | 15         | I/O         | I/O                 | SPI1 clock                        |

|          | of Froder   | 27         | .,,         | .,, 0               | O. T. Glock                       |

|          |             | 13         |             |                     |                                   |

|          | SPI1POCI    | 14         | I/O         | I/O                 | SPI1 peripheral out controller in |

|          |             | 33         |             |                     |                                   |

|          | SPI1CSN     | 16         | I/O         | I/O                 | SPI1 chip select                  |

|          |             | 26         |             |                     | '                                 |

|          |             | 13         |             |                     |                                   |

|          | SPI1PICO    | 14         | I/O         | I/O                 | SPI1 peripheral in controller out |

|          |             | 32         |             |                     |                                   |

| SWD      | SWDIO       | 11         | I/O         | I/O                 | Serial wire data input/output     |

|          | SWDCK       | 12         | I/O         | I                   | Serial wire clock input           |

| Trace    | SWO         | 13         | I/O         | 0                   | Serial wire output                |

| FUNCTION                     | SIGNAL NAME | Pin<br>No.<br>QFN40 | PIN<br>TYPE | SIGNAL<br>DIRECTION | DESCRIPTION                                     |  |  |

|------------------------------|-------------|---------------------|-------------|---------------------|-------------------------------------------------|--|--|

|                              | T0C0        | 3<br>19<br>27       |             |                     | Capture input-0 / compare output-0 of Timer-0   |  |  |

|                              | T0C1        | 11<br>20            | I/O         | I/O                 | Capture input-1 / compare output-1 of Timer-0   |  |  |

|                              | T0C2        | 12<br>26            |             |                     | Capture input-2 / compare output-2 of Timer-0   |  |  |

|                              | T1C0        | 3<br>4<br>26        |             |                     | Capture input-0 / compare output-0 of Timer-1   |  |  |

|                              | T1C1        | 4<br>5              | I/O         | I/O                 | Capture input-1 / compare output-1 of Timer-1   |  |  |

| Timers - Capture/<br>Compare | T1C2        | 5<br>7              |             |                     | Capture input-2 / compare output-2 of Timer-1   |  |  |

|                              | T2C0        | 6                   |             |                     | Capture input-0 / compare output-0 of Timer-2   |  |  |

|                              | T2C1        | 8                   | I/O         | I/O                 | Capture input-1 / compare output-1 of Timer-2   |  |  |

|                              | T2C2        | 10                  |             |                     | Capture input-2 / compare output-2 of Timer-2   |  |  |

|                              | T3C0        | 13<br>16            |             |                     | Capture input-0 / compare output-0 of Timer-3   |  |  |

|                              | T3C1        | 15                  | I/O         | I/O                 | Capture input-1 / compare output-1 of Timer-3   |  |  |

|                              | T3C2        | 14<br>15            |             |                     | Capture input-2 / compare output-2 of Timer-3   |  |  |

|                              | TOCON       | 27                  |             | _                   | Complementary compare/PWM output-0 from Timer-0 |  |  |

|                              | T0C1N       | 32                  | I/O         | 0                   | Complementary compare/PWM output-1 from Timer-0 |  |  |

|                              | T0C2N       | 33                  |             |                     | Complementary compare/PWM output-2 from Timer-0 |  |  |

|                              | T1C0N       | 15                  |             | _                   | Complementary compare/PWM output-0 from Timer-1 |  |  |

|                              | T1C1N       | 23                  | I/O         | 0                   | Complementary compare/PWM output-1 from Timer-1 |  |  |

| Timers -                     | T1C2N       | 24                  |             |                     | Complementary compare/PWM output-2 from Timer-1 |  |  |

| Complementary Capture/PWM    | T2C0N       | 11                  |             |                     | Complementary compare/PWM output-0 from Timer-2 |  |  |

|                              | T2C1N       | 12                  | I/O         | 0                   | Complementary compare/PWM output-1 from Timer-2 |  |  |

|                              | T2C2N       | 14                  |             |                     | Complementary compare/PWM output-2 from Timer-2 |  |  |

|                              | T3C0N       | 3 33                | I/O         | 0                   | Complementary compare/PWM output-0 from Timer-3 |  |  |

|                              | T3C1N       | 8                   |             | _                   | Complementary compare/PWM output-1 from Timer-3 |  |  |

|                              | T3C2N       | 10                  |             |                     | Complementary compare/PWM output-2 from Timer-3 |  |  |

| Timers - Fault input         | T1F         | 3<br>13<br>16       | I/O         | I                   | Fault input for Timer-1                         |  |  |

| FUNCTION        | SIGNAL NAME | Pin<br>No.<br>QFN40 | PIN<br>TYPE | SIGNAL<br>DIRECTION | DESCRIPTION                            |  |  |  |

|-----------------|-------------|---------------------|-------------|---------------------|----------------------------------------|--|--|--|

|                 |             | 5                   |             |                     |                                        |  |  |  |

| Timers -        | T0PE        | 11                  | I/O         | 0                   | Prescaler event output from Timer-0    |  |  |  |

| Prescaler Event |             | 6                   |             |                     |                                        |  |  |  |

|                 | T2PE        | 12                  | I/O         | 0                   | Prescaler event output from Timer-2    |  |  |  |

|                 |             | 4                   |             |                     |                                        |  |  |  |

|                 | UART0TXD    | 21                  | I/O         | О                   | UART0 TX data                          |  |  |  |

|                 |             | 22                  |             |                     |                                        |  |  |  |

|                 |             | 5                   |             |                     |                                        |  |  |  |

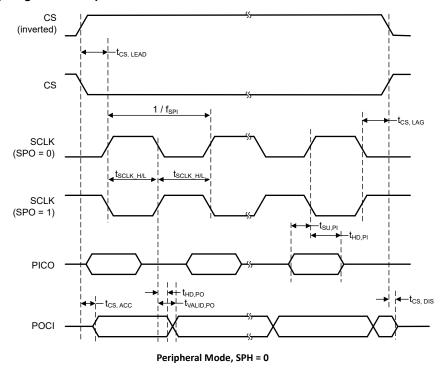

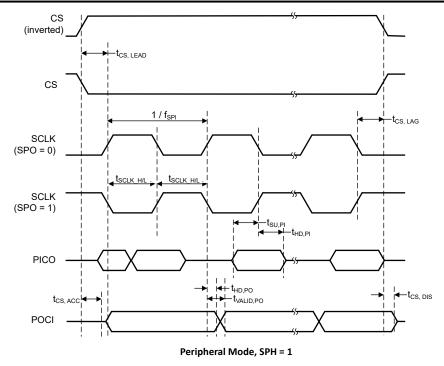

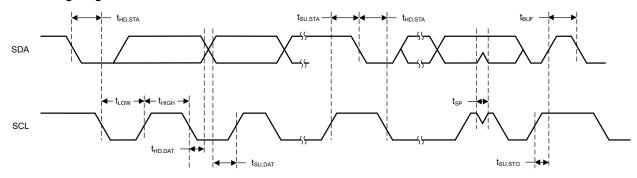

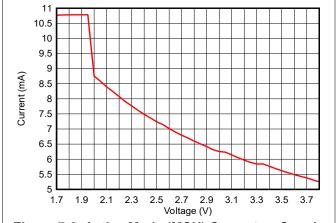

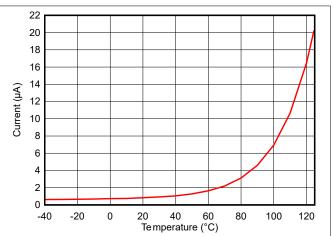

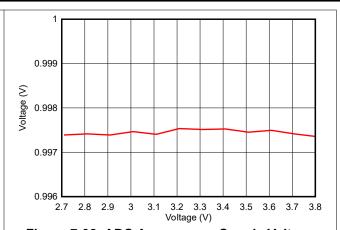

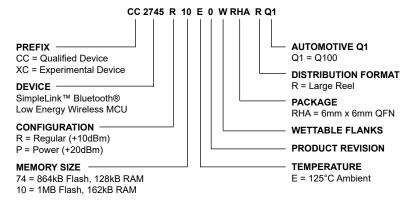

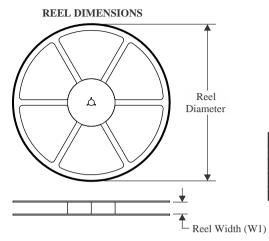

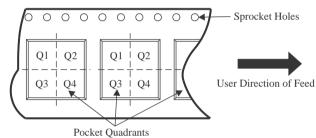

|                 | UART0RXD    | 21                  | I/O         | 1                   | UART0 RX data                          |  |  |  |