# BQ27Z746 Impedance Track™ Technology Battery Gas Gauge and Protection Solution for 1-Series Cell Li-Ion Battery Packs

### 1 Features

- Integrated battery gas gauge and protector

- Flash-programmable custom BQBMP RISC CPU

- SHA-256 authentication

- 400kHz I<sup>2</sup>C bus communications interface

- Low-voltage (2.0V) operation

- Two independent precision 16-bit ADCs

- Coulomb counting ADC with current sense resistor down to  $1m\Omega$

- Voltage ADC for cell voltage and external and internal temperature sensors

- Battery fuel gauging based on patented Impedance Track<sup>™</sup> technology

- Models battery discharge curve for accurate time-to-empty predictions

- Automatically adjusts for aging-, temperature-, and rate-induced effects on the battery

- Battery Kelvin sense differential analog output pins with built-in protection

- High-side or low-side current sensing

- Programmable hardware-based protection

- High-side FET gate drivers

- Overvoltage and undervoltage (OVP and UVP)

- Overcurrent in discharge and overcurrent in charge (OCD and OCC)

- Short circuit in discharge (SCD)

- Firmware-based overtemperature (OT)

- Reduced typical power modes

- SLEEP mode: 20µA

- SHIP mode: 10µA

- SHELF mode 5 μA

- SHUTDOWN mode: 0.2µA

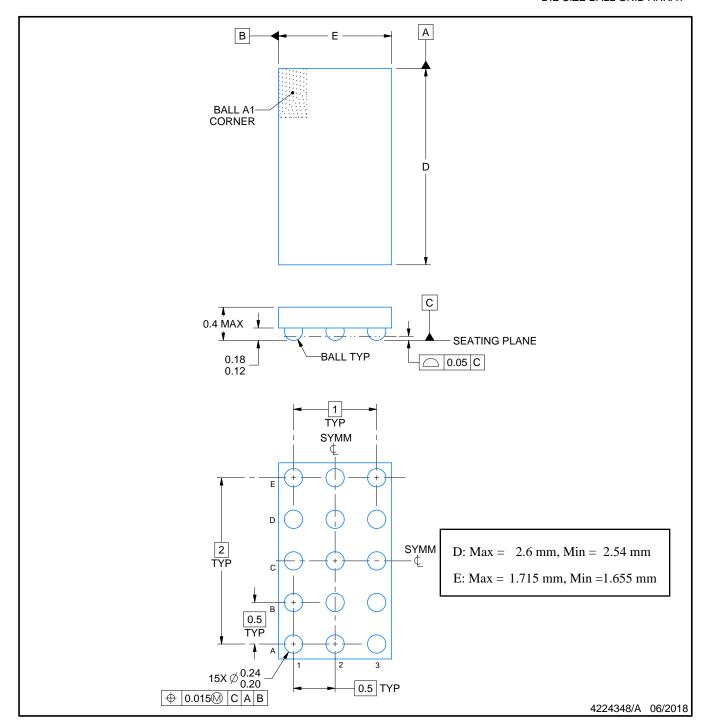

- Ultra-compact, 15-ball NanoFree™ DSBGA

## 2 Applications

- Any end equipment with 1-series rechargeable batteries:

- **Smartphones**

- **Tablets**

- Cameras

- Portable wearables/medical

- Industrial handhelds

## 3 Description

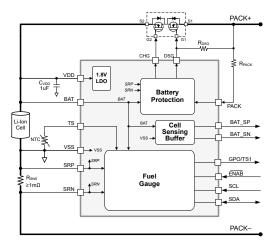

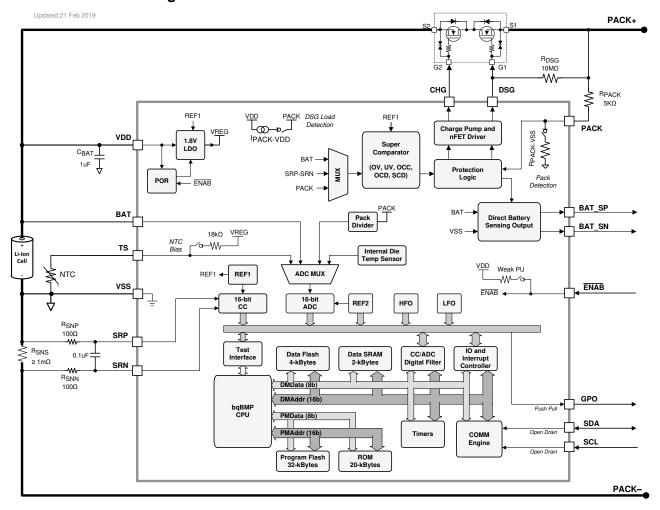

The Texas Instruments BQ27Z746 Impedance Track™ gas gauge solution is a highly integrated, accurate 1-series cell gas gauge and protection solution.

The BQ27Z746 device provides a fully integrated pack-based solution with a flash programmable custom reduced instruction-set CPU (RISC), safety protection, differential battery sensing analog output, and authentication for 1-series cell Li-ion and Lipolymer battery packs.

The BQ27Z746 gas gauge communicates through an I<sup>2</sup>C compatible interface and combines an ultralow power TI BQBMP processor, high accuracy analog measurement capabilities, integrated flash memory, N-CH high-side FET drive, and a SHA-2 Authentication transform responder into a complete, high-performance battery management solution.

#### **Package Information**

| PART NUMBER | PACKAGE (1) | BODY SIZE (NOM) |

|-------------|-------------|-----------------|

| BQ27Z746    | YAH (15)    | 1.69mm × 2.57mm |

For all available packages, see the orderable addendum at the end of the data sheet.

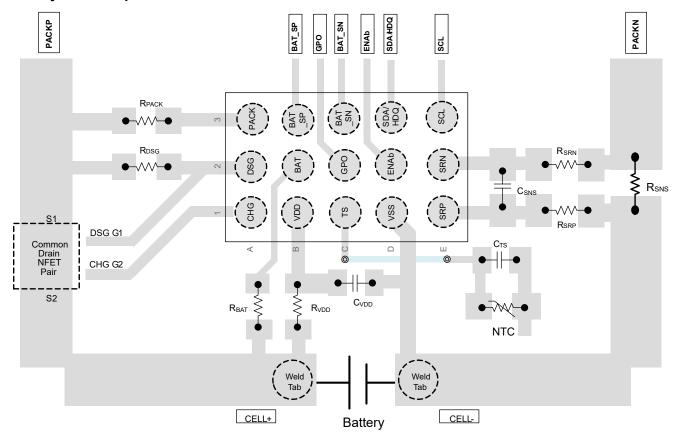

**BQ27Z746 Simplified Schematic**

# **Table of Contents**

| 1 Features                               | 7 Applications and Implementation22                      |

|------------------------------------------|----------------------------------------------------------|

| 2 Applications                           | 7.1 Application Information                              |

| 3 Description                            |                                                          |

| 4 Pin Configurations and Functions       |                                                          |

| 5 Specifications                         |                                                          |

| 5.1 Absolute Maximum Ratings             |                                                          |

| 5.2 ESD Ratings                          |                                                          |

| 5.3 Recommended Operating Conditions     |                                                          |

| 5.4 Thermal Information                  | 5 10.1 Third-Party Products Disclaimer28                 |

| 5.5 Electrical Characteristics           | 5 10.2 Documentation Support28                           |

| 5.6 Digital I/O: DC Characteristics1     | 2 10.3 Receiving Notification of Documentation Updates28 |

| 5.7 Digital I/O: Timing Characteristics1 |                                                          |

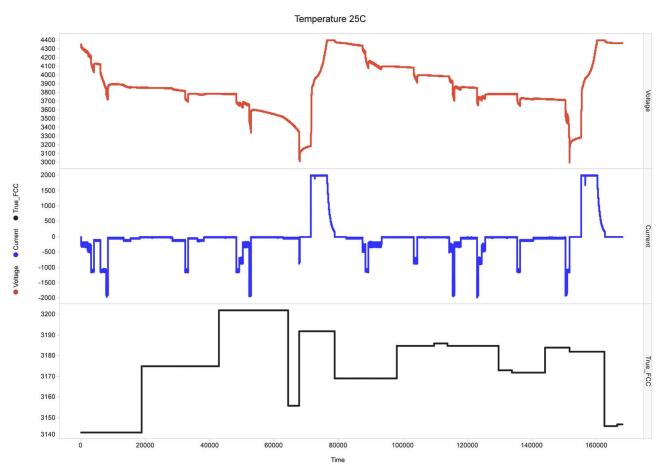

| 5.8 Typical Characteristics1             | 5 10.5 Trademarks28                                      |

| 6 Detailed Description1                  | 6 10.6 Electrostatic Discharge Caution28                 |

| 6.1 Overview1                            | 6 10.7 Glossary28                                        |

| 6.2 Functional Block Diagram1            | 6 11 Revision History29                                  |

| 6.3 Feature Description1                 | 7 12 Mechanical, Orderable, and Packaging                |

| 6.4 Device Functional Modes2             | 0 Information30                                          |

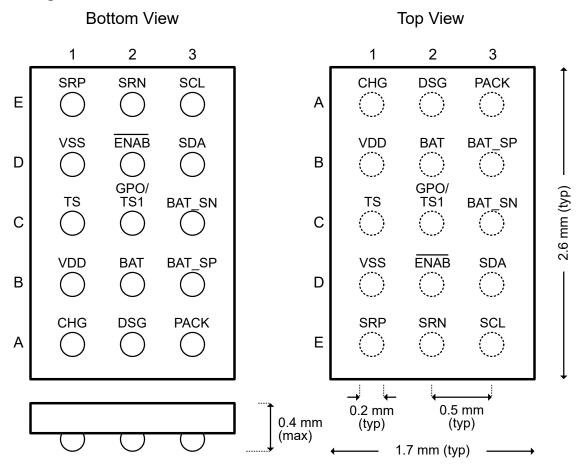

# **4 Pin Configurations and Functions**

Figure 4-1. Pinout Diagram

**Table 4-1. Pin Functions**

|         | PIN |                     | DESCRIPTION                                                                                                                                                                                |

|---------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                |

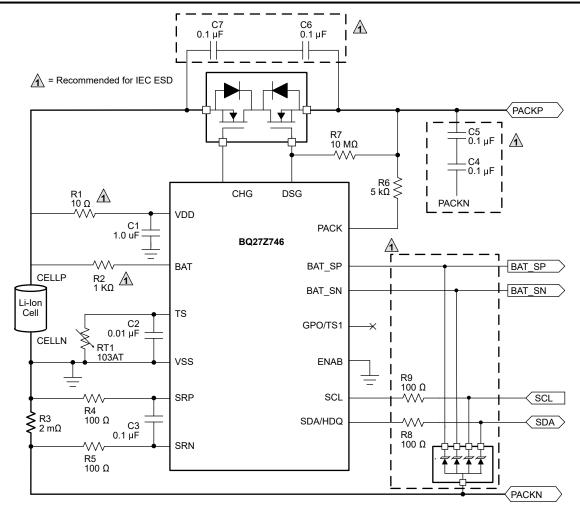

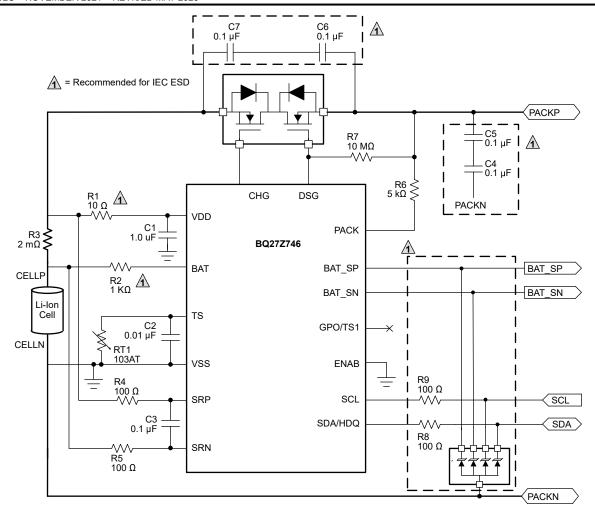

| CHG     | A1  | AO                  | Charge FET (CHG) driver                                                                                                                                                                    |

| DSG     | A2  | AO                  | Discharge FET (DSG) driver. Connect a series 10-M $\Omega$ typical resistor (R <sub>DSG</sub> ) between DSG pin and PACK+ positive terminal.                                               |

| PACK    | А3  | IA                  | Pack input voltage sensing pin. Connect a series 5-k $\Omega$ typical resistor (R <sub>PACK</sub> ) between PACK pin and PACK+ positive terminal.                                          |

| VDD     | B1  | Р                   | LDO regulator input. Connect a 1- $\mu$ F typical capacitor ( $C_{VDD}$ ) between VDD and VSS. Place the capacitor close to the gauge.                                                     |

| BAT     | B2  | IA                  | Battery voltage measurement sense input                                                                                                                                                    |

| BAT_SP  | В3  | OA                  | Cell sense output, positive                                                                                                                                                                |

| BAT_SN  | C3  | OA                  | Cell sense output, negative                                                                                                                                                                |

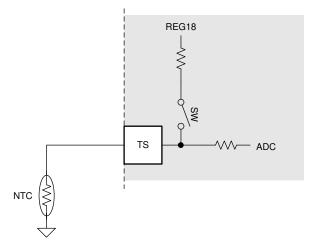

| TS      | C1  | IA                  | Thermistor input to ADC with internal 18-kΩ pullup resistor                                                                                                                                |

| GPO/TS1 | C2  | I/O                 | General purpose output. Optional TS1 ADC input channel with internal 18-kΩ pullup resistor                                                                                                 |

| VSS     | D1  | Р                   | Device ground                                                                                                                                                                              |

| ENAB    | D2  | I                   | Active low digital input with weak internal pullup to VDD. If enabled for ultra-low power SHIP mode, driving this signal to the PACK– negative terminal will enable the device to wake up. |

| SDA     | D3  | I/O                 | Digital input, open drain output for I <sup>2</sup> C serial data. Use with a typical 10-kΩ pullup resistor.                                                                               |

| SCL     | E3  | I/O                 | Digital input, open drain output for I <sup>2</sup> C serial clock. Use with a typical 10-kΩ pullup resistor.                                                                              |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

## Table 4-1. Pin Functions (continued)

|      | PIN |                     | DESCRIPTION                                                                                                                                                                     |

|------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                     |

| SRP  | E1  | IA                  | This is the positive analog input pin connected to the internal coulomb-counter peripheral for integrating a small voltage between SRP (positive side) and SRN (negative side). |

| SRN  | E2  | IA                  | This is the negative analog input pin connected to the internal coulomb-counter peripheral for integrating a small voltage between SRP (positive side) and SRN (negative side). |

(1) I/O = Digital input/output, IA = Analog input, AO= Analog output, P = Power connection

## 5 Specifications

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                |                                                                                                                                                                                              | MIN  | MAX                    | UNIT |  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|--|

| Supply voltage range                           | VDD                                                                                                                                                                                          | -0.3 | 6                      | V    |  |

|                                                | PACK (limited to 4 mA max)                                                                                                                                                                   | -0.3 | 8                      |      |  |

| Input voltage range                            | PACK+ external battery pack input terminal with 5 k $\Omega$ resistor in series to device PACK input pin                                                                                     | -0.3 | 24                     |      |  |

|                                                | PACK+ external battery pack input terminal with a 5 k $\Omega$ resistor (R <sub>PACK</sub> ) in series to device PACK pin and a 10 M $\Omega$ resistor (R <sub>DSG</sub> ) to device DSG pin | -12  | 24                     | V    |  |

|                                                | BAT                                                                                                                                                                                          | -0.3 | 6                      |      |  |

|                                                | SDA, SCL, ENAB                                                                                                                                                                               | -0.3 | 6                      |      |  |

|                                                | TS                                                                                                                                                                                           | -0.3 | 2                      |      |  |

|                                                | SRP, SRN                                                                                                                                                                                     | -0.3 | V <sub>BAT</sub> + 0.3 |      |  |

| Output voltage range                           | BAT_SP, BAT_SN                                                                                                                                                                               | -0.3 | 6                      | V    |  |

| Output voltage range                           | CHG, DSG                                                                                                                                                                                     | -0.3 | 12                     | v    |  |

| Operating junction temperature, T <sub>J</sub> |                                                                                                                                                                                              | -40  | 85                     | °C   |  |

| Storage temperature, T <sub>stg</sub>          |                                                                                                                                                                                              | -65  | 150                    | °C   |  |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

| V                  | Floatraatatia diaaharra | Human-body model (HBM) on all pins, per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM) on all pins, per ANSI/ESDA/<br>JEDEC JS-002 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

Submit Document Feedback

over operating free-air temperature range (unless otherwise noted)

|                      |     | MIN | NOM | MAX | UNIT |

|----------------------|-----|-----|-----|-----|------|

| Supply voltage range | /DD | 2.0 |     | 5.5 | V    |

## **5.3 Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                                                                 |                                                                                   | MIN                      | NOM MAX                             | UNIT |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|-------------------------------------|------|

|                                                                                 | PACK (with 5 kΩ R <sub>PACK</sub> current limit)                                  | 0                        | 12                                  |      |

| Input voltage range                                                             | PACK (no R <sub>PACK</sub> current limit)                                         | 0                        | 5.5                                 |      |

|                                                                                 | BAT                                                                               | 1.5                      | 5.5                                 | V    |

| range                                                                           | SDA, SCL, ENAB                                                                    | -0.3                     | VDD                                 | V    |

|                                                                                 | TS                                                                                | VSS                      | 1.8                                 |      |

|                                                                                 | SRN, SRP                                                                          | V <sub>CC_CM</sub> - 0.1 | V <sub>CC_CM</sub> + 0.1            |      |

|                                                                                 | BAT_SP, BAT_SN                                                                    | 2                        | VDD +V <sub>OFFS</sub>              |      |

| Output voltage                                                                  | GPO                                                                               | VSS                      | 1.8                                 | V    |

| range                                                                           | CHG, DSG                                                                          | VSS                      | VDD+ (VDD ×<br>A <sub>FETON</sub> ) | v    |

| External Decoup                                                                 | oling Capacitor on VDD pin, C <sub>VDD</sub>                                      | 1                        |                                     | μF   |

| External Decoup                                                                 | oling Capacitor on TS pin, C <sub>TS</sub>                                        |                          | 0.01                                | μF   |

| External Sense R <sub>PACK</sub>                                                | External Sense Resistor from PACK+ terminal to device PACK pin, R <sub>PACK</sub> |                          |                                     | kΩ   |

| External Sense Resistor from PACK+ terminal to device DSG pin, R <sub>DSG</sub> |                                                                                   | 10                       |                                     | МΩ   |

| External Sense                                                                  | Resistor from SRN to SRP pins, R <sub>SNS</sub>                                   | 1                        | 20                                  | mΩ   |

| Operating Temp                                                                  | erature, T <sub>A</sub>                                                           | -40                      | 85                                  | °C   |

### **5.4 Thermal Information**

Over-operating free-air temperature range (unless otherwise noted)

|                       | THERMAL METRIC <sup>(1)</sup>                | YAH (DSBGA) | UNIT |

|-----------------------|----------------------------------------------|-------------|------|

|                       | I HERMAL METRIC"                             | (15 PINS)   | UNII |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 70          |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 17          | 1    |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 20          | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1           | C/VV |

| ΨЈВ                   | Junction-to-board characterization parameter | 18          | 1    |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | NA          | 1    |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **5.5 Electrical Characteristics**

## 5.5.1 Supply Current

Unless otherwise noted, characteristics noted under conditions of  $T_A = -40$  to 85°C, no host communications, PROT On<sup>(1)</sup>,  $V_{CHG}$  and  $V_{DSG} > 5$  V,  $C_{LOAD} = 8$  nF (typical 20 nA), VDD = 4 V, Average current over 30 s with default firmware settings

| PARAMETER           | TEST CONDITIONS                                                                | MIN TYP | MAX | UNIT |

|---------------------|--------------------------------------------------------------------------------|---------|-----|------|

| I <sub>NORMAL</sub> | Standard operating conditions                                                  | 86      |     | μΑ   |

| I <sub>SLEEP</sub>  | Measured current ≤ sleep current threshold                                     | 20      |     | μΑ   |

| I <sub>SHIP</sub>   | V <sub>BAT</sub> = 3.0 V, Firmware SHIP mode enabled. 60 s average             | 10      |     | μΑ   |

| ISHELF              | V <sub>BAT</sub> = 3.0 V, Firmware SHELF mode enabled. PROT Off . 60 s average | 5       |     | μΑ   |

Copyright © 2025 Texas Instruments Incorporated

### 5.5.1 Supply Current (continued)

Unless otherwise noted, characteristics noted under conditions of  $T_A$  = -40 to 85°C, no host communications, PROT On<sup>(1)</sup>,  $V_{CHG}$  and  $V_{DSG}$  > 5 V,  $C_{LOAD}$  = 8 nF (typical 20 nA), VDD = 4 V, Average current over 30 s with default firmware settings

| PARAMETER         | TEST CONDITIONS                                                     | MIN | TYP | MAX | UNIT |

|-------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>SHUT</sub> | Firmware SHUTDOWN mode enabled OR $V_{BAT} \le V_{SHUT}$ , PROT Off |     | 0.2 | 1   | μΑ   |

<sup>(1)</sup> PROT On/Off. Protector block enabled with both DSG and CHG pins On or Off.

## 5.5.2 Common Analog (LDO, LFO, HFO, REF1, REF2, I-WAKE)

Unless otherwise noted, characteristics noted under conditions of  $T_A$  = -40 to 85°C

|                         | PARAMETER                                | TEST CONDITIONS                                                                                                                          | MIN   | TYP    | MAX   | UNIT   |

|-------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|--------|

| Internal 1.8-V L        | LDO (REG18)                              |                                                                                                                                          |       |        | -     |        |

| V <sub>REG18</sub>      | Regulator output voltage                 |                                                                                                                                          | 1.6   | 1.8    | 2.0   | V      |

| ΔV <sub>REG18TEMP</sub> | Regulator output change with temperature | $\Delta V_{BAT}/\Delta T_A$ , $I_{REG18} = 10 \text{ mA}$                                                                                | -1.2% |        | +1.2% |        |

| ΔV <sub>REG18LINE</sub> | Line regulation                          |                                                                                                                                          | -0.8% |        | 0.8%  |        |

| ΔV <sub>REG18LOAD</sub> | Load regulation                          | I <sub>REG18</sub> = 16 mA                                                                                                               | -1.5% |        | 1.5%  |        |

| I <sub>SHORT</sub>      | Short Circuit Current Limit              | V <sub>REG18</sub> = 0 V                                                                                                                 | 18    |        | 60    | mA     |

| PSRR <sub>REG18</sub>   | Power Supply Rejection Ratio             | $\Delta V_{BAT}/\Delta V_{REG18}$ , $I_{REG18}$ = 10 mA, $V_{BAT}$ > 2.5 V, f = 10 Hz                                                    |       | 50     |       | dB     |

| $V_{PORth}$             | POR threshold                            | Rising Threshold                                                                                                                         | 1.55  | 1.65   | 1.75  | V      |

| $V_{PORhy}$             | POR hysteresis                           |                                                                                                                                          |       | 0.1    |       | V      |

| V <sub>ENAB</sub>       | ENAB turn-on voltage for LDO (1)         | Active low falling threshold                                                                                                             |       |        | 0.4   | V      |

| R <sub>ENAB</sub>       | ENAB pin pullup resistance (1)           | Internal pull-up to VDD                                                                                                                  | 0.7   | 1      | 1.3   | МΩ     |

| Low Frequenc            | y Internal Oscillator (LFO)              |                                                                                                                                          |       |        | 1     |        |

| $f_{LFO}$               | LFO Operating frequency                  | Name of an austin a manda                                                                                                                |       | 65.536 |       | kHz    |

| f <sub>LFO(ERR)</sub>   | LFO Frequency error                      | Normal operating mode                                                                                                                    | -2.5% |        | +2.5% |        |

| f <sub>LFO32</sub>      | LFO operating frequency                  | Low power mode                                                                                                                           |       | 32.768 |       | kHz    |

| f <sub>LFO32(ERR)</sub> | LFO frequency error                      | Low power mode                                                                                                                           | -5%   |        | +5%   |        |

| High Frequenc           | cy Internal Oscillator (HFO)             |                                                                                                                                          |       |        |       |        |

| f <sub>HFO</sub>        | HFO operating frequency                  |                                                                                                                                          |       | 16.78  |       | MHz    |

| f                       | HFO frequency error                      | TA = -20°C to 70°C                                                                                                                       | -2.5% |        | 2.5%  |        |

| f <sub>HFO(ERR)</sub>   | The Onequency entor                      | TA = -40°C to 85°C                                                                                                                       | -3.5% |        | 3.5%  |        |

| t <sub>HFOSTART</sub>   | HFO start-up time                        | T <sub>A</sub> = -40°C to 85°C,<br>CLKCTL[HFRAMP] = 1, oscillator<br>frequency within +/- 3% of nominal<br>frequency or a power-on reset |       |        | 4     | ms     |

| Voltage Refere          | ence1 (VREF1)                            |                                                                                                                                          | -     |        |       |        |

| V <sub>REF1</sub>       | Internal reference voltage               | REF1 is for protection circuits, LDO,                                                                                                    | 1.195 | 1.21   | 1.227 | V      |

| V <sub>REF1_DRIFT</sub> | Internal Reference Voltage<br>Drift      | and CC                                                                                                                                   | -80   |        | +80   | PPM/°( |

| Voltage Refere          | ence2 (VREF2)                            |                                                                                                                                          |       |        | '     |        |

| V <sub>REF2</sub>       | Internal Reference Voltage               |                                                                                                                                          | 1.2   | 1.21   | 1.22  | V      |

| V <sub>REF2_DRIFT</sub> | Internal Reference Voltage<br>Drift      | REF2 is for the ADC                                                                                                                      | -20   |        | +20   | PPM/°  |

| Wake-Up Com             | parator (I-WAKE)                         | 1                                                                                                                                        |       | ,      |       |        |

## 5.5.2 Common Analog (LDO, LFO, HFO, REF1, REF2, I-WAKE) (continued)

Unless otherwise noted, characteristics noted under conditions of  $T_A$  = -40 to 85°C

|                       | PARAMETER                                                                                  | TEST CONDITIONS                                          | MIN   | TYP  | MAX   | UNIT |

|-----------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------|-------|------|-------|------|

| V <sub>WAKE</sub>     | Sense resistor voltage<br>threshold range to wake-up<br>gauge from low-power states<br>(2) | 500 μV step. Data Flash firmware default is 2 mV typical | -1.5  | -2.0 | -2.5  | mV   |

|                       | Effective wake-up current threshold range                                                  | Ideal R <sub>SNS</sub> = 1 mΩ                            | -1000 |      | -3000 | mA   |

| I <sub>WAKE</sub>     |                                                                                            | Ideal R <sub>SNS</sub> = 2 mΩ                            | -500  |      | -1500 |      |

|                       | an eenera range                                                                            | Ideal R <sub>SNS</sub> = 5 mΩ                            | -200  |      | -600  |      |

| V <sub>WAKE_ACC</sub> | Wake-up detection accuracy (2)                                                             |                                                          | -250  |      | 250   | μV   |

|                       | I-WAKE detection delay options (1)                                                         | Configurable with two delay options.                     | 9.6   | 12   | 14.4  |      |

| t <sub>WAKE</sub>     |                                                                                            | Data Flash firmware default is 12 ms typical             | 19.2  | 24   | 28.8  | ms   |

<sup>(1)</sup> Specified by design

### 5.5.3 Battery Protection (CHG, DSG)

Protection hardware circuits operating over free-air temperature range (unless otherwise noted)

|                          | PARAMETER                                                            | TEST CONDITIONS                                                                                      | MIN  | TYP     | MAX  | UNIT |

|--------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|---------|------|------|

| N-CH FET DR              | IVER, CHG AND DSG                                                    |                                                                                                      |      |         |      |      |

| V <sub>DRIVER</sub>      | Gate Driver Voltage, V <sub>CHG</sub> or V <sub>DSG</sub>            | C <sub>LOAD</sub> = 8 nF                                                                             | 2    | 2 × VDD |      | V    |

| A <sub>FETON</sub>       | FET driver gain factor, Vgs voltage to FET                           | A <sub>FETON</sub> = (V <sub>driver</sub> – VDD)/VDD,<br>C <sub>LOAD</sub> = 8 nF, UVP < VDD < 3.8 V | 0.9  | 1.0     | 1.2  | V/V  |

| V <sub>DSGOFF</sub>      | DSG FET driver off output voltage                                    | V <sub>DSGOFF</sub> = V <sub>DSG</sub> – PACK, C <sub>L</sub> = 8 nF                                 |      |         | 0.2  | V    |

| V <sub>CHGOFF</sub>      | CHG FET driver off output voltage                                    | V <sub>CHGOFF</sub> = V <sub>CHG</sub> – VSS , C <sub>L</sub> = 8 nF                                 |      |         | 0.2  | V    |

| t <sub>rise</sub>        | FET driver rise time (1)                                             | C <sub>L</sub> = 8 nF, (Vdriver – VDD)/VDD = 1x<br>V <sub>FETON</sub> changes from VDD to 2×VDD      |      | 400     | 800  | us   |

| t <sub>fall</sub>        | FET driver fall time (1)                                             | CL = 8 nF, V <sub>FETON</sub> changes from V <sub>FETMAX</sub> to V <sub>FETOFF</sub>                |      | 50      | 200  | us   |

| V <sub>FET_SHUT</sub>    | Firmware FET driver shut down voltage (2) (4)                        | Configurable with 1-mV steps —                                                                       | 2000 | 2100    | 5000 | mV   |

| V <sub>FET_SHUT_RE</sub> | Firmware FET driver shut down release (2) (4)                        |                                                                                                      | 2000 | 2300    | 5000 | mV   |

| I <sub>LOAD</sub>        | FET driver maximum loading                                           |                                                                                                      | -    |         | 10   | uA   |

| VOLTAGE PR               | OTECTION                                                             |                                                                                                      |      |         |      |      |

| V <sub>OVP</sub>         | Hardware overvoltage protection (OVP) detection range <sup>(3)</sup> | Recommended threshold range.                                                                         | 3500 |         | 5000 | mV   |

| OVI                      | Factory default trimmed threshold <sup>(3)</sup>                     | Factory trimmed in 50-mV steps                                                                       | 4525 |         |      |      |

|                          |                                                                      | TA = 25°C,<br>C <sub>LOAD</sub> at CHG/DSG < 1 μA                                                    | -15  |         | 15   | mV   |

| V <sub>OVP_ACC</sub>     | Hardware OVP detection accuracy (3)                                  | TA = 0°C to 60°C,<br>C <sub>LOAD</sub> at CHG/DSG < 1 μA                                             | -25  |         | 25   | mV   |

|                          |                                                                      | TA = $-40$ °C to 85°C,<br>C <sub>LOAD</sub> at CHG/DSG < 1 $\mu$ A                                   | -50  |         | 50   | mV   |

| V <sub>FW_OVP</sub>      | Firmware OVP detection range (4)                                     | Configurable with 1-mV steps                                                                         | 2000 | 4490    | 5000 | mV   |

| V <sub>FW_OVP_REL</sub>  | Firmware OVP release range (4)                                       | Comigurable with 1-my steps                                                                          | 2000 | 4290    | 5000 | mV   |

| V <sub>UVP</sub>         | Hardware undervoltage (UVP) detection range (3)                      | Recommended threshold range. Factory trimmed in 50-mV steps                                          | 2000 |         | 4000 | mV   |

|                          | Factory default trimmed threshold <sup>(3)</sup>                     | - Factory tillillied in 50-my steps                                                                  |      | 2300    |      |      |

<sup>(2)</sup> Data flash is configurable in FULL ACCESS mode and locked in SEALED. Accuracy is assured by factory trim at specified default threshold. A change in the factory threshold requires device calibration in the field.

## 5.5.3 Battery Protection (CHG, DSG) (continued)

Protection hardware circuits operating over free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                                                                 | TEST CONDITIONS                                           | MIN                 | TYP   | MAX                 | UNIT |

|-------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------|-------|---------------------|------|

|                         |                                                                                           | TA = 25°C,<br>C <sub>LOAD</sub> at CHG/DSG < 1 μA         | -20                 |       | 20                  | mV   |

| V <sub>UVP_ACC</sub>    | Hardware UVP detection accuracy (3)                                                       | TA = 0°C to 60°C,<br>C <sub>LOAD</sub> at CHG/DSG < 1uA   | -30                 |       | 30                  | mV   |

|                         |                                                                                           | TA = -40°C to 85°C,<br>C <sub>LOAD</sub> at CHG/DSG < 1uA | -50                 |       | 50                  | mV   |

| V <sub>FW_UVP</sub>     | Firmware UVP detection range (4)                                                          | Configurable with 4 m/ / store                            | 2000                | 2500  | 5000                |      |

| V <sub>FW_UVP_REL</sub> | Firmware UVP release range (4)                                                            | Configurable with 1 mV steps                              | 2000                | 2900  | 5000                | mV   |

| R <sub>PACK-VSS</sub>   | Resistance between PACK and VSS                                                           | SHUTDOWN mode only                                        | 100                 | 300   | 550                 | kΩ   |

| V <sub>RCP</sub>        | Reverse Charge Protection limit                                                           | −10V Continuous Operating, −12 V<br>ABS MAX               | -10                 |       |                     | V    |

| CURRENT PI              | ROTECTION                                                                                 |                                                           |                     |       |                     |      |

| V <sub>occ</sub>        | Sense voltage threshold range for Overcurrent in Charge (OCC) (3) (4)                     | Recommended threshold range.                              | 4                   |       | 100                 | mV   |

| 500                     | Factory default trimmed threshold <sup>(3)</sup>                                          | Factory trimmed in 1-mV steps                             |                     | 14    |                     |      |

| V <sub>OCC</sub>        | OCC 2-mV step design option                                                               | 2 mV step configuration option                            | 2                   |       | 256                 | mV   |

|                         |                                                                                           | Ideal R <sub>SNS</sub> = 1 mΩ                             | 4                   | 14    | 100                 |      |

| l <sub>occ</sub>        | Effective OCC current threshold range from V <sub>OCC</sub> (1) (4)                       | Ideal R <sub>SNS</sub> = 2 mΩ                             | 2                   | 7     | 50                  | Α    |

|                         | nom vocc ,                                                                                | Ideal R <sub>SNS</sub> = 5 mΩ                             | 0.8                 | 2.8   | 20                  |      |

| I <sub>FW_OCC</sub>     | Firmware OCC detection range (4)                                                          | Configurable with 1 mA steps                              | 0                   | 12000 | +I <sub>CC_IN</sub> | mA   |

| V <sub>OCD</sub>        | Sense voltage threshold range for Overcurrent in discharge (OCD) (3) (4)                  | Recommended threshold range.                              | -4                  |       | -100                | mV   |

|                         | Factory default trimmed threshold <sup>(3)</sup>                                          | Factory trimmed in 1-mV steps                             |                     | -16   |                     |      |

| V <sub>OCD</sub>        | OCD 2-mV step design option                                                               | ±2 mV step configuration option                           | -2                  |       | -256                | mV   |

|                         |                                                                                           | Ideal R <sub>SNS</sub> = 1 mΩ                             | -4                  | -16   | -100                | 0 A  |

| I <sub>OCD</sub>        | Effective OCD current threshold range from V <sub>OCD</sub> <sup>(1)</sup> <sup>(4)</sup> | Ideal R <sub>SNS</sub> = 2 mΩ                             | -2                  | -8    | -50                 |      |

|                         | v 0CD                                                                                     | Ideal R <sub>SNS</sub> = 5 mΩ                             | -0.8                | -3.2  | -20                 |      |

| I <sub>FW_OCD</sub>     | Firmware OCD detection range (4)                                                          | Configurable with 1-mA steps                              | -I <sub>CC_IN</sub> | -7000 | 0                   | mA   |

| $V_{SCD}$               | Sense voltage threshold range for Short circuit current in discharge (SCD) (3) (4)        | Threshold factory trimmed with 1-mV steps                 | -5                  |       | -120                | mV   |

|                         | Factory default trimmed threshold <sup>(3)</sup>                                          |                                                           |                     | -20   |                     |      |

|                         | E# 11 00D 111 1 1                                                                         | ldeal R <sub>SNS</sub> = 1 mΩ                             | <b>-</b> 5          | -20   | -120                |      |

| I <sub>SCD</sub>        | Effective SCD current threshold range from V <sub>SCD</sub> (1) (4)                       | Ideal R <sub>SNS</sub> = 2 m $\Omega$                     | -2.5                | -10   | -60                 | Α    |

|                         |                                                                                           | ldeal R <sub>SNS</sub> = 5 mΩ                             | -1                  | -4    | -24                 |      |

|                         |                                                                                           | <20 mV, TA = -25°C to 60°C                                | -2.1                |       | 2.1                 |      |

|                         | Oversurrent (OCC, OCD, CCD)                                                               | <20 mV                                                    | -2.1                |       | 2.1                 |      |

| $V_{OC\_ACC}$           | Overcurrent (OCC, OCD, SCD) detection accuracy (3)                                        | 20 mV-55 mV                                               | -3                  |       | 3                   | mV   |

|                         |                                                                                           | 56 mV-100 mV                                              | -5                  |       | 5                   |      |

|                         |                                                                                           | >100 mV                                                   | -12                 |       | 12                  |      |

| I <sub>PACK-VDD</sub>   | Current sink between PACK and VDD during current fault                                    | Load removal detection in firmware                        |                     | 15    |                     | μΑ   |

|                         | OCC fault release threshold                                                               | (/                                                        |                     | 100   |                     | mV   |

| OC_REL                  | OCD, SCD fault release threshold                                                          | (V <sub>PACK</sub> – V <sub>BAT</sub> )                   |                     | -400  |                     | mV   |

## 5.5.3 Battery Protection (CHG, DSG) (continued)

Protection hardware circuits operating over free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                | TEST CONDITIONS                                                                                        | MIN   | TYP  | MAX   | UNIT |

|-----------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| T <sub>OTC_TRIP</sub> | OTC 4 min /mala and 4 house health (2) (4)               |                                                                                                        | -40.0 | 55.0 | 150.0 | °C   |

| T <sub>OTC_REL</sub>  | OTC trip/release threshold (2) (4)                       |                                                                                                        | -40.0 | 50.0 | 150.0 | °C   |

| T <sub>OTD_TRIP</sub> |                                                          |                                                                                                        | -40.0 | 60.0 | 150.0 | °C   |

| T <sub>OTD_REL</sub>  | OTD trip/release threshold (2) (4)                       | Firmware-based and configurable in                                                                     | -40.0 | 55.0 | 150.0 | °C   |

| T <sub>UTC_TRIP</sub> | UTC trip/release threshold (2) (4)                       | 0.1°C steps                                                                                            | -40.0 | 0.0  | 150.0 | °C   |

| T <sub>UTC_REL</sub>  | OTC trip/release trireshold (=/ (*/                      |                                                                                                        | -40.0 | 5.0  | 150.0 | °C   |

| T <sub>UTD_TRIP</sub> | LITE 4 min (male and 4 household (2) (4)                 |                                                                                                        | -40.0 | 0.0  | 150.0 | °C   |

| T <sub>UTD_REL</sub>  | UTD trip/release threshold (2) (4)                       |                                                                                                        | -40.0 | 5.0  | 150.0 | °C   |

| PROTECTIO             | ON DELAY <sup>(1)</sup>                                  |                                                                                                        |       |      |       |      |

| t <sub>OVP</sub>      | OVP detection delay (debounce) options (1) (4)           | Configurable with 4095 delay options in 1.953-ms steps. Factory default = 1000 ms (512 counts) typical | 1.953 | 1000 | 7998  | ms   |

| t <sub>UVP</sub>      | UVP detection delay (debounce) options (1) (4)           | Configurable with 127-delay options in 1.953-ms steps. Factory default = 127 ms (65 counts) typical    | 1.953 | 127  | 248   | ms   |

| tocc                  | OCC detection delay (debounce) options (1) (4)           | Configurable with 31 delay options in 1.953-ms steps. Factory default = 7.8 ms (4 counts) typical      | 1.953 | 7.8  | 60.5  | ms   |

| t <sub>OCD</sub>      | OCD detection delay (debounce) options (1) (4)           | Configurable with 255 delay options in 0.244-ms steps. Factory default = 15.9 ms (65 counts) typical   | 0.244 | 15.9 | 62.3  | ms   |

| t <sub>SCD</sub>      | SCD detection delay (debounce) options (1) (4)           | Configurable with seven delay options in 122-µs steps. Factory default = 244-µs (2 counts) typical     | 122   | 244  | 854   | μs   |

| T <sub>OTC_DLY</sub>  | OTC trip delay <sup>(2) (4)</sup>                        | Circulate hand and application 1                                                                       | 0     | 2    | 255   | s    |

| T <sub>OTD_DLY</sub>  | OTD trip delay <sup>(2) (4)</sup>                        | Firmware-based and configurable in 1- s steps.                                                         | 0     | 2    | 255   | s    |

| T <sub>UTC_DLY</sub>  | UTC trip delay <sup>(2) (4)</sup>                        | The typical value is the data flash                                                                    | 0     | 2    | 255   | s    |

| T <sub>UTD_DLY</sub>  | UTD trip delay <sup>(2) (4)</sup>                        | factory default.                                                                                       | 0     | 2    | 255   | s    |

|                       | (LOW VOLTAGE) CHARGING                                   |                                                                                                        |       |      |       |      |

| V <sub>0CHGR</sub>    | Charger voltage requires to start zero-<br>volt charging | V <sub>PACK</sub> – VSS                                                                                | 1.6   |      |       | V    |

| V <sub>0INH</sub>     | Battery voltage that inhibits zero-volt charging         | VDD – VSS                                                                                              |       | 1.0  | 1.1   | V    |

- (1) Specified by design. Not production tested.

- (2) Firmware-based parameter. Not production tested.

- (3) Accuracy assured by factory trim at specified default threshold. A change from the default threshold requires device calibration in the field. Refer to the BQ27Z746 Technical Reference Manual.

- (4) Specified typical value is the factory default. Not production tested. The data flash configuration value can be changed in FULL ACCESS mode and is locked in SEALED mode. Refer to the BQ27Z746 Technical Reference Manual.

## 5.5.4 Cell Sensing Output (BAT\_SP, BAT\_SN)

Unless otherwise noted, characteristics noted under conditions of  $T_A = -40$  to 85°C

|                     | PARAMETER                            | TEST CONDITIONS                                                                   | MIN  | TYP  | MAX  | UNIT |  |

|---------------------|--------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|--|

| Static Response     |                                      |                                                                                   |      |      |      |      |  |

|                     |                                      | V <sub>BAT</sub> @ 1500 mV and 2400 mV DC,                                        | 1450 | 1500 | 1550 |      |  |

| V <sub>BUFACC</sub> | Buffer accuracy<br>(BAT_SP – BAT_SN) | PACK-BAT_SP ≥ 200 mV,<br>BAT_SP load: Hi-Z to 1 kΩ,<br>BAT_SN load: 1 kΩ to 10 kΩ | 2350 | 2400 | 2450 | mV   |  |

## 5.5.4 Cell Sensing Output (BAT\_SP, BAT\_SN) (continued)

Unless otherwise noted, characteristics noted under conditions of  $T_A$  = -40 to  $85^{\circ}C$

|                        | PARAMETER                                                   | TEST CONDITIONS                                                                                            | MIN  | TYP  | MAX  | UNIT  |

|------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|-------|

|                        |                                                             | 400-mV option, V <sub>BAT</sub> = 1.5 V to 2.5 V                                                           | 370  | 400  | 430  |       |

| .,                     | BAT SN common mode shift                                    | 200-mV option, V <sub>BAT</sub> = 2.0 V to 2.5 V                                                           | 170  | 200  | 230  |       |

| V <sub>BUFOFFS</sub>   | (BAT_SN – VSS)                                              | 0-mV option, V <sub>BAT</sub> = 2.0 V to 2.5 V                                                             | -30  | 0    | 30   | mV    |

|                        |                                                             | 600-mV option, V <sub>BAT</sub> = 2.0 to 2.5 V                                                             | 550  | 600  | 650  |       |

| ΔV <sub>BUF_LINE</sub> | Buffer line regulation                                      | V <sub>BAT</sub> = 1.5 to 2.5 V, no load, BAT_SP<br>- BAT_SN, V <sub>PACK</sub> - V <sub>BAT</sub> = 1.0 V |      | 10   |      | mV    |

| ΔV <sub>BUF_LOAD</sub> | Buffer load regulation                                      | V <sub>BAT</sub> = 2.4 V, load = 1 mA, BAT_SP –<br>BAT_SN, V <sub>PACK</sub> - V <sub>BAT</sub> = 1.0 V    |      | 1.2  |      | mV    |

| V <sub>RLOACC</sub>    | RLO mode accuracy<br>(BAT_SP – BAT_SN)                      | V <sub>BAT</sub> = 3000-mV to 5000-mV DC,                                                                  | -7   |      | +7   |       |

| V <sub>RLOACCP</sub>   | RLO mode accuracy<br>(BAT_SP – VSS)                         | For stability, 0-mV buffer option enabled BAT SP load: Hi-Z to 1 kΩ                                        | -5   |      | +5   | mV    |

| V <sub>RLOACCN</sub>   | RLO mode accuracy<br>(BAT_SN – VSS)                         | BAT_SN load: 1 kΩ to 10 kΩ                                                                                 | -5   |      | +5   |       |

| Russian                | BAT_SP low resistance                                       | 200-Ω option, DSG FET = ON                                                                                 | 160  | 200  | 260  | Ω     |

| R <sub>LO_SP</sub>     | mode                                                        | 510-Ω option, DSG FET = ON                                                                                 | 459  | 510  | 561  |       |

| P. a. a                | BAT_SN low resistance                                       | 200-Ω option, DSG FET = ON                                                                                 | 160  | 200  | 260  | 0     |

| R <sub>LO_SN</sub>     | mode                                                        | 510-Ω option, DSG FET = ON                                                                                 | 459  | 510  | 561  | Ω     |

| R <sub>HIZ_SP</sub>    | BAT_SP high impedance mode                                  | CHO EET - OEE                                                                                              | 0.6  | 1.0  | 1.3  | ΜΩ    |

| R <sub>HIZ_SN</sub>    | BAT_SN high impedance mode                                  | CHG FET = OFF                                                                                              | 0.6  | 1.0  | 1.3  | IVISZ |

| t <sub>BUF_OFF</sub>   | Buffer turn-off timing (1)                                  | Buffer disable timing respect to DSG FET turn-on                                                           |      | 500  |      | us    |

| C <sub>BUF_SP</sub>    | Max external capacitance for                                | BAT_SP to SRN (PACK-)                                                                                      |      |      | 150  | pF    |

| C <sub>BUF_SN</sub>    | stable operation (1)                                        | BAT_SN to SRN (PACK-)                                                                                      |      |      | 150  | þΓ    |

| B <sub>BUF_BW</sub>    | Buffer unity gain bandwidth                                 | Buffer enabled                                                                                             |      | 30   |      | kHz   |

| .,                     | BAT_SP – BAT +Fault (BCP)<br>Threshold Range <sup>(1)</sup> | Recommended threshold range.                                                                               | +100 |      | +250 |       |

| $V_{BCP}$              | Factory default trimmed threshold <sup>(3)</sup>            | Factory trimmed in ≈2-mV steps                                                                             |      | +200 |      | mV    |

| V <sub>BCP_ACC</sub>   | BAT_SP – BAT +Fault<br>Accuracy <sup>(3)</sup>              | RLO mode enabled,<br>Step size 10 mV                                                                       | -10  |      | +10  |       |

| V                      | BAT_SP – BAT –Fault (BDP)<br>Threshold Range <sup>(1)</sup> | Recommended threshold range.                                                                               | -250 |      | -100 |       |

| $V_{BDP}$              | Factory default trimmed threshold <sup>(3)</sup>            | Factory trimmed in ≈2-mV steps                                                                             |      | -200 |      | mV    |

| V <sub>BDP_ACC</sub>   | BAT_SP – BAT –Fault<br>Accuracy <sup>(3)</sup>              | RLO mode enabled,<br>Step size 10 mV                                                                       | -10  |      | +10  |       |

| Vnev                   | BAT_SN - VSS +Fault (BCN)<br>Threshold Range <sup>(1)</sup> | Recommended threshold range.                                                                               | +100 |      | +250 |       |

| $V_{BCN}$              | Factory default trimmed threshold <sup>(3)</sup>            | Factory trimmed in ≈2-mV steps                                                                             |      | +200 |      | mV    |

| V <sub>BCN_ACC</sub>   | BAT_SN – VSS +Fault<br>Accuracy <sup>(3)</sup>              | RLO mode enabled,<br>Step size 10 mV                                                                       | -10  |      | +10  |       |

## 5.5.4 Cell Sensing Output (BAT\_SP, BAT\_SN) (continued)

Unless otherwise noted, characteristics noted under conditions of  $T_A$  = -40 to 85°C

|                            | PARAMETER                                                   | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT |

|----------------------------|-------------------------------------------------------------|------------------------------------------------------------------|------|------|------|------|

| V                          | BAT_SN - VSS -Fault (BDN)<br>Threshold Range <sup>(1)</sup> | Recommended threshold range.                                     | -250 |      | -100 |      |

| V <sub>BDN</sub>           | Factory default trimmed threshold <sup>(3)</sup>            | Factory trimmed in ≈2-mV steps                                   |      | -200 |      | mV   |

| V <sub>BDN_ACC</sub>       | BAT_SN – VSS –Fault<br>Accuracy (3)                         | RLO mode enabled,<br>Step size 10 mV                             | -10  |      | +10  |      |

| t <sub>LO_FAULT_DLY</sub>  | BAT_SP / BAT_SN<br>fault comparator delay <sup>(1)</sup>    | 8-ms delay                                                       |      | 8    |      | ms   |

|                            |                                                             | 100-ms delay                                                     |      | 100  |      | ms   |

| t <sub>LO_FAULT_STRT</sub> | BAT_SP / BAT_SN<br>fault restart time (1) (2)               |                                                                  |      | 1000 |      | ms   |

| Transient Resp             | onse                                                        |                                                                  |      |      |      |      |

| V <sub>LOAD_SP</sub>       | BAT_SP load transient (1)                                   | No load ≥ 1 KΩ ≥ No load,                                        | -300 |      | 300  | mV   |

| V <sub>LOAD_SN</sub>       | BAT_SN load transient (1)                                   | Transition time 1 µs                                             | -200 |      | 200  | mV   |

| V <sub>LINE_SN</sub>       | BAT_SN line transient (1)                                   | VBAT = 1.5 V ≥ 2.4 V ≥ 1.5 V,<br>Transition slope 500 mV / 10 us | -30  |      | 30   | mV   |

| V <sub>TRANS</sub>         | (BAT_SP – BAT_SN)<br>transition transient <sup>(1)</sup>    | Firmware commanded transition from BUF mode to RLO mode          | -700 |      | 50   | mV   |

<sup>(1)</sup> Specified by Design. Not production tested.

## 5.5.5 Gauge Measurements (ADC, CC, Temperature)

Unless otherwise noted, characteristics noted under conditions of  $T_A = -40$  to  $85^{\circ}C$

|                       | PARAMETER                                   | TEST CONDITIONS                                             | MIN                     | TYP     | MAX                     | UNIT |  |

|-----------------------|---------------------------------------------|-------------------------------------------------------------|-------------------------|---------|-------------------------|------|--|

| Analog Digita         | al Converter (ADC)                          |                                                             |                         |         |                         |      |  |

| V <sub>BAT_RES</sub>  | Battery Voltage ADC<br>Resolution (bits)    | Signed data format, ±15 bits                                |                         | 16      |                         | bits |  |

| V <sub>BAT_FS</sub>   | Battery Measurement Full<br>Scale Range     |                                                             | -0.2                    |         | 5.5                     | V    |  |

| V                     | Battery Voltage ADC Error                   | T <sub>A</sub> = +25°C, V <sub>BAT</sub> = 4.0 VDC          |                         | ±1      |                         | mV   |  |

| V <sub>BAT_ERR</sub>  | Ballery Vollage ADC Ellor                   | V <sub>BAT</sub> = 2.5 to 5.0 VDC                           |                         | ±2      |                         | IIIV |  |

| R <sub>BAT</sub>      | Effective input resistance                  |                                                             | 8                       |         |                         | МΩ   |  |

| t <sub>BAT</sub>      | Battery Voltage Conversion Time             |                                                             |                         | 11.7    |                         | ms   |  |

| V <sub>ADC_RES</sub>  | Effective Resolution                        | V <sub>BAT</sub>                                            | 14                      | 15      |                         | bits |  |

| Coulomb Co            | unter (CC)                                  |                                                             |                         |         |                         |      |  |

| V <sub>CC_CM</sub>    | Common mode voltage range                   | V <sub>SS</sub> = 0V, 2V ≤ V <sub>BAT</sub> ≤ 5V            | V <sub>SS</sub>         |         | $V_{BAT}$               | V    |  |

| V <sub>CC_IN</sub>    | Input voltage range                         |                                                             | V <sub>CC_CM</sub> -0.1 |         | V <sub>CC_CM</sub> +0.1 | V    |  |

|                       |                                             | Ideal R <sub>SNS</sub> = 1 m $\Omega$ (16-bit data limited) |                         | +22 760 |                         |      |  |

| I <sub>CC_IN</sub>    | Effective input current sense range (1) (2) | Ideal R <sub>SNS</sub> = 2 m $\Omega$ (16-bit data limited) |                         | ±32,768 |                         | mA   |  |

|                       |                                             | Ideal R <sub>SNS</sub> = 5 mΩ                               |                         | ±20,000 |                         |      |  |

| t <sub>CC_CONV</sub>  | Conversion time                             | Single conversion                                           |                         | 1000    |                         | ms   |  |

| CC                    | Effective Resolution                        |                                                             |                         | 16      |                         | bits |  |

| CC <sub>ADC_RES</sub> | Ellective Resolution                        | 1 LSB = VREF1/10/(±2 <sup>15</sup> )                        |                         | ±3.7    |                         | μV   |  |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

<sup>(2)</sup> Firmware-based parameter. Not production tested.

<sup>(3)</sup> Accuracy assured by factory trim at specified default threshold. A change from the default threshold requires device calibration in the field. Refer to the BQ27Z746 Technical Reference Manual.

## 5.5.5 Gauge Measurements (ADC, CC, Temperature) (continued)

Unless otherwise noted, characteristics noted under conditions of  $T_A$  = -40 to 85°C

|                         | PARAMETER                                       | TEST CONDITIONS                                                           | MIN  | TYP  | MAX  | UNIT   |

|-------------------------|-------------------------------------------------|---------------------------------------------------------------------------|------|------|------|--------|

| 1                       | Effective current                               | Ideal R <sub>SNS</sub> = 1.0 m $\Omega$ , 10.0 A, T <sub>A</sub> = 25 °C  |      | 26   |      | mA     |

| I <sub>CC_ERR</sub>     | measurement error                               | Ideal R <sub>SNS</sub> = 1.0 m $\Omega$ , –10.0 A, T <sub>A</sub> = 25 °C |      | 29   |      | ША     |

| CC <sub>OSE</sub>       | Offset error                                    | 16- bit Post-Calibration                                                  | -2.6 | 1.3  | +2.6 | LSB    |

| CC <sub>OSE_DRIFT</sub> | Offset error drift                              | 15-bit + sign, Post Calibration                                           |      | 0.04 | 0.07 | LSB/°C |

| CC <sub>GE</sub>        | Gain Error                                      | 15-bit + sign, Over input voltage range                                   | -492 | 131  | +492 | LSB    |

| R <sub>CC_IN</sub>      | Effective input resistance                      |                                                                           | 7    |      |      | ΜΩ     |

| NTC Thermist            | or Measurement                                  |                                                                           |      |      |      |        |

| R <sub>NTC(PU)</sub>    | Internal Pullup Resistance                      | Factory Trimmed, Firmware compensated                                     | 14.4 | 18   | 21.6 | kΩ     |

| R <sub>NTC(DRIFT)</sub> | Resistance drift over temperature               | Firmware compensated                                                      | -250 | -120 | 0    | PPM/°C |

| В                       | External NTC Thermistor Temperature Measurement | Ideal 10KΩ 103AT NTC, TA = –10 to 70°C                                    | -2   | ±1   | +2   | °C     |

| R <sub>NTC_ERR</sub>    | Error with Linearization                        | Ideal 10KΩ 103AT NTC, TA = –40 to 85°C                                    | -3   | ±2   | +3   | C      |

| Internal Temp           | erature Sensor                                  |                                                                           |      |      |      |        |

| V <sub>(TEMP)</sub>     | Internal Temperature sensor voltage drift       | V <sub>TEMPP</sub>                                                        | 1.65 | 1.73 | 1.8  | mV/°C  |

| V <sub>(TEMP)</sub>     | Internal Temperature sensor voltage drift       | V <sub>TEMPP</sub> – V <sub>TEMPN</sub> (specified by design)             | 0.17 | 0.18 | 0.19 | mV/°C  |

Firmware-based parameter. Not production tested.

### 5.5.6 Flash Memory

Unless otherwise noted, characteristics noted under conditions of  $T_A$  = -40 to 85°C

|                          | PARAMETER               | TEST CONDITIONS    | MIN   | TYP | MAX | UNIT   |

|--------------------------|-------------------------|--------------------|-------|-----|-----|--------|

|                          | Data retention          |                    | 10    | 100 |     | Years  |

|                          | Flash programming write | Data Flash         | 20000 |     |     | Cycles |

|                          | cycles                  | Instruction Flash  | 1000  |     |     | Cycles |

| t <sub>(ROWPROG)</sub>   | Row programming time    |                    |       |     | 40  | μs     |

| t <sub>(MASSERASE)</sub> | Mass-erase time         | TA = -40°C to 85°C |       |     | 40  | ms     |

| t <sub>(PAGEERASE)</sub> | Page-erase time         | TA = -40°C to 85°C |       |     | 40  | ms     |

| I <sub>FLASHREAD</sub>   | Flash Read Current      | TA = -40°C to 85°C |       |     | 1   | mA     |

| I <sub>FLASHWRTIE</sub>  | Flash Write Current     | TA = -40°C to 85°C |       |     | 5   | mA     |

| I <sub>FLASHERASE</sub>  | Flash Erase Current     | TA = -40°C to 85°C |       |     | 15  | mA     |

## 5.6 Digital I/O: DC Characteristics

Unless otherwise noted, characteristics noted under conditions of  $T_A = -40$  to  $85^{\circ}C$ ,  $V_{REG18} = 1.8 \text{ V}$

|                                      | PARAMETER                   | TEST CONDITIONS                       | MIN  | TYP | MAX  | UNIT |  |  |

|--------------------------------------|-----------------------------|---------------------------------------|------|-----|------|------|--|--|

| I <sup>2</sup> C Pins (SCL, SDA/HDQ) |                             |                                       |      |     |      |      |  |  |

| V <sub>IH</sub>                      | High-level input voltage    | SCL, SDA pins                         | 1.26 |     |      | V    |  |  |

| V <sub>IL</sub>                      | Low-level input voltage low | SCL, SDA pins                         |      |     | 0.54 | V    |  |  |

| V <sub>OL</sub>                      | Low-level output voltage    | SCL, SDA pins, I <sub>OL</sub> = 1 mA |      |     | 0.36 | V    |  |  |

Limited by 16-bit twos-complement numeric format

# 5.6 Digital I/O: DC Characteristics (continued)

Unless otherwise noted, characteristics noted under conditions of  $T_A = -40$  to 85°C,  $V_{REG18} = 1.8 \text{ V}$

|                  | PARAMETER                   | TEST CONDITIONS                         | MIN  | TYP | MAX  | UNIT |

|------------------|-----------------------------|-----------------------------------------|------|-----|------|------|

| Cı               | Input capacitance           | SCL, SDA pins                           |      |     | 10   | pF   |

| I <sub>lkg</sub> | Input leakage current       | SCL, SDA pins                           |      | 1   |      | μA   |

| Push-P           | ull Pins (GPO)              | ·                                       |      |     |      |      |

| V <sub>IH</sub>  | High-level input voltage    | Push-Pull pins                          | 1.15 |     |      | V    |

| V <sub>IL</sub>  | Low-level input voltage low | Push-Pull pins                          |      |     | 0.54 | V    |

| V <sub>OH</sub>  | Output voltage high         | Push-Pull pins, I <sub>OH</sub> = -1 mA | 1.08 |     |      | V    |

| V <sub>OL</sub>  | Output voltage low          | Push-Pull pins, I <sub>OL</sub> = 1 mA  |      |     | 0.36 | V    |

| Cı               | Input capacitance           | Push-Pull pins                          |      |     | 10   | pF   |

| I <sub>lkg</sub> | Input leakage current       | Push-Pull pins                          |      | 1   |      | μΑ   |

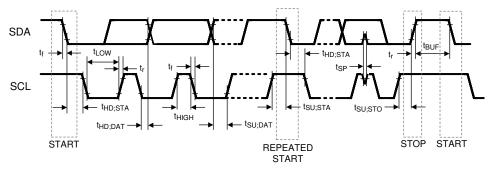

# 5.7 Digital I/O: Timing Characteristics

|                           | PARAMETER                    | TEST CONDITIONS      | MIN N | NOM MAX  | UNIT |  |

|---------------------------|------------------------------|----------------------|-------|----------|------|--|

| I <sup>2</sup> C Timing - | — 100 kHz                    |                      | -     | <u>'</u> |      |  |

| f <sub>SCL</sub>          | Clock Operating Frequency    | SCL duty cycle = 50% |       | 100      | kHz  |  |

| t <sub>HD:STA</sub>       | START Condition Hold Time    |                      | 4.0   |          | μs   |  |

| t <sub>LOW</sub>          | Low period of the SCL Clock  |                      | 4.7   |          | μs   |  |

| t <sub>HIGH</sub>         | High period of the SCL Clock |                      | 4.0   |          | μs   |  |

| t <sub>SU:STA</sub>       | Setup repeated START         |                      | 4.7   |          | μs   |  |

| t <sub>HD:DAT</sub>       | Data hold time (SDA input)   |                      | 0     |          | ns   |  |

| t <sub>SU:DAT</sub>       | Data setup time (SDA input)  |                      | 250   |          | ns   |  |

| t <sub>r</sub>            | Clock Rise Time              | 10% to 90%           |       | 1000     | ns   |  |

| t <sub>f</sub>            | Clock Fall Time              | 90% to 10%           |       | 300      | ns   |  |

| t <sub>SU:STO</sub>       | Setup time STOP Condition    |                      | 4.0   |          | μs   |  |

| t <sub>BUF</sub>          | Bus free time STOP to START  |                      | 4.7   |          | μs   |  |

| I2C Timing -              | — 400 kHz                    |                      |       | <u>'</u> |      |  |

| f <sub>SCL</sub>          | Clock Operating Frequency    | SCL duty cycle = 50% |       | 400      | kHz  |  |

| t <sub>HD:STA</sub>       | START Condition Hold Time    |                      | 0.6   |          | μs   |  |

| t <sub>LOW</sub>          | Low period of the SCL Clock  |                      | 1.3   |          | μs   |  |

| t <sub>HIGH</sub>         | High period of the SCL Clock |                      | 600   |          | ns   |  |

| t <sub>SU:STA</sub>       | Setup repeated START         |                      | 600   |          | ns   |  |

| t <sub>HD:DAT</sub>       | Data hold time (SDA input)   |                      | 0     |          | ns   |  |

| t <sub>SU:DAT</sub>       | Data setup time (SDA input)  |                      | 100   |          | ns   |  |

| t <sub>r</sub>            | Clock Rise Time              | 10% to 90%           |       | 300      | ns   |  |

| t <sub>f</sub>            | Clock Fall Time              | 90% to 10%           |       | 300      | ns   |  |

| t <sub>SU:STO</sub>       | Setup time STOP Condition    |                      | 0.6   |          | μs   |  |